-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

概览

简介

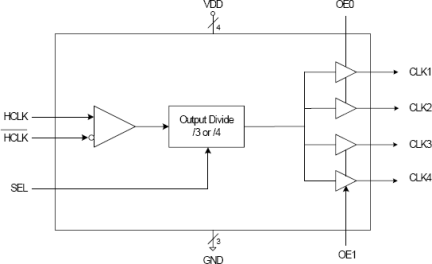

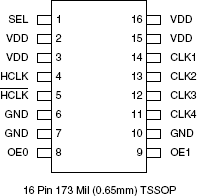

The 558-02 accepts a high-speed LVHSTL input and provides four CMOS low skew outputs from a selectable internal divider (divide by 3, divide by 4). The four outputs are split into two banks of two outputs. Each bank has a separate output enable to tri-state the output buffers. The 558-02 is a member of the ICS Clock BlocksTM family of clock generation, synchronization, and distribution devices.

特性

- 16-pin TSSOP package

- LVHSTL inputs

- Accepts up to 250 MHz input frequency

- Four low skew (<250 ps) outputs

- Selectable internal divider of 3 or 4

- Operating voltage of 3.3 V

产品对比

应用

文档

请登录后开启订阅

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 应用文档 | PDF 91 KB | |

| 应用文档 | PDF 1.99 MB | |

| 概览 | PDF 217 KB | |

| 应用文档 | PDF 322 KB | |

| 应用文档 | PDF 495 KB | |

| 应用文档 | PDF 442 KB | |

| 应用文档 | PDF 153 KB | |

| 应用文档 | PDF 565 KB | |

| 产品变更通告 | PDF 361 KB | |

9 items

|

||