概览

简介

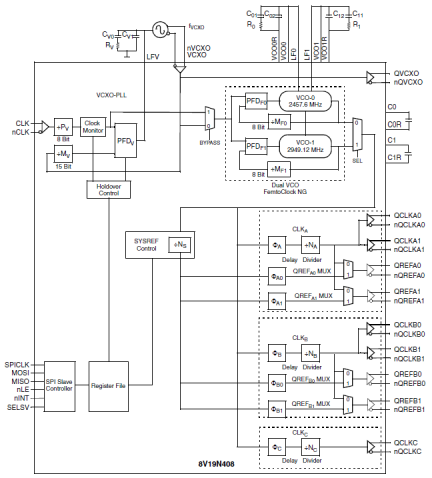

8V19N408 is a fully integrated FemtoClock® NG Jitter Attenuator and Clock Synthesizer. The device is a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards and is optimized to deliver excellent phase noise performance. The device supports JESD204B subclass 0 and 1 clock implementations. The device is very flexible in programming of the output frequency and phase. A two-stage PLL architecture supports both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for best possible phase noise characteristics.The second stage PLL lock on the VCXO-PLL output signal and synthesizes the target frequency. For flexibility, the second-stage PLL can use one of two VCOs at 2400MHz - 2500MHz (VCO-0) and 2920MHz - 3000MHz (VCO-1).

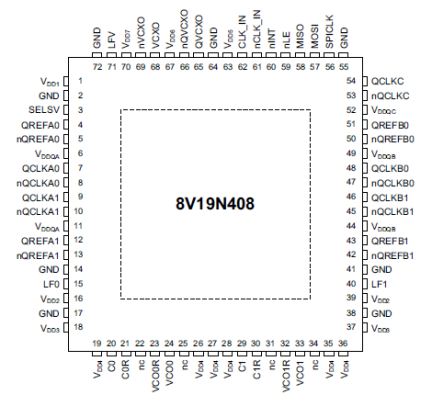

The device supports the clock generation of high-frequency clocks from the selected VCO and low-frequency system reference signals (SYSREF). The system reference signals are internally synchronized to the clock signals. Delay functions exist for achieving alignment and controlled phase delay between system reference and clock signals and to align/delay individual output signals. The input is monitored for activity. Short-term hold-over is provided to handle clock input failure scenarios. Auto-lock, individually programmable output frequency dividers and phase adjustment capabilities are added for flexibility. The device is configured through a 4-wire SP serial interface and reports lock and signal loss status in internal registers and optionally via lock detect (nINT) output. The device is packaged in a lead-free (RoHS 6) 72-lead VFQFN package. The extended temperature range supports wireless infrastructure, telecommunication and networking end equipment requirements. The device is a member of the high-performance clock family from IDT.

For information regarding evaluation boards and material, please contact your local IDT sales representative.

特性

- Core timing unit for JESD204B wireless infrastructure clocks

- First stage PLL uses an external VCXO for jitter attenuation

- Second PLL stage facilitates a dual integrated VCO for flexible frequency synthesis

- Integrated VCO frequencies: 2400MHz - 2500MHz (VCO-0) and 2920MHz - 3000MHz (VCO-1)

- Five differential configurable LVPECL, LVDS clock outputs with a variable output amplitude

- Four differential LVDS system reference (SYSREF) signal outputs

- Synchronization between clock and system reference signals

- Wide input frequency range supported by 8-bit pre- and 15-bit VCOX-PLL feedback divider

- Output clock frequencies: 2457.6MHz ÷N (VCO-0) and 2949.12MHz ÷N (VCO-1) in wireless infrastructure applications

- Three independent output clock frequency dividers N (range of ÷1 to ÷96)

- Clock output frequency range (VC0-0): (2400MHz - 2500MHz) ÷N

- Clock output frequency range (VC0-1): (2920MHz - 3000MHz) ÷N

- Phase delay capabilities for alignment/delay for clock and SYSREF signals

- Individual output phase adjustment (Clock): one-period of the selected VCO frequency in 64 steps

- Individual output phase adjustment (SYSREF): approximately half-period of the selected VCO frequency in 8 steps

- Internal, SPI controlled SYSREF pulse generation

- SYSREF frequencies: fVCO ÷ NS (10 dividers)

- NS divider range: ÷64 to ÷2048

- SYSREF (wireless infrastructure): 1.2MHz – 46.08MHz

- Clock input compatible with LVPECL, LVDS, LVCMOS signals

- Dedicated power-down features for reducing power consumption

- Input clock monitoring

- Holdover for temporary loss of input signal scenarios

- Support of output power-down and output disable

- Typical clock output phase noise at 614.4MHz:

1MHz offset: -149.4dBc/Hz - RMS phase noise (12kHz – 20MHz): 80.4fs (typical)

- Status conditions with programmable functionality for loss-of-lock and loss-of-reference indication

- Lock detect (nINT) output for status change indication

- 3.3V core and output supply mode

- -40°C to +85°C ambient operating temperature

- Lead-free (RoHS 6) 72-lead VFQFN packaging

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

视频和培训

新闻和博客

| 博客 | 2021年4月27日 | ||

| 博客 | 2018年4月27日 | ||

| 新闻 | 2017年12月18日 |