PCI Express® Jitter Attenuator

概览

简介

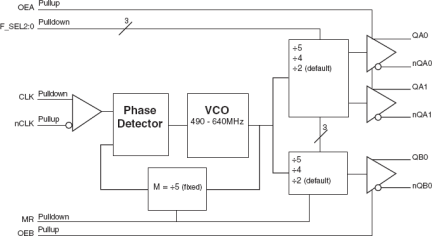

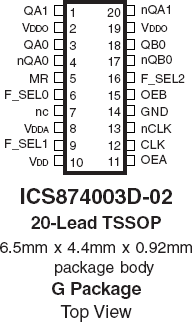

The 874003D-02 is a high performance Differential- to-LVDS Jitter Attenuator designed for use in PCI Express® systems. In some PCI Express® systems, such as those found in desktop PCs, the PCI Express® clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The 874003D-02 has a bandwidth of 2.1MHz. The 2.1MHz provides an intermediate bandwidth that can easily track triangular spread profiles, while providing good jitter attenuation. The 874003D-02 uses IDT's 3rd Generation FemtoClockTM PLL technology to achieve the lowest possible phase noise. The device is packaged in a 20 Lead TSSOP package, making it ideal for use in space constrained applications such as PCI Express® add-in cards.

特性

- Three Differential LVDS output pairs

- One Differential clock input

- CLK and nCLK supports the following input types: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Output frequency range: 98MHz - 320MHz

- Input frequency range: 98MHz - 128MHz

- VCO range: 490MHz - 640MHz

- Cycle-to-cycle jitter: 35ps (maximum)

- Supports PCI Express® Spread-Spectrum Clocking

- The 2.1MHz bandwidth mode allows the system designer to make jitter attenuation/tracking skew design trade-offs

- 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

产品对比

应用

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 466 KB | |

| 产品变更通告 | PDF 611 KB | |

| End Of Life Notice | PDF 161 KB | |

| 产品变更通告 | PDF 611 KB | |

| 产品变更通告 | PDF 596 KB | |

| 产品变更通告 | PDF 544 KB | |

| 产品变更通告 | PDF 95 KB | |

| 产品变更通告 | PDF 50 KB | |

8 items

|

||

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.