## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## SuperH RISC engine C/C++ Compiler Package APPLICATION NOTE: [Compiler Use guide] Option Guide

This document explains the compiler options available in version 9 of the SuperH RISC engine C/C++ compiler.

## Table of contents

| 1.    | Optimization Options                                                                    | 2  |

|-------|-----------------------------------------------------------------------------------------|----|

| 1.1   | Basic options (Optimize for speed, Optimize for size, Optimize for both speed and size) | 2  |

| 1.1.1 | Automatic inline expansion                                                              | 4  |

| 1.1.2 | Loop unroll                                                                             | 8  |

| 1.1.3 | Shift-operation expansion                                                               | 10 |

| 1.1.4 | Transfer-code expansion                                                                 | 12 |

| 1.1.5 | Method of division (microcomputer other than SH-1)                                      | 14 |

| 1.1.6 | Unaligned data transfer                                                                 |    |

| 1.1.7 | Expansion of constant loading instructions                                              | 18 |

| 1.2   | Advanced options for improving performance                                              | 20 |

| 1.2.1 | Specifies address range                                                                 | 20 |

| 1.2.2 | Disposition of variables                                                                | 21 |

| 1.2.3 | Optimized for access to external variables                                              | 24 |

| 1.2.4 | GBR Relative Logic Operation Generation                                                 | 27 |

| 1.2.5 | Division of optimizing ranges                                                           | 29 |

| 1.2.6 | MAC register                                                                            | 30 |

| 1.2.7 | Extension of return value                                                               | 32 |

| 1.2.8 | Enumeration data size                                                                   |    |

| 1.2.9 | Switch statement expansion method                                                       | 36 |

| 2.    | Useful Options                                                                          | 37 |

| 2.1   | Debugging Information Output Mode                                                       | 37 |

| 2.2   | Pre-processor expansion                                                                 | 39 |

| 2.3   | External variables handled as volatile                                                  | 41 |

| 2.4   | Vacant loop elimination                                                                 |    |

| 2.5   | Elimination of expression preceding infinite loop                                       | 44 |

| 2.6   | Switches the order of bit assignment                                                    | 46 |

| 2.7   | Specifies the boundary alignment value for structures, unions, and classes              | 47 |

| Websi | te and Support <website and="" support,ws=""></website>                                 | 48 |

## 1. Optimization Options

The compiler optimization options include three basic options (**Optimize for speed, Optimize for size, and, Optimize for both speed and size**) and advanced options, which are used to specify optimization settings in greater detail. Section 1.1 explains the basic options and the advanced options for each. Section 1.2 explains advanced options available for improving performance.

Note that the expanded assembly code examples in this document were obtained by specifying code=asmcode and cpu=sh2. This code might vary depending on the specification of the cpu option (H-1, SH-2, SH-2E, SH-3, or SH4). The code is also subject to change if the compiler is improved in the future. Accordingly, you should use these code examples for reference only.

## 1.1 Basic options (Optimize for speed, Optimize for size, Optimize for both speed and size)

The compiler performs two types of optimization: reduction of the object size and reduction of the execution time. If execution speed is the priority, specify the speed option. If size is the priority, specify the size option. If you want to balance speed and size, specify the nospeed option, which is the default.

The following explains these options:

speed option:

Performs optimization that reduces execution time but increases object size, as well as performing optimization that reduces both execution time and object size.

size option:

Performs optimization that reduces object size but increases execution time, as well as performing optimization that reduces both execution time object size.

nospeed option:

Performs optimization that reduces both execution time and object size.

In an ideal situation, the functions for which speed is the priority and the functions for which size is the priority are stored in separate files, so that the optimization type (speed first or size first) can be selected for each file.

Format:

SPeed SIze <u>NOSPeed</u>

Option settings in High-Performance Embedded Workshop (Renesas IDE hereafter):

| Configuration : C/C++ Toolchain Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SimDebug_SH-2       Category: Optimize         All Loaded Projects       Optimize         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construction of the state       Image: Construction of the state         Image: Construc |

Supplementary note:

The execution speed on production machines depends not only on the code generated by the compiler, but also on the memory architecture, the cache hit rate, interrupts, and other factors. Consequently, specifying the speed option might not always generate the fastest code. Make sure that you check the results of the options described in this document by executing them on production machines.

The defaults of some advanced compiler optimization options depend on the selected basic option. Table 1-1 lists the advanced options whose defaults depend on the selected basic option.

| No. | Functionality                                      | nospeed<br>(default)     | size                   | speed                    | See section |

|-----|----------------------------------------------------|--------------------------|------------------------|--------------------------|-------------|

| 1   | Automatic inline expansion                         | noinline                 | noinline               | Inline                   | 1.1.1       |

| 2   | Loop unroll                                        | noloop                   | noloop                 | loop                     | 1.1.2       |

| 3   | Shift-operation expansion                          | Instruction expansion    | Run-time routine call  | Instruction expansion    | 1.1.3       |

| 4   | Transfer-code expansion                            | Instruction<br>expansion | Run-time routine call  | Instruction<br>expansion | 1.1.4       |

| 5   | Method of division (microcomputer other than SH-1) | Instruction<br>expansion | Run-time routine call  | Instruction expansion    | 1.1.5       |

| 6   | Unaligned data transfer                            | Instruction expansion    | Run-time routine call  | Instruction expansion    | 1.1.6       |

| 7   | Expansion of constant loading instructions         | Literal data reference   | Literal data reference | Instruction<br>expansion | 1.1.7       |

| Table 1-1 Basic options | ("nospeed", | "size", and | "speed") | and default adv | anced options |

|-------------------------|-------------|-------------|----------|-----------------|---------------|

|-------------------------|-------------|-------------|----------|-----------------|---------------|

The following describes the advanced options listed above.

#### 1.1.1 Automatic inline expansion

Specifies whether to automatically perform inline expansion of functions.

When the inline option is specified, the compiler automatically performs inline expansion. The user is able to use inline=<*numeric-value*>, to specify the allowed increase in the program's size due to the use of inline expansion. For example, when inline=50 is specified, inline expansion will be applied until the program has grown to 150% of its size (gain of 50%).

The compiler performs automatic inline expansion by starting with the smallest of the called functions. Note that for the functions in which #pragma inline is specified, inline expansion is always performed regardless of the specification of the automatic inline expansion option. Also note that the upper limit on the size that the compiler uses for automatic inline expansion includes the increases in size resulting from inline expansion of #pragma inline.

When the noinline option is specified, automatic inline expansion is not performed.

Note that automatic inline expansion is not performed for the following functions:

- Functions that have variable parameters

- Functions that perform a call via the address of a function that will be expanded

For details about inline expansion, see 1.2 Performs inline expansion of functions in the manual SuperH RISC engine C/C++ Compiler Package APPLICATION NOTE: [Compiler Use guide] Extended Specifications.

Format:

## INLine [= *numeric-value*] : The default advanced option used when "speed" is selected. The default value is 20.

NOINLine : The default advanced option used when "size" or "nospeed" is selected.

| SuperH RISC engine Standard Toolcha | ain                                                                                                                                                                                                                                                                                                                                                                                                    | <u>? ×</u>                                                                                                                                                                                       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration :<br>SimDebug_SH-2    | C/C++ Toolchain Option<br>Category : Optimize<br>Optimize :<br>on<br>Speed or size :<br>Optimize for size<br>Generate file for inter-module<br>Optimization for access to<br>external variables :<br>None<br>Gbr relative operation :<br>Auto<br>Unaligned move :<br>Default<br>Options C/C++ :<br>-cpu=sh2 -object="\$(CONFIGDI<br>size -gbr=auto -macsave=0 -che<br>global_volatile=0 -opt_range=all | Switch statement :<br>Auto<br>Shift operation :<br>Default<br>Transfer code development :<br>Default<br>R)¥\$(FILELEAF).ob) <sup>"</sup> -debug -<br>sincpath -errorpath -<br>-infinite_loop=0 - |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                        | OK Cancel                                                                                                                                                                                        |

Figure 1-2

| <u>\</u> |                                       |                                           |

|----------|---------------------------------------|-------------------------------------------|

|          | Optimize details                      | <u>? ×</u>                                |

| V        | Inline Global variables Miscellaneous |                                           |

|          | Inline file path :                    |                                           |

|          |                                       | <u>A</u> dd                               |

|          |                                       | Remove                                    |

|          |                                       |                                           |

|          |                                       |                                           |

|          |                                       | Automatic inline expansion: Custom        |

|          | Automatic inline expansion : Custom   | Specification of maximum increase in size |

|          |                                       | as a percentage allowed in automatic      |

|          | Maximum : 20 =                        | inline expansion.                         |

|          |                                       |                                           |

|          | ОК                                    | Cancel                                    |

Figure 1-3

Inline expansion requires that the definitions of functions to be expanded can be referenced at compile time. Therefore, in normal inline expansion, only functions that are in the same file can be expanded. If it is necessary to expand functions located in different files, inter-file inline expansion options (file\_inline=file-name[,...]) must be specified. Note that if extern functions that have the same name are defined in multiple files that are specified for inter-file inline expansion, the compiler does not guarantee the result, since one of the function definitions is selected arbitrarily.

If the source file is specified for inline expansion, the compiler excludes the file from inline expansion and outputs the following warning message:

C1315 (W) File\_inline *file-name* ignored by same file as source file

Option settings in Renesas IDE:

In the SuperH RISC engine Standard Toolchain dialog box, on the C/C++ tab, select **Optimize** from the **Category** drop-down list, and click **Details** (Figure 1-2). In the displayed dialog box, shown below, specify the settings as follows.

| Optimize details                             | <u>? ×</u>     |                                   |

|----------------------------------------------|----------------|-----------------------------------|

| Inline Global variables Miscellaneous        |                |                                   |

| Inline file path :                           |                |                                   |

| \$(PROJDIR)¥b.c                              | <u>A</u> dd    | Ĺ                                 |

|                                              | <u>R</u> emove |                                   |

|                                              |                | Click this button to              |

|                                              |                | specify an inline expansion file. |

|                                              |                |                                   |

|                                              |                |                                   |

| Automatic inline <u>e</u> xpansion : Default |                |                                   |

| Maximum : 20 🚍                               |                |                                   |

|                                              |                |                                   |

| OK                                           | Cancel         |                                   |

Figure 1-4

#### Example:

| Source code                                                                                   |

|-----------------------------------------------------------------------------------------------|

| <a.c></a.c>                                                                                   |

| void func(void)                                                                               |

| {                                                                                             |

| <b>g</b> ();                                                                                  |

|                                                                                               |

| <pre>cb.c&gt;</pre>                                                                           |

| #pragma inline (g)                                                                            |

| void q(void)                                                                                  |

|                                                                                               |

| h();                                                                                          |

|                                                                                               |

|                                                                                               |

| file inline= <source a.c="" after="" b.c="" expanded="" image="" is="" specified="" when=""/> |

| void func(void)                                                                               |

| {                                                                                             |

| h();                                                                                          |

|                                                                                               |

|                                                                                               |

The file\_inline\_path option is useful when you specify files that are located in folders other than the current folder for inter-file inline expansion. If you specify the names of these folders beforehand in the file\_inline\_path=*path*-*name*[,...] format, you do not need to specify the path names of the target files.

The compiler searches the folders specified in the file\_inline\_path option for the target files, and then searches the current folder.

| SuperH RISC engine Standard Toolch | ain                                                                                                                                                                                  | <u>?</u> × |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| SuperH RISC engine Standard Toolch |                                                                                                                                                                                      |            |

|                                    | Options C/C++ :<br>-cpu=sh2 -file_inline_path="\$(PROJDIR)" -<br>object="\$(CONFIGDIR)¥\$(FILELEAF).obj" -debug -gbr=auto -<br>macsave=0 -chgincpath -errorpath -global_volatile=0 - |            |

|                                    | OK Cance                                                                                                                                                                             | 1          |

Figure 1-5

## 1.1.2 Loop unroll

Specifies whether to perform loop unrolling.

Specifying the loop option enables loop expansion optimization. For details about loop expansion optimization, see 4.1 *Reducing the number of times a loop is repeated* in the manual *SuperH RISC engine C/C++ Compiler Package APPLICATION NOTE: [Compiler use guide] Efficient programming techniquesCompiler.*

You can use the max\_unroll=*numeric-value* (*numeric-value*: 1-32) option to specify the maximum number of loop expansions. If loop expansion optimization is enabled, the option default is 2. If loop expansion optimization is disabled, the max\_unroll specification is ignored.

Format:

LOop : The default advanced option used when the basic option is "speed" is selected. The default value is 2.

NOLOop : The default advanced option used when the basic option is "size" or "nospeed" is specified.

| uperH RISC engine Standard Toolch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ? ×     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Configuration :<br>Dhry21  All Loaded Projects  All L | C/C++ Toolchain Option<br>Category: Other<br>Miscellaneous options:<br>Expand return value to 4 byte<br>Veloop unrolling<br>Approximate a floating-point constant division<br>Veloop unrolling<br>Ser defined options:<br>Iser defined options:<br>Iser defined options:<br>Copuesh2 - preinclude="\$(FILEDIR)*gregister.h" -<br>object="\$(CONFIGDIR)*\$(FILEDIR)*gregister.h" -<br>object="\$(CONFIGDIR)*\$(FILELEAF).obj" - debug -<br>listfile="\$(CONFIGDIR)*\$(FILELEAF).lst" -show=tab=4 - | speed V |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ОК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cancel  |

Figure 1-6

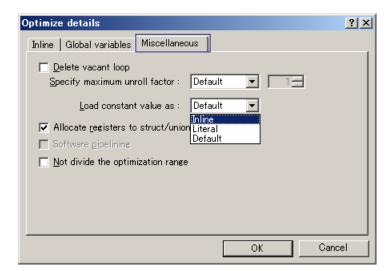

To specify the maximum number of loop expansions, click the **Compiler** tab in the SuperH RISC engine Standard Toolchain dialog box. Then select **Optimize** from the **Category** drop-down list, and click **Details** (Figure 1-2). In the displayed dialog box, shown below, specify the settings as follows.

| Optimize details                                                                                           | ? ×                                               |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Inline Global variables Miscellaneous                                                                      |                                                   |

| Delete vacant loop<br>Specify maximum unroll factor : Sustem I III<br>Load constant value as : Default III |                                                   |

| the numb                                                                                                   | <b>istom</b> is selected,<br>er of loop expansion |

| levels car                                                                                                 |                                                   |

| <u>N</u> ot divide the optimization range                                                                  |                                                   |

| OK                                                                                                         | Cancel                                            |

Figure 1-7

### 1.1.3 Shift-operation expansion

You can select whether shift operations are to be expanded into instructions or treated as run-time routine calls.

If inline (instruction expansion) is specified, shift operations are always expanded into instructions. If runtime (run-time routine call) is specified, the processing differs depending on the number of instructions into which the operation will be expanded. If the number of instructions will exceed 5, the operation is treated as a run-time routine call. If the number of instructions will not exceed 5, the operation is expanded into instructions.

Format:

#### SHIft = Inline : The default advanced option used when the basic option is "speed" or "nospeed". Runtime : The default advanced option used when the basic option is "size".

| SuperH RISC engine Standard Toolch | ain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>? ×</u> |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Configuration :<br>SimDebug_SH-2   | C/C++       Toolchain Option         Category:       Optimize         Optimize: <ul> <li>on</li> <li>generate</li> <li>generate</li> <li>file for inter-module optimization</li> <li>Optimize for size</li> <li>Generate file for inter-module optimization</li> <li>Optimization for access to</li> <li>external variables:</li> <li>Switch statement:</li> <li>None</li> <li>Auto</li> <li>Generation:</li> <li>Auto</li> <li>Generation:</li> <li>Auto</li> <li>Default</li> <li>Default</li> <li>Default</li> <li>Runtime</li> </ul> Options C/C++ :           Options C/C++ : <ul> <li>Cpu=sh2 -object="\$(CONFIGDIR)¥\$(FILELEAF).obj" -debug - size -gbr=auto -macsave=0 -chgincpath -errorpath - global_volatile=0 -opt_range=all -infinite_loop=0 -</li> </ul> |            |

|                                    | OK Canc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91         |

Figure 1-8

### Example:

| Source coo<br>int var;                  | de:                                  |                                                                                |                 |             |                                                                    |                            |                                |

|-----------------------------------------|--------------------------------------|--------------------------------------------------------------------------------|-----------------|-------------|--------------------------------------------------------------------|----------------------------|--------------------------------|

| <pre>void f(vo: {     var &gt;: }</pre> |                                      |                                                                                |                 |             |                                                                    |                            |                                |

|                                         | assembly co                          | de (shift=in                                                                   | line specified) |             | assembly co                                                        | de (shift=ru               | untime specified)              |

| _f:                                     | XTRCT<br>SHAR<br>SHAR<br>SHAR<br>RTS | L11+2,R5<br>@R5,R2<br>R2,R2<br>R2,R2<br>R2,R6<br>R6,R2<br>R2<br>R2<br>R2<br>R2 | ; var           | _f:<br>L11: | STS.L<br>MOV.L<br>JSR<br>MOV.L<br>LDS.L<br>RTS<br>MOV.L<br>.DATA.L | @R15+,PR<br>R0,@R5<br>_var | ;sta_sftrall<br>; var<br>; var |

| L11:                                    | MOV.L                                | R2,@R5                                                                         | ; var           |             | .DATA.L                                                            | sta_sftr                   | rall                           |

|                                         | .RES.W<br>.DATA.L                    | 1<br>_var                                                                      |                 |             |                                                                    |                            |                                |

## 1.1.4 Transfer-code expansion

You can select whether the transfer code of a structure, array, or class is expanded into instructions or treated as a run-time routine call.

If inline is specified, transfer code is always expanded into instructions. If runtime is specified, the processing differs depending on the number of instructions into which the code will be expanded. If the code can be copied with two pairs of load/stores (4 instructions), the code is expanded into instructions. If the code cannot be copied with two pairs of load/stores (4 instructions), the code is treated as a run-time routine call.

Format:

## BLOckcopy = Inline : The default advanced option used when the basic option is "speed" or "nospeed".

Runtime: The default advanced option used when the basic option is "size".

| perH RISC engine Standard Toolch | nain ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration :                  | C/C++ Toolchain Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SimDebug_SH-2                    | Category : Optimize         Optimize :         on <ul> <li>Details</li> <li>Speed or size :</li> <li>Optimize for size</li> <li>Generate file for inter-module optimization</li> <li>Optimization for access to         <ul> <li>generate file for inter-module optimization</li> <li>Optimization for access to             <ul> <li>generate file for inter-module optimization</li> <li>Optimize for size</li> <li>Generate file for inter-module optimization</li> <li>Optimization for access to                  <ul></ul></li></ul></li></ul></li></ul> |

Figure 1-9

Example:

| Source co | de:                               |                         |           |              |              |             |

|-----------|-----------------------------------|-------------------------|-----------|--------------|--------------|-------------|

| struct _S | T_ {                              |                         |           |              |              |             |

| char a    |                                   |                         | •         |              |              |             |

| } x;      |                                   |                         |           |              |              |             |

| ,         |                                   |                         |           |              |              |             |

| extern vo | id g(struct                       | ST );                   |           |              |              |             |

|           | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                         | :         |              |              |             |

| void f(vo | (bid)                             |                         |           |              |              |             |

| {         |                                   |                         |           |              |              |             |

| g(x);     |                                   |                         | •         |              |              |             |

| }         |                                   |                         |           |              |              |             |

| 1         |                                   |                         |           |              |              |             |

|           |                                   |                         | :         |              |              |             |

|           |                                   | e (blockcopy=inline     |           | assembly cod | le (blockcop | y=runtime   |

| specified | <u>)</u>                          |                         | specified | 1)           |              |             |

| _f:       |                                   |                         | _f:       |              |              |             |

|           | STS.L                             | PR,@-R15                | 1         | STS.L        | PR,@-R15     |             |

|           | ADD                               | #-8,R15                 |           | ADD          | #-8,R15      |             |

|           | MOV.L                             | L11+2,R6 ; _x           |           | MOV.L        | L11,R2       | ; _x        |

|           | MOV.L                             | L11+6,R4 ; _g           |           | MOV.L        | L11+4,R5     | ;slow_mvn   |

|           | MOV.B                             | @(1,R6),R0 ; (part of)x | :         | MOV          | R15,R1       |             |

|           | MOV.B                             | @R6,R1 ; (part of)x     |           | JSR          | @R5          |             |

|           | MOV.B                             | R0,@(1,R15)             |           | MOV          | #5,R0        | ; H'0000005 |

|           | MOV.B                             | @(2,R6),R0 ; (part of)x |           | MOV.L        | L11+8,R1     | ; _g        |

|           | MOV.B                             | R1,@R15                 |           | JSR          | @R1          |             |

|           | MOV.B                             | R0,@(2,R15)             | 1         | NOP          |              |             |

|           | MOV.B                             | @(3,R6),R0 ; (part of)x | :         | ADD          | #8,R15       |             |

|           | MOV.B                             | R0,@(3,R15)             |           | LDS.L        | @R15+,PR     |             |

|           | MOV.B                             | @(4,R6),R0 ; (part of)x | :         | RTS          |              |             |

|           | JSR                               | @R4                     | :         | NOP          |              |             |

|           | MOV.B                             | R0,@(4,R15)             | L11:      |              |              |             |

|           | ADD                               | #8,R15                  |           | .DATA.L      | _x           |             |

|           | LDS.L                             | @R15+,PR                |           | .DATA.L      |              |             |

|           | RTS                               |                         |           | .DATA.L      | _a _         |             |

|           | NOP                               |                         | •         |              | -            |             |

| L11:      |                                   |                         | ;         |              |              |             |

|           | .RES.W                            | 1                       |           |              |              |             |

|           | .DATA.L                           | _x                      |           |              |              |             |

|           | .DATA.L                           |                         | 1         |              |              |             |

|           |                                   |                         |           |              |              |             |

| L         |                                   |                         | •         |              |              |             |

## 1.1.5 Method of division (microcomputer other than SH-1)

You can select the method used for integer-type division and remainder calculation in the program. This option has no effect when the microcomputer is SH-1.

If division=cpu=inline is specified, constant division is converted to multiplication by inline expansion. Variable division is processed differently depending on the microcomputer type. If the microcomputer is SH-2A or SH2A-FPU, variable division is expanded into instructions. If the microcomputer is not SH-2A or SH2A-FPU, variable division is treated as a run-time routine call.

If division=cpu=runtime is specified, power-of-two constant division is expanded into instructions. Other types of constant division are processed differently depending on the microcomputer type. If the microcomputer is SH-2A or SH2A-FPU, the division operation is expanded into instructions. If the microcomputer is not SH-2A or SH2A-FPU, the division operation is treated as a run-time routine call.

Format:

DIvision = <u>Cpu</u> = Inline : The default advanced option used when the basic option is "speed" or "nospeed".

Runtime : The default advanced option used when the basic option is "size".

| SuperH RISC engine Standard Toolch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ain ?X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration :<br>SimDebug_SH-2   All Loaded Projects  C source file  C source file  C source file  Source  Sou | C/C++       Assembly       Link/Library       Standard Library       CPU       Deb • •         Category:       Object       Image: Comparison of the standard Library       CPU       Deb • •         Qutput file type :       Image: Comparison of the standard Library       Image: Comparison of the standard Library       Deb • •         Machine code (*.obj)       Image: Comparison of the standard Library       Image: Comparison of the standard Library       Details         Image: Comparison of the standard Library       Image: Comparison of the standard Library       Image: Comparison of the standard Library       Details         Image: Comparison of the standard Library       Image: Comparison of the standard Library       Image: Comparison of the standard Library       Details         Image: Comparison of the standard Library         Options C/C++ :       Image: Comparison of the standard Library       Image: Comparison o |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Figure 1-10

| Section :                                                       | T <u>e</u> mplate :    |

|-----------------------------------------------------------------|------------------------|

| Program section (P)                                             | Auto                   |

| P                                                               | Store string data in : |

| Division sub-options :                                          | Const section          |

| Default<br>Default<br>CPII/mine                                 |                        |

| CPU/inline<br>CPU/runtimeches<br>16/32byte boundaries :<br>None |                        |

Figure 1-11

Example:

Source code: int x; void f(int y) { x = y/3;} Expanded assembly code (division=cpu=inline Expanded assembly code (division=cpu=runtime specified) specified) \_f: \_f: MACL,@-R15 STS.L STS.L PR,@-R15 MACH,@-R15 MOV.L L11+2,R2 STS.L ; \_\_divls ; H'55555556 MOV.L L11,R1 MOV R4,R1 MOV.L L11+4,R5 ; \_x JSR @R2 ; H'0000003 DMULS.L R4,R1 MOV #3,R0 MACH,R6 L11+6,R5 STS MOV.L ; \_x R6,R0 MOV LDS.L @R15+,PR ROTL R0 RTS AND #1,R0 MOV.L R0,@R5 ; x ADD R0,R6 L11: .RES.W MOV.L R6,@R5 1 ; x \_\_\_divls LDS.L @R15+,MACH .DATA.L RTS .DATA.L \_x LDS.L @R15+,MACL L11: Н'55555556 .DATA.L .DATA.L \_x

### 1.1.6 Unaligned data transfer

You can select whether instruction expansion or a run-time routine call should be applied to the data transfer of a structure, union, or class whose alignment value is 1. If inline (instruction expansion) is specified, the transfer is always expanded into instructions. If runtime (run-time routine call) is specified, the transfer is expanded into instructions unless the number of instructions after the expansion would be large. If the number of instructions would be large after the expansion, the transfer is treated as a run-time routine call.

Format:

Unaligned = Inline : The default advan ced option used when the basic option is "speed" or "nospeed".

Runtime : The default advanced option used when the basic option is "size".

| SuperH RISC engine Standard Toolcha | ain <u>?</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ľ |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Configuration :<br>SimDebug_SH-2    | C/C++ Assembly Link/Library Standard Library CPU Deb<br>Category: Optimize<br>Optimize:<br>on<br>Speed or size:<br>Generate file for inter-module optimization<br>Optimization for access to<br>external variables:<br>None<br>Gbr relative operation:<br>Auto<br>Gbr relative operation:<br>Auto<br>Gbr relative operation:<br>Auto<br>Default<br>Unaligned move:<br>Transfer code development:<br>Default<br>Default<br>Default<br>Default<br>Default<br>Default<br>Default<br>Default<br>Default<br>Default<br>Transfer code development:<br>Default<br>Default<br>Options C/C++:<br>-cpu=sh2 -object="\$(CONFIGDIR)\#\$(FILELEAF).obj" -debug -<br>ebr=auto -macsave=0 -cheincpath -errorpath -global_volatile=0<br>-opt_range=all -infinite_loop=0 -del_vacant_loop=0 - |   |

|                                     | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

Figure 1-12

Example:

| Source c | ode:        |                         | :          |             |                         |

|----------|-------------|-------------------------|------------|-------------|-------------------------|

| #pragma  | pack 1      |                         | :          |             |                         |

| struct { |             |                         | -          |             |                         |

| char     | a;          |                         |            |             |                         |

| short    | b;          |                         | :          |             |                         |

| int      | c;          |                         | :          |             |                         |

| } x,y;   |             |                         | :          |             |                         |

| #pragma  | unpack      |                         | :          |             |                         |

|          | -           |                         | :          |             |                         |

| void fun | c(void)     |                         |            |             |                         |

| {        | . ,         |                         |            |             |                         |

| •        | = y.c;      |                         | :          |             |                         |

| }        | <b>.</b>    |                         | :          |             |                         |

| ,        |             |                         |            |             |                         |

|          |             |                         | :          |             |                         |

| Expanded | assembly co | de (unaligned=inline    | . Expanded | assembly co | ode (unaligned=runtime  |

| specifie |             |                         | specified  |             |                         |

| _func:   | <u>~/</u>   |                         | func:      | <u>a /</u>  |                         |

|          | MOV.L       | L11+2,R3 ; H'0000003+_y | ;          | STS.L       | PR,@-R15                |

|          | MOV.L       | L11+6,R7 ; H'0000003+ x | -          | MOV.L       | L11+2,R2 ; H'0000003+ y |

|          | MOV.B       | @R3,R4 ; y.c            |            | MOV.L       | L11+6,R1 ; H'0000003+ x |

|          | MOV.B       | @(1,R3),R0 ; y.c        | :          | MOV.L       | L11+10,R7 ;slow_mvn     |

|          | MOV.B       | R4,@R7 ; x.c            |            | JSR         | @R7                     |

|          | MOV.B       | R0,@(1,R7) ; x.c        |            | MOV         | #4,R0 ; H'0000004       |

|          | MOV.B       | @(2,R3),R0 ; y.c        | :          | LDS.L       | @R15+,PR                |

|          | MOV.B       | R0,@(2,R7) ; x.c        | 1          | RTS         | 01120 / 211             |

|          | MOV.B       | @(3,R3),R0 ; y.c        |            | NOP         |                         |

|          | RTS         | 0,0,10,,100,,10         | L11:       | 1.01        |                         |