# How to Make 1.2V LVCMOS from 1.8V LVCMOS Output

## 1. Introduction

LVCMOS logic simply toggles the output of its driver between ground level and VDD rail level. This means that the output amplitude or swing is a function of the VDD rail voltage. The common method for setting the LVCMOS amplitude is to apply the corresponding VDD rail voltage.

Most LVCMOS driver circuits have a certain VDD rail voltage range where requirements are met like output impedance and rise / fall times. When an amplitude is required that is below the low limit of the LVCMOS driver, there will be issues when simply lowering the VDD rail to this low voltage. Fortunately there are alternative methods to control the LVCMOS amplitude that allow amplitudes below the VDD rail low limit for the LVCMOS driver.

## 1.1 Typical LVCMOS Application

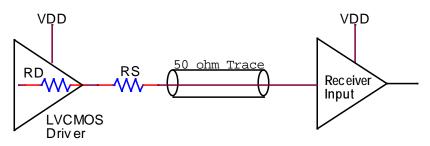

The typical LVCMOS driver to LVCMOS receiver input is as displayed in the following figure.

Figure 1. LVCMOS Clock Trace

RS is used to match the LVCMOS driver output impedance (RD) to the  $50\Omega$  clock trace. Renesas LVCMOS drivers are typically designed with  $17\Omega$  output impedance and need RS =  $33\Omega$  to match to a  $50\Omega$  clock trace. Some fan-out buffers (and for example, the FemtoClock 2 LVCMOS drivers) have a  $50\Omega$  output impedance in the driver so RS is not needed. For the LVCMOS driver output impedance, please check the relevant device datasheet.

This method of terminating a clock trace is called "Source Termination" because the clock trace is terminated at the source (driver) side only. The destination (receiver) side is a high impedance and is not terminated. Using this method, the full ground to VDD swing will appear at the receiver input. The signal integrity of the waveform at the receiver is good while at other places on the clock trace and at the driver side a reflection can be visible.

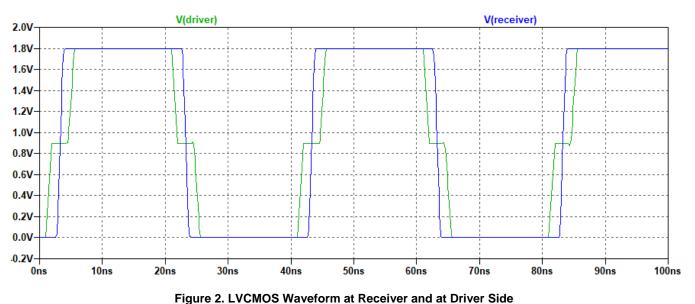

Below waveforms are from a simulation with a 25MHz 1.8V LVCMOS clock and a 10 inch or 25cm 50 $\Omega$  clock trace to a receiver input.

Reflections are visible at the driver side but cannot do any harm at that location. What is important is that the

waveform at the receiver input has good signal integrity.

### **1.2 Attenuating the LVCMOS Amplitude**

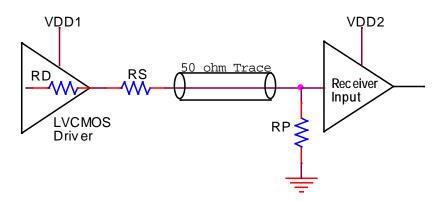

When, for example, the LVCMOS driver cannot operate below 1.8V but the receiver needs a 1.2V amplitude, the LVCMOS waveform needs to be attenuated. The simplest method is a resistor parallel to the receiver input.

Figure 3. Attenuating LVCMOS

Assuming that the LVCMOS amplitude at the driver is equal to VDD1 and the LVCMOS amplitude needed at the receiver input is VDD2, the formula for finding the parallel resistor RP value is as follows:

(EQ) 1 RP = 50 × VDD2 / (VDD1-VDD2)

Example: VDD1 = 1.8V and VDD2 =  $1.2V \rightarrow RP = 50 \times 1.2 / (1.8-1.2) = 100\Omega$

This formula also assumes a 50 $\Omega$  trace impedance and RD + RS = 50 $\Omega$  for proper matching to the clock trace.

The method works for any receiver amplitude below the driver amplitude. In addition to 1.2V LVCMOS, you can also make 1.5V LVCMOS or 1.0V LVCMOS or anything below the 1.8V driver levels by adjusting the RP resistor value.

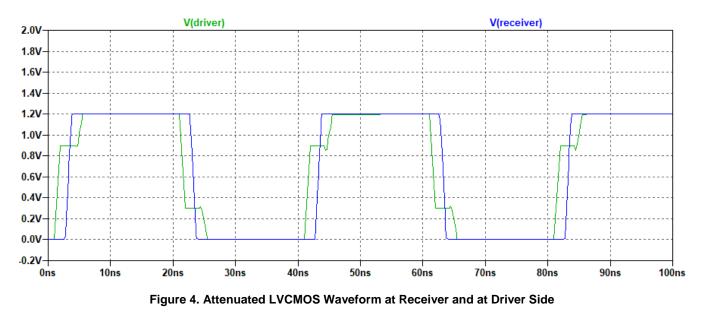

The following waveforms are from a simulation with a 25MHz 1.8V LVCMOS clock, a 10 inch or 25cm 50 $\Omega$  clock trace to a receiver input and 100 $\Omega$  parallel to the receiver input.

As predicted by the formula, the amplitude at the receiver input is now 1.2V and signal integrity is still good. The reflections that are visible at the driver side are no longer near the 50% level but can still not do any harm.

# 2. Measurements

### 2.1 Typical 1.8V LVCMOS

Keysight Infiniium : Monday, June 21, 2021 3:05:11 PM

Figure 5. Typical 1.8V LVCMOS 25MHz Waveform at Receiver Side

Measurements:

- Amplitude = 1.80V

- Frequency = 24.999992MHz

- Cycle-to-Cycle Jitter = 4.84ps RMS, 17.2ps peak

### 2.2 Adding 100Ω to 1.8V LVCMOS

Adding  $100\Omega$  parallel to the receiver input (in this case the Probe to the oscilloscope) to attenuate the waveform to 1.2V.

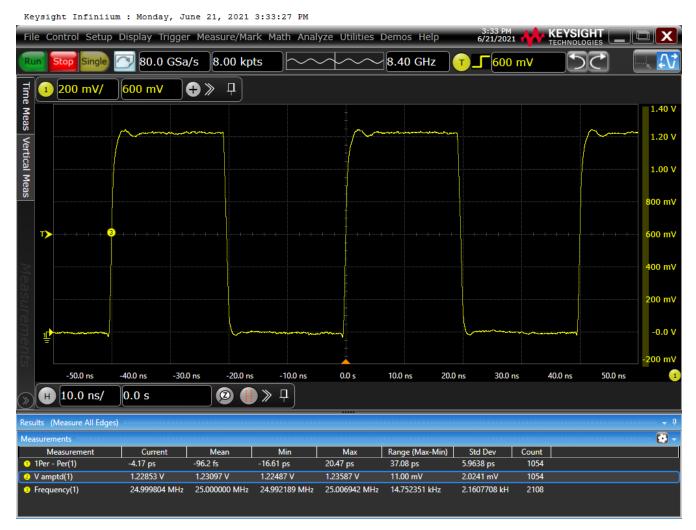

### Figure 6. 1.8V LVCMOS 25MHz with 100 $\Omega$ added at Receiver Side

The vertical scale for the measurement was adjusted to improve the jitter measurement.

Measurements:

- Amplitude = 1.23V

- Frequency = 25.00000MHz

- Cycle-to-Cycle Jitter = 5.96ps RMS, 20.5ps peak

The resistor parallel to the receiver input does a good job simply lowering the amplitude and not affect other properties of the clock with any significance.

The Cycle-to-Cycle Jitter ("1Per-Per" in the plot) looks a little bit higher because the smaller amplitude also makes the rising and falling edges slower in absolute volts per nanosecond, and as a result, this increases the noise floor of the oscilloscope. The jitter of the clock itself did not change: it is the noise contribution of the oscilloscope that changed. Besides that, the small LVCMOS amplitudes are mostly needed for micro-processor or "compute" applications where this jitter level is well within the requirements.

The frequency changed very little, only 0.3ppm in this case. This is also mostly due to the frequency measurement precision of an oscilloscope. This test was done with a Renesas Frequency Generator IC where

the isolation from the outputs to the crystal is very good. Clock oscillators with one output use much smaller chips where that isolation may be less good. When using this attenuation method with a clock oscillator, some frequency change can be expected.

# 3. Conclusion

Adding a single resistor parallel to the LVCMOS receiver input is an effective method to attenuate the LVCMOS amplitude when the VDD on the LVCMOS driver cannot be lowered enough to achieve the desired amplitude.

# 4. Revision History

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.0      | Jul 5, 2021 | Initial release. |

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.