概要

説明

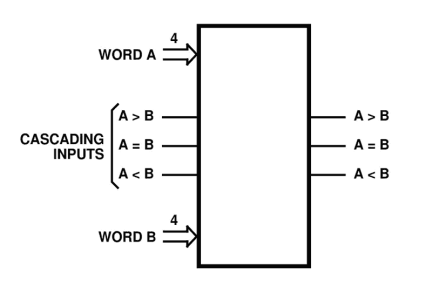

CD4063BMS is a 4-bit magnitude comparator designed for use in computer and logic applications that require the comparison of two 4-bit words. This logic circuit determines whether one 4-bit word (Binary or BCD) is less than, equal to, or greater than a second 4-bit word. The CD4063BMS has eight comparing inputs (A3, B3, through A0, B0), three outputs (A < B, A = B, A > B) and three cascading inputs (A < B, A = B, A > B) that permit systems designers to expand the comparator function to 8, 12, 16. . . 4N bits. When a single CD4063BMS is used, the cascading inputs are connected as follows: (A < B) = low, (A = B) = high, (A > B) = low. For words longer than 4 bits, CD4063BMS devices may be cascaded by connecting the outputs of the less significant comparator to the corresponding cascading inputs of the more significant comparator. Cascading inputs (A < B, A = B, and A > B) on the least significant comparator are connected to a low, a high, and a low level, respectively.

特長

- Electrically screened to DLA SMD 5962-96757

- High Voltage Type (20V Rating)

- Expansion to 8, 12, 16 4N Bits by Cascading Units

- Medium Speed Operation Compares Two 4-Bit Words in 250ns (Typ.) at 10V

- 100% Tested for Quiescent Current at 20V

- Standardized Symmetrical Output Characteristics

- 5V, 10V and 15V Parametric Ratings

- Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and +25°C

- Noise Margin (Full Package Temperature Range) 1V at VDD = 5V 2V at VDD = 10V 2.5V at VDD = 15V

- Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

アプリケーション

- Servo Motor Controls

- Process Controllers

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 79 KB | |

| カタログ | PDF 467 KB | |

| カタログ | PDF 4.85 MB | |

| Price Increase Notice | PDF 360 KB | |

| その他資料 | ||

| ホワイトペーパー | PDF 533 KB | |

| Product Advisory | PDF 499 KB | |

| 製品変更通知 | PDF 230 KB | |

| アプリケーションノート | PDF 338 KB | |

9 items

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。