-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

X28HC256

circleアクティブサンプル入手可能256K, 32K x 8 Bit; 5 Volt, Byte Alterable EEPROM

概要

説明

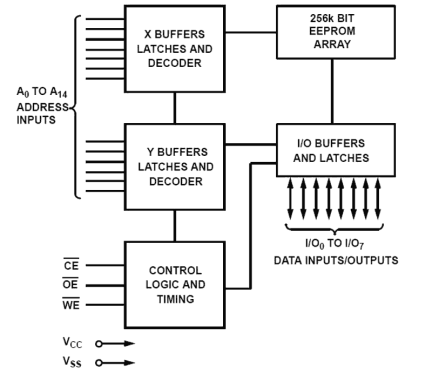

The X28HC256 is a second generation high performance CMOS 32k x 8 EEPROM. It is fabricated with Intersil’s proprietary, textured poly floating gate technology, providing a highly reliable 5V only nonvolatile memory. The X28HC256 supports a 128-byte page write operation, effectively providing a 24μs/byte write cycle, and enabling the entire memory to be typically rewritten in less than 0. 8s. The X28HC256 also features DATA polling and Toggle bit polling, two methods of providing early end of write detection. The X28HC256 also supports the JEDEC standard software data protection feature for protecting against inadvertent writes during power-up and power-down. Endurance for the X28HC256 is specified as a minimum 100, 000 write cycles per byte and an inherent data retention of 100 years

特長

- Access time: 90ns

- Simple byte and page write

- Single 5V supply

- No external high voltages or VP-P control circuits

- Self timed

- No erase before write

- No complex programming algorithms

- No overerase problem

- Low power CMOS

- Active: 60mA

- Standby: 500μA

- Software data protection

- Protects data against system level inadvertent writes

- High-Speed page write capability

- Highly reliable Direct Write™ cell

- Endurance: 100,000 cycles

- Data retention: 100 years

- Early end of write detection

- DATA polling

- Toggle bit polling

- RoHS compliant

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

Pkg. Type |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Price (USD) | 1ku |

ご購入 / サンプル |

|

|---|---|---|---|---|---|

| 型名 | |||||

X28HC256JIZ-12 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 35.08 | サンプルを入手, |

X28HC256JIZ-12T1 circleアクティブ |

PLCC | Reel | 3 | ||

X28HC256JIZ-15 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 34.91 | サンプルを入手, |

X28HC256JIZ-15T1 circleアクティブ |

PLCC | Reel | 3 | 33.64 | |

X28HC256JIZ-90 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 35.15 | サンプルを入手, |

X28HC256JIZ-90T1 circleアクティブ |

PLCC | Reel | 3 | 33.64 | |

X28HC256JZ-12 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 35.15 | サンプルを入手, |

X28HC256JZ-12T1 circleアクティブ |

PLCC | Reel | 3 | ||

X28HC256JZ-15 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 36.15 | サンプルを入手, |

X28HC256JZ-15T1 circleアクティブ |

PLCC | Reel | 3 | 33.64 | |

X28HC256JZ-90 circleアクティブ サンプル入手可能 |

PLCC | Tube | 3 | 42.31 | サンプルを入手, |

X28HC256JZ-90T1 circleアクティブ |

PLCC | Reel | 3 | ||

X28HC256PIZ-12 circleアクティブ サンプル入手可能 |

PDIP | Tube | Not Applicable | 55.56 | サンプルを入手, |

X28HC256PIZ-15 circleアクティブ サンプル入手可能 |

PDIP | Tube | Not Applicable | 33.35 | サンプルを入手, |

X28HC256PZ-12 circleアクティブ サンプル入手可能 |

PDIP | Tube | Not Applicable | サンプルを入手, |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product