Jitter Attenuator & FemtoClock NG® Multiplier

概要

説明

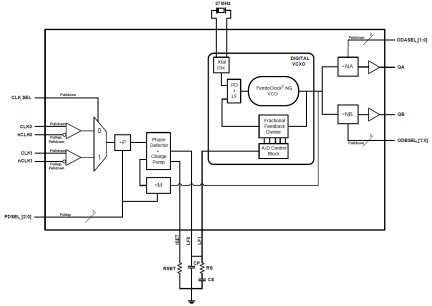

The 810N252I-02 device uses IDT's fourth generation FemtoClock® NG technology for optimal high clock frequency and low phase noise performance, combined with a low power consumption and high power supply noise rejection. The 810N252I-02 is a PLL based synchronous multiplier that is optimized for PDH or SONET to Ethernet clock jitter attenuation and frequency translation.

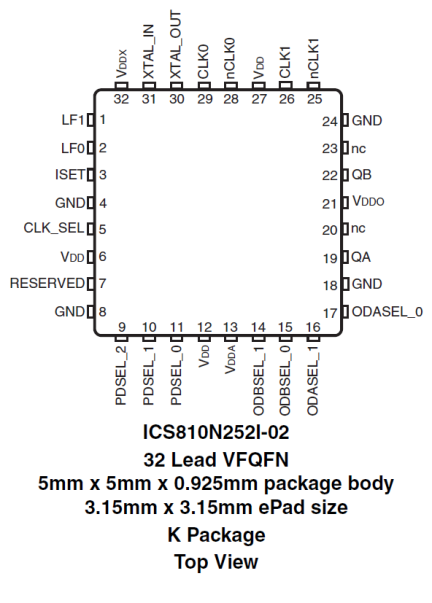

The 810N252I-02 contains two internal frequency multiplication stages that are cascaded in series. The first stage is a jitter attenuator, capable of jitter attenuation down to 10Hz using the external loop filter. The second stage is a FemtoClock NG® frequency multiplier that provides the low jitter, high frequency Ethernet output clock that easily meets Gigabit and 10 Gigabit Ethernet jitter requirements. Pre-divider and output divider multiplication ratios are selected using device selection control pins. The multiplication ratios are optimized to support most common clock rates used in PDH, SONET and Ethernet applications. The device requires the use of an external, inexpensive fundamental mode 27MHz crystal. The device is packaged in a space-saving 32-VFQFN package and supports industrial temperature range.

特長

- Fourth generation FemtoClock® NG technology

- Two single-ended LVCMOS/LVTTL outputs

- Each output supports independent frequency selection at 25MHz, 125MHz, 156.25MHz and 312.5MHz

- Two differential inputs support the following input types: LVPECL, LVDS, LVHSTL, HCSL

- Accepts input frequencies from 8kHz to 155.52MHz including 8kHz, 1.544MHz, 2.048MHz, 19.44MHz, 25MHz, 77.76MHz, 125MHz and 155.52MHz

- Crystal interface designed for a 27MHz crystal

- Attenuates the phase jitter of the input clock by using a low-cost fundamental mode crystal

- Customized settings for jitter attenuation and reference tracking using an external loop filter connection

- FemtoClock NG frequency multiplier provides low jitter, high frequency output

- Absolute pull range: ±50ppm

- Power supply noise ratio (PSNR): -85dB

- FemtoClock NG VCO frequency: 625MHz

- RMS phase jitter @ 125MHz, using a 27MHz crystal (12kHz – 20MHz): 0.67ps (typical)

- 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。