-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

MC100ES6014

circle廃止品2.5V/3.3V,1:5 Differential ECL/PECL/HSTL/LVDS Clock Driver

warning以下のデバイスを代替品として推奨しております。

ページセクションへ移動:

arrow_drop_down

概要

説明

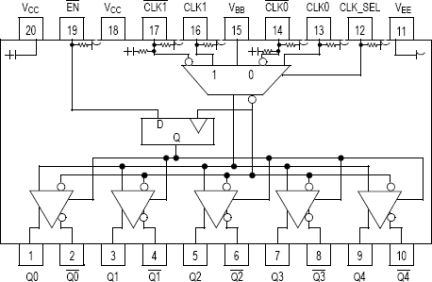

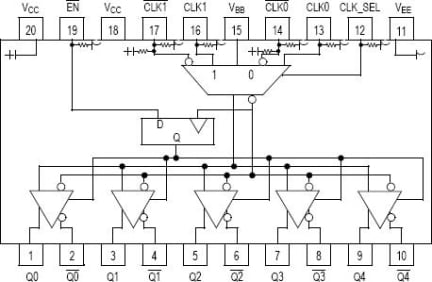

The MC100ES6014 is a low skew 1-to-5 differential driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The ECL/PECL input signals can be either differential or single-ended (if the VBB output is used). HSTL and LVDS inputs can be used when the ES6014 is operating under PECL conditions. The ES6014 specifically guarantees low output-to-output skew. Optimal design, layout, and processing minimize skew within a device and from device to device. To ensure that the tight skew specification is realized, both sides of any differential output need to be terminated identically into 50 ? even if only one output is being used. If an output pair is unused, both outputs may be left open (unterminated) without affecting skew. The common enable (EN) is synchronous, outputs are enabled/disabled in the LOW state. This avoids a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control. The internal flip flop is clocked on the falling edge of the input clock; therefore, all associated specification limits are referenced to the negative edge of the clock input. The MC100ES6014, as with most other ECL devices, can be operated from a positive VCC supply in PECL mode. This allows the ES6014 to be used for high performance clock distribution in +3.3 V or +2.5 V systems. Single ended CLK input pin operation is limited to a VCC ? 3.0 V in PECL mode, or VEE ? –3.0 V in ECL mode. Designers can take advantage of the ES6014's performance to distribute low skew clocks across the backplane or the board.

特長

- 25 ps Within Device Skew

- 400 ps Typical Propagation Delay

- Maximum Frequency > 2 GHz Typical

- The 100 Series Contains Temperature Compensation

- PECL and HSTL Mode: VCC = 2.375 V to 3.8 V with VEE = 0 V

- ECL Mode: VCC = 0 V with VEE = –2.375 V to –3.8 V

- LVDS and HSTL Input Compatible

- Open Input Default State

- 20-Lead Pb-Free Package Available

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

Processing table

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

ご購入 / サンプル |

|

|---|---|---|---|---|---|---|

| 型名 | ||||||

| TSSOP | 20 | C | Yes | Tube | ||

| TSSOP | 20 | C | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product