# RENESAS

R10DS0281EJ0001

Rev.0.01

Jan 13,2019

### RENESAS Low Latency High Bandwidth Memory (Low Latency DRAM family Gen.5<sup>th</sup>)

## 18 / 9Gb Common I/O x72 Burst Length of 2/4

### 3D-stacked DRAM for Networking & High-Performance Computing.

The Low Latency – Dynamic random-access memory of 5th generation (RENESAS Low Latency DRAM V memory) is suited to networking & High-performance computing system solution that requires reduced randomaccess cycle (tRc) memory which is, in general, called Low Latency High Bandwidth Memory (RENESAS Low Latency HBM). Low Latency HBM consists of multiple Low Latency DRAM memory (called slice) dies in 3D DRAM stack and base die at the bottom. Utilizing on those technology, Low Latency HBM achieves high random access and high bandwidth access and low power consumption with low input voltage.

In the case of 18Gbits capacity configuration1, Low Latency HBM consists of 8 memory dies and 1 base die, which is divided into 16 independent channels. Each channel is completely independent from other channels, and doesn't need to be synchronized with any of them. It has 72bits wide interface architecture with burst length of 2 operating at DDR data rate and reduced random access cycle tRc operation architecture consisting of 16x2banks which compensates the number of tRC/tCK. Low Latency HBM also supports burst length of 4 operating (configuration2) and interface function like standard DRAM.

The Low Latency HBM provides two different configurations as for different types of Networking / High Performance Computing resource memory application. While configuration 1 supports 16Bytes/cycle data transfer rate as a maximum, configuration 2 can achieve up to 16x2Bytes/cycle data transfer rate.

#### Specification

- Configuration1:16-channel x72bits DDR architecture.

- 8K WLs x144bits xCA [4:0] per a bank

- Configuration2: Pseudo 16-channel x72bits DDR 8K WLs x288bits xCA [4:1] per a bank (1-channel has 2 pseudo channels)

- Density:18Gbits w/8 slice dies,16x2banks /a channel 9Gbits w/8 slice dies, 8x2banks /a channel 9Gbits w/4 slice dies,16x1banks /a channel

- Operating frequency

- 1.0GHz

- Random Cycle t<sub>RC</sub>

- 12.0 ns / 16.0 ns t

- Command / Address bus 1/2 cycle DDR input.

- Differential clock inputs (CK\_t/CK\_c)

- One cycle command like SRAM command input.

- Burst Length: 2/4

- Power supply 2.5 V Vpp

- 1.0 V V<sub>DDC</sub>

1.0 V / 1.2V VDDQ

- Refresh command

- Auto Refresh: 8192 cycles / 2 ms for each bank 10-year lifetime with 115° C junction temperature.

| Speed          | tRC      | Operating | Data Rate   | Note                  |  |  |

|----------------|----------|-----------|-------------|-----------------------|--|--|

| Configuration1 | 12cycles | 1.0GHz    | 2.0Gbps/pin | VDDQ 1.0V             |  |  |

| Burst Length2  | (12.0ns) | (1.00ns)  |             | V <sub>DDQ</sub> 1.2V |  |  |

| Configuration2 | 16cycles | 1.0GHz    | 2.0Gbps/pin | VDDQ 1.0V             |  |  |

| Burst Length 4 | (16.0ns) | (1.00ns)  |             | VDDQ 1.2V             |  |  |

Table 1 Main features

Notes. Configuration 1/2 are categorized from difference of µBUMP footprint assignment (transfer data size). Notes. Do not stop CK\* toggling after power-up in all channels. And Keep frequency at 1GHz. Notes. There are two products for  $V_{DDQ}$  1.0 V nominal product and  $V_{DDQ}$  1.2 V nominal product

### This datasheet is digest edition. Please contact Mail Inquires for more information. Mail Inquiries : LowLatencyHBM@lm.renesas.com

### Contents

| RENESAS Low Latency High Bandwidth Memory(Low Latency DRAM family Gen.5th) 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2. Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>3. Package pins.</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4. Interface AC Characteristics       6         Normal bus timing       6         (1) Command /Address bus timing       6         (2) Definition of Data Input / output Timing Waveforms       7         (3) Definition of Data Input / output Timing Specification       8                                                                                                                                                                                                                                                                               |

| 5. Operation       11         5.1. Interface Overview       11         5.2. Clocking       12         5.3. Addressing       12         5.4. Command and Address bus       13         5.5. Command encoding       14         5.7. Command Functional Description       16         5.8. Data mask       18         5.9. Data inversion       18         5.10. Data bus turn-around       18         5.11. Command cycles       18         5.12. Write data cycles       18         5.13. Read data cycles       19         5.14. Automatic Refresh       19 |

| 6. Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7. Test Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8. APPENDIX       19         Revision History       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 1. Overview

Low Latency DRAM of 5<sup>th</sup> generation (Low Latency DRAM V) is, like as Low Latency DRAM II / III / IV (product family), a high-performance DRAM chip targeting on such applications that require high bandwidth and moderately small burst length of random accesses onto a high capacity DRAM memory. The primary design emphasis is on high command access rate and small granularity data size with high random accesses and low power, and the secondary emphasis is on high bandwidth for network / compute resource and work memory. Especially, "random accesses "is defined as t<sub>RC</sub> in specifications. Low Latency HBM is stacked with multiple dies made of Low Latency DRAM technologies archiving short t<sub>RC</sub> DRAM array core architecture.

Low Latency HBM has two type interface footprints defined in two configurations. Configuration1 mainly focuses on Control/Table/Cache memory application (BL2/16Bytes data size), having 16 channels. And, Configuration 2 focuses on Buffer memory application (BL4/32Bytes data size) in network system, having 16 pseudo channels. Low Latency HBM would cover variable next generation applications, and adapt suitable functions to networking / High performance computing system.

### Features Configuration 1 and 2

- $\cdot$  BL = 2 / 4 with 72bits DQ width (16Bytes data size) per a channel (a Pseudo channel).

- · 8192 words, 144I/O (x72bits, DDR), 32 pages per a bank (=36M).

- The Low Latency HBM consists of 8/4 memory (slice) dies and one logic (base) die.

- Differential clock inputs (CK\_t/CK\_c) toggling after power-up in all channels (Keep frequency at 1GHz).

- · DDR commands entered on each positive CK\_t, CK\_c edge. Main commands are single cycle input.

· Semi-independent Row & Column Command Interfaces allowing Activates / Precharges function to be issued in parallel with Reads/Writes.

- $\cdot$  Data referenced to strobes RDQS\_t/RDQS\_c and WDQS\_t/WDQS\_c.

- · Up to 16 channels per stack in case of configuration1. Pseudo 16 channels per stack in case of configuration2.

$\cdot\,$  16x2banks per channel w/8 slice dies (upper 16banks and lower 16banks are selected by SID) in 18Gbits product case.

8x2banks per channel w/8 slice dies or 16banks per channel w/4 slice dies in 9Gbits product case.

- · DBIac support configurable via MRS

- · IO voltage 1.0 V / 1.2V

- $\cdot\,$  DRAM core voltage 1.0 V, independent of IO voltage 1.0V / 1.2V

- · Unterminated data/address/cmd/clk interfaces

- · Temperature sensor

|                           | Configuration1 |            |                  |         | Configu   | Iration2        |

|---------------------------|----------------|------------|------------------|---------|-----------|-----------------|

| Density / Die [Gb]        | 2.3            | 1.1        | 2.3              | 2.3     | 1.1       | 2.3             |

| Memory Stack              |                | 8          | 4                | 8       | 3         | 4               |

| Total Memory[Gb]          | 18             | 9          | 9                | 18      | 9         | 9               |

| Clock Freq.[GHz]          | 1              | .0         | 1.0              | 1       | .0        | 1.0             |

| tRC[ns]                   | 12             | 2.0        | 12.0             | 16      | 6.0       | 16.0            |

| Activation command [Cyc.] |                | 1          | 1                |         | 1         | 1               |

| Burst Length              |                | 2          | 2                | 4       | 4         | 4               |

| # Ch.                     | 1              | 6          | 16               | Pseu    | do 16     | Pseudo 16       |

| #Bank / Ch.               | 16x2           | 8x2        | 16               | 16x2    | 8x2       | 16              |

| #I/O / Ch.                | 72bits         | s DDR      | 72bits DDR       | 72bits  | 5 DDR     | 72bits DDR      |

| Data size                 | 16Bytes        | s x(BL/2). | 16Bytes x(BL/2). | 16Bytes | s x(BL/2) | 16Bytes x(BL/2) |

| Total #I/O                | 1,1            | 152        | 1,152            | 1,1     | 52        | 1,152           |

| Peak B/W [Gbps]           | 2,3            | 304        | 2,304            | 2,3     | 304       | 2,304           |

| Access Rate [Maps]        | 16,            | 000        | 16,000           | 8,0     | 000       | 8,000           |

#### Table 2 Features configuration 1 and 2

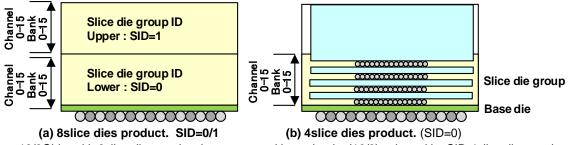

**Notes.** 8slice dies product has upper 16banks and lower 16banks selected by SID.4slice dies product has only lower 16banks. **Notes.** There are two products for V<sub>DDQ</sub> 1.0 V nominal product and V<sub>DDQ</sub> 1.2 V nominal product

**Notes.** In case of 18Gbits product, a bank is selected by bank address of BA [3:0] and SID. In case of 9Gbits product, BA3 or SID do not be used depending on 8 slice dies stack or 4 slice dies stack.

## **2. Electrical Specifications**

Power supplies and DC Characteristics

| Table 5 Absolute Maximum Ratings      |                  |                                |               |      |

|---------------------------------------|------------------|--------------------------------|---------------|------|

| Parameter                             | Symbol           | Conditions                     | Rating        | Unit |

| Supply voltage                        | V <sub>PP</sub>  | 2.5 V nominal                  | -0.3 to +2.8  | V    |

| Supply voltage                        | V <sub>DDC</sub> | 1.0 V nominal                  | -0.3 to +1.26 | V    |

| Output supply voltage,                | V <sub>DDQ</sub> | $V_{DDQ}$ 1.0 V nominal        | -0.3 to +1.26 | V    |

| Input voltage, Input / Output voltage |                  | V <sub>DDQ</sub> 1.2 V nominal | -0.3 to +1.50 | V    |

| hand / O day to self and              |                  | V <sub>DDQ</sub> 1.0 V         | -0.3 to +1.26 |      |

| Input / Output voltage                | VIH / VIL        | V <sub>DDQ</sub> 1.2 V         | -0.3 to +1.50 | V    |

| Junction temperature                  | TJ               |                                | 0 to +125     | °C   |

| Storage temperature                   | T <sub>STG</sub> |                                | -55 to +125   | °C   |

### Table 3 Absolute Maximum Ratings

Notes. There are two products for V\_DDQ 1.0 V nominal product and V\_DDQ 1.2 V nominal product

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

| Parameter                           | Symbol                            | MIN.                      | TYP. | MAX.                      | Unit | Comments                       | Note |

|-------------------------------------|-----------------------------------|---------------------------|------|---------------------------|------|--------------------------------|------|

| Supply voltage                      | V <sub>PP</sub>                   | 2.375                     | 2.5  | 2.625                     | V    |                                | 1,2  |

| Supply voltage                      | V <sub>DDC</sub>                  | 0.950                     | 1.0  | 1.050                     | V    |                                | 1,2  |

|                                     |                                   | 0.950                     | 1.0  | 1.050                     | V    | V <sub>DDQ</sub> 1.0 V nominal | 4.0  |

| Output supply voltage               | V <sub>DDQ</sub>                  | 1.140                     | 1.2  | 1.260                     | V    | V <sub>DDQ</sub> 1.2 V nominal | 1,2  |

| High level output voltage           | V <sub>OH (DC)</sub>              | V <sub>DDQ</sub> *0.7     |      |                           | V    |                                | 1,2  |

| Low level output voltage            | V <sub>OL (DC)</sub>              |                           |      | V <sub>DDQ</sub> *0.3     | V    |                                | 1,2  |

| High level input voltage            | V <sub>IH (DC)</sub>              | V <sub>DDQ</sub> *0.7     |      |                           | V    |                                | 1,2  |

| Low level input voltage             | VIL (DC)                          |                           |      | V <sub>DDQ</sub> *0.3     | V    |                                | 1,2  |

| Differential input crossing voltage | VIX                               | V <sub>DDQ</sub> *0.5-0.1 |      | V <sub>DDQ</sub> *0.5+0.1 | V    |                                | 1,2  |

|                                     |                                   |                           |      |                           | mA   |                                |      |

|                                     |                                   |                           |      |                           | mA   |                                |      |

| Driver strength                     | I <sub>OH</sub> , I <sub>OL</sub> |                           |      |                           | mA   |                                | 1,2  |

| Forcing VDDQ/2 voltage.             |                                   |                           |      |                           | mA   |                                |      |

|                                     |                                   |                           |      |                           | mA   |                                |      |

#### Table 4 Recommended DC Operating Conditions $0^{\circ}C \le T_{J} \le 115^{\circ}C$

**Notes.** There are two products for  $V_{DDQ}$  1.0 V nominal product and  $V_{DDQ}$  1.2 V nominal product **Notes.** All voltage referenced to V<sub>SS</sub> (GND) at µBUMP

### This datasheet is digest edition. Please contact Mail Inquires for more information. Mail Inquiries : LowLatencyHBM@Im.renesas.com

## 3. Package pins.

| Symbol                 | Direction | I/О Туре    | Freq<br>[MHz] | Description                                                                                                          |

|------------------------|-----------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------|

| CK[a:*]_t<br>CK[a:*]_c | Input     | 1.0V / 1.2V | 1000          | Clock inputs:<br>CK_t and CK_c are differential clock inputs. This input clock pair                                  |

|                        |           |             |               | registers address and control inputs on the rising edge of CK_t. CK_c                                                |

|                        |           |             |               | is ideally 180 degrees out of phase with CK_t.<br>Don't stop CK* toggling and change frequency after power-up in all |

|                        |           |             |               | channels (Stable CK* toggling must start at power on sequence).                                                      |

| CKE[a:*]               | Input     | 1.0V / 1.2V | _             | Always CKE HIGH activates after Power UP.                                                                            |

| []                     |           |             |               | CKE must be maintained HIGH throughout read and write accesses,                                                      |

|                        |           |             |               | because of adapting I/O control. Refer to CKE session in detail about                                                |

|                        |           |             |               | CKE usage for LOOP BACK.                                                                                             |

| RESET_n                | Input     | 1.0V / 1.2V | -             | Master reset:                                                                                                        |

| C[a:*]0-C[a:*]7        | Input     | 1.0V / 1.2V | 1000          | Column Command and Address inputs for each command.                                                                  |

|                        |           |             |               | Address inputs, including bank select bits and parity bits.                                                          |

| R[a:*]0-R[a:*]8        | Input     | 1.0V / 1.2V | 1000          | Row Command and Address inputs for each command.                                                                     |

|                        |           |             |               | Address inputs, including bank select bits and parity bits.                                                          |

| WDQS[a:*]0_t           | Input     | 1.0V / 1.2V | 1000          | Write data strobe for DQ and DBI inputs:                                                                             |

| -WDQS[a:*]1_t,         |           |             |               | WDQSx0 => DQx0-DQx31,DQx64-DQx67,DBIx0-DBIx3                                                                         |

| WDQS[a:*]0_c           |           |             |               | WDQSx1 => DQx32-DQx63,DQx68-DQx71,DBIx4-DBIx7                                                                        |

| -WDQS[a:*]1_c          |           |             |               |                                                                                                                      |

| RDQS[a:*]0_t           | Output    | 1.0V / 1.2V | 1000          | Read data strobe for DQ and DBI outputs:                                                                             |

| -RDQS[a:*]1_t,         |           |             |               | RDQSx0 => DQx0-DQx31,DQx64-DQx67,DBlx0-DBlx3                                                                         |

| RDQS[a:*]0_c           |           |             |               | RDQSx1 => DQx32-DQx63,DQx68-DQx71,DBlx4-DBlx7                                                                        |

| -RDQS[a:*]1_c          |           |             | 1000          |                                                                                                                      |

| DQ[a:*]0               | Input     | 1.0V / 1.2V | 1000          | Data input/output: Data size 16Bytes configuration on x72 parts                                                      |

| -DQ[a:*]71             | /Output   |             |               | The DQ signals form the 72bits data bus for 16channel or pseudo                                                      |

|                        |           |             |               | 16channel mode. During READ commands, the data is referenced to                                                      |

|                        |           |             |               | both edges of RDQSx. During WRITE commands, the data is sampled                                                      |

| DDI(- +10              | lanut     | 4.01/14.01/ | 1000          | at both edges of WDQSx.                                                                                              |

| DBI[a:*]0              | Input     | 1.0V / 1.2V | 1000          | Data inversion state for DQ inputs:                                                                                  |

| -DBI[a:*]7             | /Output   |             |               |                                                                                                                      |

|                        |           |             |               | EVEN Byte DQ group<br>DBIx0 => DQx0-DQx7 ,DQx64 DBIx4=>DQx32-DQx39 ,DQx68                                            |

|                        |           |             |               | DBIx0 => DQx0-DQx7 ,DQx04 DBIx4=>DQx32-DQx39 ,DQx06<br>DBIx2 => DQx16-DQx23,DQx66 DBIx6=>DQx48-DQx55 ,DQx70          |

|                        |           |             |               |                                                                                                                      |

|                        |           |             |               | ODD Byte DQ group                                                                                                    |

|                        |           |             |               | DBIx1 => DQx8-DQx15 ,DQx65 DBIx5=>DQx40-DQx47 ,DQx69                                                                 |

|                        |           |             |               | DBIx3 => DQx24-DQx31,DQx67 DBIx7=>DQx56-DQx63,DQx71                                                                  |

| Table 5 Signals in Ident | tification |

|--------------------------|------------|

|--------------------------|------------|

Notes. Input pin has no on-die termination.

Notes. DWORD of Pseudo 16Ch. [a0:h0, a1:h1] (configuration2) / 16Ch. [a: p] (configuration1).

Notes. AWORD of 8Ch. [a; h] (configuration2), / 16Ch. [a; p] (configuration1) [a:\*] = [a0:h0, a1:h1] (configuration2), [a:\*] = [a: p] (configuration1)

Notes. There are two products for VDDQ 1.0 V nominal product and VDDQ 1.2 V nominal product

Notes. "x" means some suffix of channel. In this datasheet, this "x" is often omitted.

## 4. Interface AC Characteristics

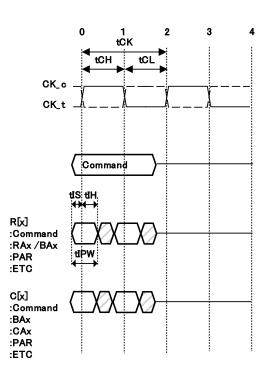

### Normal bus timing

Standard bus timing waveforms and values for command and data are shown in Figure 1 and Interface AC Parameters in Table 6. All timing is measured to/from the crossing point on differential clocks and to/from the half voltage crossing point on single-ended signals.

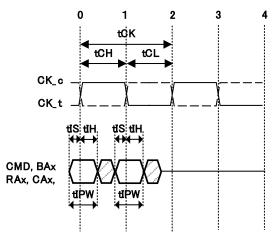

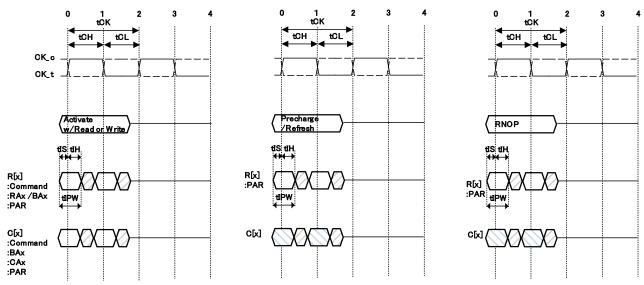

### (1) Command /Address bus timing

**Notes 1.** tIS/tIH is defined in each CK\_t/c edge (Rise) / CK\_c/t edge (Fall).

### Figure 1 DDR Command / Address (R[x], C[x] including BAx, RAx, CAx) Input Timing Waveforms

| Parameter                                          | Symbol                 | Symbol – |      | Unit            | Note |

|----------------------------------------------------|------------------------|----------|------|-----------------|------|

|                                                    | "CK                    | MIN.     | MAX. |                 |      |

| CK clock period                                    | t <sub>ск</sub>        |          |      | ns              |      |

| (maximum 1000 MHz clock frequency, minimum 500MHz) |                        |          |      |                 |      |

| CK_t/_c LOW time                                   | t <sub>CL</sub>        |          |      | t <sub>CK</sub> |      |

| CK_t/_c HIGH time                                  | t <sub>сн</sub>        |          |      | t <sub>ск</sub> |      |

| Clock period jitter                                | t <sub>JIT</sub> (per) |          |      | ns              | 1    |

| Cycle-to-cycle clock jitter                        | t <sub>JIT</sub> (cc)  |          |      | ns              |      |

| CK_t/_c to Input signal pin setup                  | t <sub>IS</sub>        |          |      | ns              | 2    |

| CK_t/_c to Input signal pin hold                   | t <sub>IH</sub>        |          |      | ns              | 2    |

| Input signal pin pulse width                       | t <sub>IPW</sub>       |          |      | ns              |      |

| Table 6 Interface | AC Parameters | ; command inputs |

|-------------------|---------------|------------------|

|                   |               |                  |

Notes 1. Frequency drift is not allowed.

Notes 2. Total  $t_{IS} / t_{IH}$  for  $V_{DDQ}/2$  crosspoint need to add  $\Delta t_{IS} / \Delta t_{IH}$  derating value in **Table 10** to this  $t_{IS} / t_{IH}$  value.

## This datasheet is digest edition. Please contact Mail Inquires for more information.

Mail Inquiries : LowLatencyHBM@lm.renesas.com

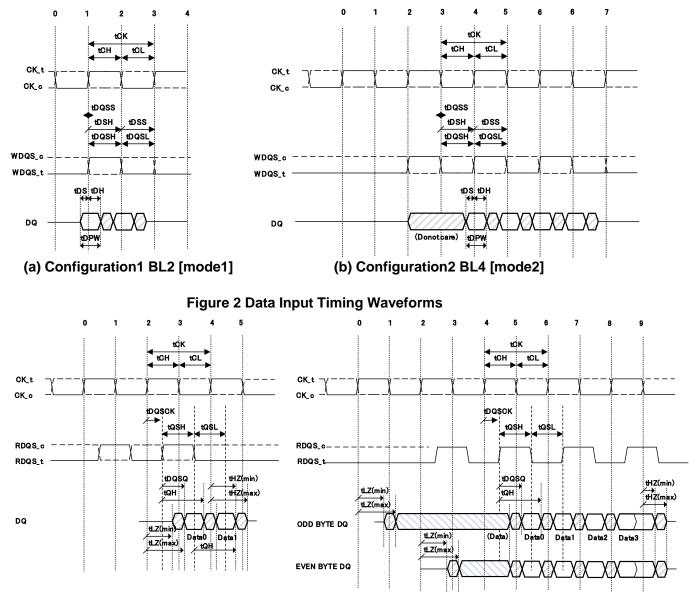

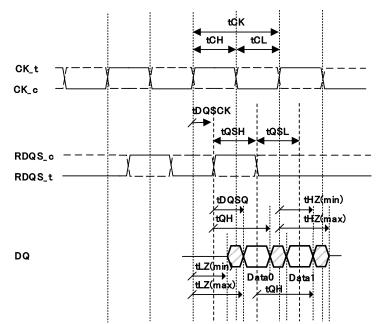

### (2) Definition of Data Input / output Timing Waveforms

Figure 2 shows "Data Input Timing Waveforms". Figure 3 shows "Data Output Timing Waveforms". Low Latency HBM has 2 modes [mode1, mode2] for preamble setting and postamble setting(Table 7). Table 8 shows DQ Byte group assignment.

Unless necessary, this DATASHEET is described in using configuration1 mode1.

#### (a) Configuration1 BL2 [mode1]

(b) Configuration2 BL4 [mode2]

**Notes.** (Data) output is data of previous read command or low data in the case of first read command. **Notes.** Data3 output is half cycle longer in the configuration2 BL4 [mode2] **Notes.** Refer to Table 5 or Table 8 about Byte DQ assignment

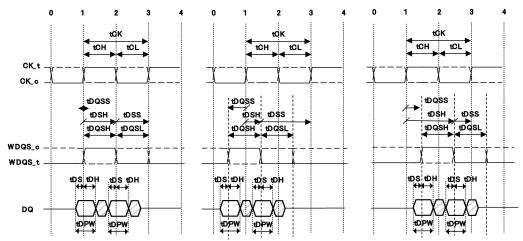

### Figure 3 Data Output Timing Waveforms

| Table 7 Preamble setting and Postamble setting abut cycle number# [tCK] | ]. |

|-------------------------------------------------------------------------|----|

|-------------------------------------------------------------------------|----|

|              | Configuratio | on 1 [mode1] | Configuratio | on 2[mode2] |

|--------------|--------------|--------------|--------------|-------------|

| [tCK]        | Preamble     | Postamble    | Preamble     | Postamble   |

| WRITE (WDQS) | 0            | 0            | 1            | 0           |

| READ (RDQS)  | 1            | 0            | 1            | 1           |

| DQ                 | Byte Group |

|--------------------|------------|

| DQx [7:0], DQx64   | Even Byte  |

| DQx [15:8], DQx65  | Odd Byte   |

| DQx [23:16], DQx66 | Even Byte  |

| DQx [31:24], DQx67 | Odd Byte   |

| DQx [39:32], DQx68 | Even Byte  |

| DQx [47:40], DQx69 | Odd Byte   |

| DQx [55:48], DQx70 | Even Byte  |

| DQx [63:56], DQx71 | Odd Byte   |

Table 8 DO group assignment

**Notes.** DWORD of Pseudo 16Ch. [a:p]=[a0:h0, a1:h1] (configuration2) / 16Ch. [a:p](configuration1).

### (3) Definition of Data Input / output Timing Specification

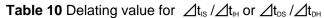

Standard bus timing waveforms and values for data are shown in Figure 4 and Figure 5. Figure 4 shows three cases of Data Input Timing Waveforms for tDQSS (0/-/+). Figure 5 shows Data Output Timing Waveforms.

Notes. tDS/tDH is defined in each WDQS\_t/c edge (Rise) / WDQS\_c/t(Fall).

### Figure 4 Data Input Timing Specification for tDQSS (0/-/+)

| Parameter                                                   | Symbol<br>f <sub>CK</sub> | –<br>(1.0GHz) |      | Unit            | Note |

|-------------------------------------------------------------|---------------------------|---------------|------|-----------------|------|

|                                                             |                           | MIN.          | MAX. |                 |      |

| WDQS_t (rising edge) to CK_t skew (rising edge)             | t <sub>DQSS</sub>         |               |      | t <sub>ск</sub> |      |

| WDQS_t/_c LOW time                                          | t <sub>DQSL</sub>         |               |      | t <sub>ск</sub> |      |

| WDQS_t/_c HIGH time                                         | t <sub>DQSH</sub>         |               |      | t <sub>ск</sub> |      |

| WDQS_t (falling edge) to CK_t (rising edge) setup time      | t <sub>DSS</sub>          |               |      | t <sub>ск</sub> |      |

| WDQS_t (falling edge) from CK_t (rising edge) hold time     | t <sub>DSH</sub>          |               |      | t <sub>ск</sub> |      |

| DQ, DBI to WDQS_t/WDQS_c(rising or falling edge) setup time | t <sub>DS</sub>           |               |      | ns              | 1    |

| WDQS_t/WDQS_c(rising or falling edge) to DQ, DBI hold time  | t <sub>DH</sub>           |               |      | ns              | 1    |

| DQ, DBI input pulse width                                   | t <sub>DPW</sub>          |               |      | ns              |      |

### Table 9 Interface AC Parameters; Data input

**Notes.** Total  $t_{DS} / t_{DH}$  for  $V_{DDQ}/2$  crosspoint need to add  $\Delta t_{DS} / \Delta t_{DH}$  derating value in **Table 10** to this  $t_{DS} / t_{DH}$  value.

### <u>This datasheet is digest edition. Please contact Mail Inquires for more information.</u> <u>Mail Inquiries : LowLatencyHBM@Im.renesas.com</u>

5

| Slew rate [V/ns] | Setup | Hold | Unit |

|------------------|-------|------|------|

| 2                |       |      | ps   |

| 3                |       |      | ps   |

| 4                |       |      | ps   |

| 5                |       |      | ps   |

| 6                |       |      | ps   |

| 7                |       |      | ps   |

| 8                |       |      | ps   |

| 9                |       |      | ps   |

| 10               |       |      | ps   |

**Notes.** RDQS\_t/\_c need clocking of 1 cycle as preamble term before output of DQ data.

0

### Figure 5 Data Output Timing Specification

| Parameter                                 | <b>Symbol</b><br>f <sub>ск</sub> | –<br>(1.0GHz) |      | Unit            | Note |

|-------------------------------------------|----------------------------------|---------------|------|-----------------|------|

|                                           |                                  | MIN.          | MAX. |                 |      |

| RDQS_t/_c LOW time                        | t <sub>QSL</sub>                 |               |      | t <sub>ск</sub> |      |

| RDQS_t/_c HIGH time                       | t <sub>QSH</sub>                 |               |      | t <sub>ск</sub> |      |

| CK to RDQS_t/_c skew                      | t <sub>DQSCK</sub>               |               |      | ns              |      |

| RDQS_t/_c to DQ, DBI skew                 | t <sub>DQSQ</sub>                |               |      | ns              |      |

| DQ, DBI hold time from RDQS_t/_c          | t <sub>QH</sub>                  |               |      | t <sub>ск</sub> |      |

| CK_t/_c to DQ output driver turn-on time  | t <sub>LZ</sub>                  |               |      | ns              |      |

| CK_t/_c to DQ output driver turn-off time | t <sub>HZ</sub>                  |               |      | ns              |      |

#### Table 11 Interface AC Parameters; Data output

### <u>This datasheet is digest edition. Please contact Mail Inquires for more information.</u> Mail Inquiries : LowLatencyHBM@Im.renesas.com

| Table 12 Interface                                  | Symbol          |                   | -    |      |                      |     |

|-----------------------------------------------------|-----------------|-------------------|------|------|----------------------|-----|

| Parameter                                           | f <sub>cк</sub> | (1.00             | 2H4) | Unit | Note                 |     |

|                                                     |                 | ICK               | MIN. | MAX. |                      |     |

| ACTIVATE command to same bank Activate command.     | BL2             | t <sub>RC</sub>   | 12   |      | t <sub>ск</sub>      | 1   |

| Row Cycle time. Single bank refresh Cycle time.     | BL4             | ·rc               | 16   |      | t <sub>CK</sub>      |     |

| ACTIVATE command (w/ Read command; ACT w/RD)        | BL2             | t <sub>RAS</sub>  |      |      | t <sub>CK</sub> / μs | 2   |

| to Precharge command (PRE), Same bank               | BL4             | 1010              |      |      | t <sub>cκ</sub> / μs |     |

| Precharge command (PRE) to ACTIVATE command         | BL2             | t <sub>RP</sub>   |      |      | t <sub>ск</sub>      |     |

| Same bank                                           | BL4             |                   |      |      | t <sub>CK</sub>      |     |

| ACTIVATE command to different bank Activate command | BL2             | t <sub>RRD</sub>  |      |      | t <sub>ск</sub>      | 4   |

| Single Bank refresh command is same definition.     | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Read w/o AP command to different bank Read command  | BL2             | t <sub>CCD1</sub> |      |      | t <sub>ск</sub>      | 3   |

|                                                     | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Read w/o AP command to same bank Read command       | BL2             | t <sub>CCD2</sub> |      |      | t <sub>ск</sub>      | 3   |

|                                                     | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Read w/o AP command to Precharge command(PRE)       | BL2             | t <sub>RTP</sub>  |      |      | t <sub>ск</sub>      | 3   |

|                                                     | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Read command Latency (data output delay)            | BL2             | t <sub>RL</sub>   |      |      | t <sub>CK</sub>      | 9   |

| V <sub>DDQ</sub> 1.0 V nominal product              | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Write command Latency (data input delay)            | BL2             | t <sub>WL</sub>   |      |      | t <sub>ск</sub>      | 9   |

| V <sub>DDQ</sub> 1.0 V nominal product              | BL4             |                   |      | 1    | t <sub>CK</sub>      |     |

| Read command to Write Command Delay                 | BL2             | t <sub>RWD</sub>  |      |      | t <sub>CK</sub>      |     |

| V <sub>DDQ</sub> 1.0 V nominal product              | BL4             |                   |      |      | t <sub>CK</sub>      |     |

| Write command to Read Command Delay                 | BL2             | t <sub>WRD</sub>  |      |      | t <sub>CK</sub>      |     |

| V <sub>DDQ</sub> 1.0 V nominal product              | BL4             |                   |      |      | t <sub>CK</sub>      |     |

| REFRESH command to same bank REFRESH command.       | BL2             | t <sub>RFC</sub>  |      |      | t <sub>CK</sub>      | 5   |

| tRFC=tRC                                            | BL4             |                   |      | -    | t <sub>CK</sub>      |     |

| Read command to different SID Read command          | BL2             | t <sub>CCDR</sub> |      |      | t <sub>ск</sub>      | 6   |

|                                                     | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Max Activate Count w/ Read                          | -               | MACR              |      |      | -                    | 7   |

| Read command Latency (data output delay)            | BL2             | t <sub>RL</sub>   |      |      | t <sub>ск</sub>      | 8,9 |

| V <sub>DDQ</sub> 1.2 V nominal product              | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Write command Latency (data input delay)            | BL2             | t <sub>WL</sub>   |      |      | t <sub>CK</sub>      | 8,9 |

| V <sub>DDQ</sub> 1.2 V nominal product              | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Read command to Write Command Delay                 | BL2             | t <sub>RWD</sub>  |      |      | t <sub>CK</sub>      | 8   |

| V <sub>DDQ</sub> 1.2 V nominal product              | BL4             |                   |      |      | t <sub>ск</sub>      |     |

| Write command to Read Command Delay                 | BL2             | t <sub>WRD</sub>  |      |      | t <sub>ск</sub>      | 8   |

| V <sub>DDQ</sub> 1.2 V nominal product              | BL4             |                   |      |      | t <sub>ск</sub>      |     |

**Table 12** Interface AC Parameters; chip specifications

Notes 1. This command is SRAM like command that operates row activate command w/ Read/Write command (tRCD=0). So, activate command w/o Read/Write command is not supported. And, activate command w/ another bank Read/Write command is not supported.

tRC is minimum value in the case of Write/Read command w/ Auto precharge (w/AP).

**Notes 2.** Do not use Precharge command after Activate command with Auto precharge Read command / Write command (ACT w/RDA, ACT w/WRA) for any bank. These commands reserve precharge command(PRE), automatically.

Notes 3. Write w/o AP command is not supported.

Notes 4. Single Bank refresh at each bank. Command to Command delay definition is as same as tRRD.

Notes 5. There are some limitations regarding optional refresh modes. Refer to those sessions.

Notes 6. Including Activate command w/ Read command. tCCDR=tCCD1+1tCK.

Notes 7. Maximum bank numbers of open bank by ACT w/RD command.

Notes 8. These specifications of  $V_{DDQ}$  1.2 V nominal product are different from those of  $V_{DDQ}$  1.0 V nominal product.

**Notes 9.** The specification of Read/Write Latency is constant value ( $t_{CK}$ ) depending on configuration and  $V_{DDQ}$ .

## 5. Operation

### 5.1. Interface Overview

The primary Low Latency HBM interface consists of a unidirectional command and address bus and a bidirectional data bus. This type of data bus is often referred to as common I/O or CIO. Pin Identification contains the list of pins on the Low Latency HBM.

The command and address bus are a double data rate (DDR) bus consisting of R[x], C[x]. Both the command bus and address bus are clocked by the differential clock pair CK\_t and CK\_c. READ and WRITE commands can be issued at a rate of every single cycles of CK in burst length 2 and 4 mode.

The data interface is a double-rate (DDR) interface that transfers 72bits of data <sup>Note</sup> on each clock edge for 72bits parts and 144bits of data (Pseudo 2channels x 72bits) on each clock edge for 144 bits parts. The data interface also includes 4 data inversion pins. The Low Latency HBM outputs one differential clock pairs, RDQS\_t and RDQS\_c that are associated with read data. Because the data bus is bidirectional, idle cycles are required to implement data bus turnaround as described in 5.10. Data bus turn-around.

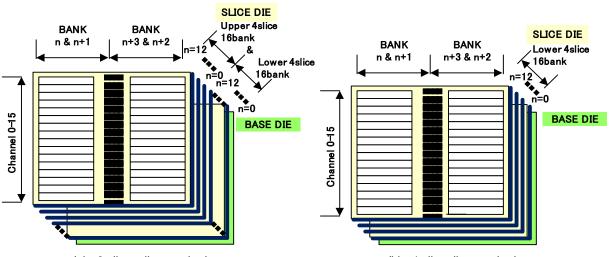

This interface is called a channel. Low Latency HBM has 16 / Pseudo16 channels (8 channels) independently in each configartion1/2. Those channels consist of multiple DRAM dies called as SLICE die and BASE die. For example, 18Gbits Low Latency HBM is containing 8DRAM SLICE dies and 1 BASE die. 4Gbits one has 4DRAM SLICE dies. One SLICE die has 16channels w/ 2banks or 4banks for each case. Figure 6 shows those.

**Note** For parts with 72bits data bus (configuration1), all references in this section should refer to DQ0-DQ71 and DBI0-7 unless otherwise noted in each channel. And, configuration2 uses 2channle parts of configuration1. So, for parts with 144bits data bus, all references in this section should refer to DQ0-DQ71 and DBI0-7 through 2channels unless otherwise noted in each channel.

(a) 8 slices dies stacked

(b) 4 slice dies stacked

**Notes.** The assignment of channels and banks can physically change in the product revision. This figure is just image.

**Notes.** Channel0-15 are indicated by suffix [a:p] in the case of configuration1.

Notes.18/9Gbits with 8slice dies product has upper and lower banks (16/8) selected by SID.4slice dies product has only

lower 16banks.

### Figure 6 over view of DRAM dies stacked with slice dies and base die

### 5.2. Clocking

There are three groups of clock signals: CK\_t/CK\_c, WDQS\_t/WDQS\_c, and RDQS\_t /RDQS\_c.

The CK\_t/CK\_c clock is associated with the address and command pins: R[x], C[x]. At the Low Latency HBM pins, the CK\_t/CK\_c transitions are nominally centered with respect to address and command signal transitions.

The WDQS\_t/WDQS\_c clocks are associated with write data. WDQS\_t/WDQS\_c clocks are used as a source-centered clock for the double data rate DQ0-DQ71, DBI0-DBI7.

The WDQS\_t/WDQS\_c clocks must meet the specified  $t_{DQSS}$  skew with respect to the CK\_t/CK\_c clock to ensure proper timing relationship between command and data cycles and to enable proper data bus turn-around.

The RDQS\_t/RDQS\_c clocks are associated with read data. At the Low Latency HBM pins, and for x72 devices, RDQS\_t/RDQS\_c clocks must be source-synchronous with the read data DQ0-DQ71, DBI0-DBI7 pins.

The RDQS\_t/RDQS\_c clocks must meet the specified  $t_{DQSCK}$  skew with respect to the CK\_t/CK\_c clock to ensure proper timing relationship between command and data cycles and to enable proper data bus turn-around.

Table 13 channel addressing

| Table 13 channel addressing |               |             |          |                |         |          |  |

|-----------------------------|---------------|-------------|----------|----------------|---------|----------|--|

|                             |               | Configu     | iration1 | Configuration2 |         |          |  |

| Product density             | 18Gbits       | 9Gbits      | 9Gbits   | 18Gbits        | 9Gbits  | 9Gbits   |  |

| Memory Stack                | 8             | 3           | 4        | 8              | 3       | 4        |  |

| Configuration               |               |             | 1        |                | -       | 2        |  |

| # Ch.                       |               | 1           | 6        |                | Pseu    | do 16    |  |

| Access data size            |               | 72bits      | x BL2    |                | 72bits  | x BL4    |  |

| Row address                 |               | RA[′        | 12:0]    | RA[12:0]       |         |          |  |

| Size                        |               | 8           | K        | 8K             |         |          |  |

| Col address                 |               | CA[         | 4:0]     | CA[4:1]        |         |          |  |

| Size                        |               | 3           | 2        | 16             |         |          |  |

| Bank address                | BA[3:0],      | BA[2:0]     | BA[3:0]  | BA[3:0]        | BA[2:0] | BA[3:0]  |  |

|                             |               | (BA3=0)     |          |                | (BA3=0) |          |  |

|                             | S             | SID (SID=0) |          | SID            |         | (SID=0)  |  |

| Size                        | 16x2          | 8x2         | 16       | 16x2           | 8x2     | 16       |  |

| Page size                   | 4608          |             | 4608     | 46             | 08      | 4608     |  |

| -                           | 144lOx32 144l |             | 144IOx32 | 288IOx16       |         | 288lOx16 |  |

| Refresh / a bank            | 8K/2ms        |             |          |                | 8K/     | 2ms      |  |

### 5.3. Addressing

Notes. 10-year lifetime with 115°C junction temperature.

Notes. SID means "Slice die group ID" showed by following figure.

**Notes.** 18/9Gbits with 8slice dies product has upper and lower banks (16/8) selected by SID.4slice dies product has only lower 16banks.

### 5.4. Command and Address bus

In Burst of 2/4 mode one clock cycle is required to load the multiplexed command and address. In DDR Command and Address mode command and address inputs are captured by the RAM in two beats per cycle. Two of the bits in the command and address field select which of the banks in the RAM will be accessed. The bit functions as an ordinary command and address bits in the devices described in this data sheet.

| Row command/address (CMD/BAx, RAx) |              |              |  |  |  |  |  |

|------------------------------------|--------------|--------------|--|--|--|--|--|

| Activate                           | Rising (BT0) | Falling(BT1) |  |  |  |  |  |

| R[8]                               | L            | RA13/L       |  |  |  |  |  |

| R[7]                               | RA12         | RA6          |  |  |  |  |  |

| R[6]                               | RA11         | RA5          |  |  |  |  |  |

| R[5]                               | RA10         | RA4          |  |  |  |  |  |

| R[4]                               | RA9          | RA3          |  |  |  |  |  |

| R[3]                               | RA8          | RA2          |  |  |  |  |  |

| R[2]                               | RA7          | PAR          |  |  |  |  |  |

| R[1]                               | Command      | RA1          |  |  |  |  |  |

| R[0]                               | Command      | RA0          |  |  |  |  |  |

### Table 14 single cycle row/col command and address assignment example (bit encoding; BT0-1).

| Col comman   | Col command/address (CMD/BAx, CAx) |              |  |  |  |  |  |

|--------------|------------------------------------|--------------|--|--|--|--|--|

| Read / Write | Rising (BT0)                       | Falling(BT1) |  |  |  |  |  |

| C[7]         | PCS/V                              | V            |  |  |  |  |  |

| C[6]         | SID/V                              | Command      |  |  |  |  |  |

| C[5]         | BA3/V                              | CA4          |  |  |  |  |  |

| C[4]         | BA2                                | CA3          |  |  |  |  |  |

| C[3]         | BA1                                | CA2          |  |  |  |  |  |

| C[2]         | BA0                                | PAR          |  |  |  |  |  |

| C[1]         | Command                            | CA1          |  |  |  |  |  |

| C[0]         | Command                            | CA0/V        |  |  |  |  |  |

Notes. CA0 for BL2. CA0 don't care at BL4.

Notes. V means Valid Signal (either H or L, but not floating)

Notes. Following session exactly shows command encoding table in detail.

**Notes.** Edge of BT0 is rising edge of command clock (CK). Edge of BT1 is falling edge of command clock (CK). **Notes.** tIS/tIH is defined in each CK\_t/c edge (Rise/Fall) / CK\_t/c(Fall/Rise).

#### Figure 7 DDR Command / Address (R[x], C[x] including BAx, RAx, CAx) Input Timing Waveforms

### 5.5. Command encoding

The Low Latency HBM supports standard 9 types of command. The 4 types of command are Row commands as shown in Table 15 and Figure 8. The 5 types of command are Col commands as shown in Table 16 and Figure 9.

| Function       | Sym. | Clock<br>Edge | R[0] | R[1] | R[2] | R[3] | R[4] | R[5]  | R[6]  | R[7]  | R[8]   |

|----------------|------|---------------|------|------|------|------|------|-------|-------|-------|--------|

| Row NO         | RNOP | Rising        | Н    | Н    | V    | V    | V    | V     | V     | V     | L      |

| operation      |      | Falling       | V    | V    | PAR  | V    | V    | V     | V     | V     | L      |

| Activate w/RD, | ACT  | Rising        | L    | Н    | RA7  | RA8  | RA9  | RA10  | RA11  | RA12  | L      |

| RDA,or WRA.    |      | Falling       | RA0  | RA1  | PAR  | RA2  | RA3  | RA4   | RA5   | RA6   | RA13/L |

| Precharge      | PRE  | Rising        | Н    | L    | BA0  | BA1  | BA2  | BA3/V | SID/V | PCS/V | L      |

|                |      | Falling       | V    | V    | PAR  | V    | V    | V     | V     | V     | L      |

| Refresh        | REF  | Rising        | L    | L    | BA0  | BA1  | BA2  | BA3/V | SID/V | PCS/V | L      |

| Single Bank    |      | Falling       | V    | V    | PAR  | V    | V    | V     | V     | V     | L      |

### Table 15 Over view of Row commands

Notes. CKE = H (CKE should be LOW preventing for illegal commands at initialization.)

Notes. Active command needs col commands (write / read commands) referring to BA [0:3], SID, PCS of Col commands

Notes. RA13 is only used at 36Gbits configuration in future. And R [8] bit can be reserved pin and must be set 0.

Notes. Bank open for COL operation needs "ACT commands"

Notes. Use PCS at pseudo channel mode (Burst length 4).

Notes. Configuration2 is double data size of Configuration1 divided by PCS.

**Notes.** Use SID at 8slice dies product due to choose lower or upper four slice dies. (SID=0 recommended when 4slice dies product. BA3=0 recommended when BA3 do not be used).

Notes. Parity is calculated on all pins of each command when the parity function is enabled in the mode register.

### Figure 8 DDR Command / Address (R[x], C[x] including BAx, RAx, CAx) Input Timing Waveforms

- The two types of NO OPERATION (NOP) command (RNOP, CNOP) must be used on any cycle where no other commands are requested.

- ✓ The ACTIVATE (ACT) command is used to initiate an activate operation of a single bank, but this command needs read command or write command as same timing.

- The PRECHARGE (PRE) command is used to initiate a precharge operation on a particular bank of the memory.

- The REF command is used to initiate a refresh operation on a particular bank of the memory.

| Function     | Sym.     | Clock<br>Edge | C[0]                                                                              | C[1] | C[2] | C[3] | C[4] | C[5]  | C[6]  | C[7]  |  |

|--------------|----------|---------------|-----------------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|--|

|              |          | Luge          |                                                                                   |      |      |      |      |       |       |       |  |

| Column NO    | CNOP     | Rising        | Н                                                                                 | Н    | V    | V    | V    | V     | V     | V     |  |

| Operation    |          | Falling       | V                                                                                 | V    | PAR  | V    | V    | V     | V     | V     |  |

| Read         | RD       | Rising        | Н                                                                                 | L    | BA0  | BA1  | BA2  | BA3/V | SID/V | PCS/V |  |

|              |          | Falling       | CA0/V                                                                             | CA1  | PAR  | CA2  | CA3  | CA4   | L     | V     |  |

| Read w/ AP   | RDA      | Rising        | Н                                                                                 | L    | BA0  | BA1  | BA2  | BA3/V | SID/V | PCS/V |  |

|              |          | Falling       | CA0/V                                                                             | CA1  | PAR  | CA2  | CA3  | CA4   | Н     | V     |  |

| Write w/ AP  | WRA      | Rising        | L                                                                                 | Н    | BA0  | BA1  | BA2  | BA3/V | SID/V | PCS/V |  |

|              |          | Falling       | CA0/V                                                                             | CA1  | PAR  | CA2  | CA3  | CA4   | Н     | L     |  |

| Mode         | MRS      | Rising        | L                                                                                 | L    | Н    | OP6  | OP7  | MRA0  | MRA1  | V     |  |

| Register set |          | Falling       | OP0                                                                               | OP1  | PAR  | OP2  | OP3  | OP4   | OP5   | V     |  |

|              | (CKE abo |               | tes CKE - H (CKE should be LOW preventing for illegal commands at initialization) |      |      |      |      |       |       |       |  |

Table 16 Over view of Col commands

Notes. CKE = H (CKE should be LOW preventing for illegal commands at initialization.)

Notes. Use PCS at pseudo channel mode (Burst length 4).

Notes. MRA [1:0] and OP [7:0] are showed in detail by Configuration session.

Notes. CA0 for BL2 (Burst length2). CA0 don't care BL4 (Burst length 4).

**Notes.** 18/9Gbits with 8slice dies product has upper and lower banks (16/8) selected by SID.4slice dies product has only lower 16banks. SID/BA3=0 fixed is each recommended when not to use.

**Notes.** Parity is calculated on all pins of each command when the parity function is enabled in the mode register.

Notes. The WRITE (WR) command is not used to initiate a burst write. This command is not permitted.

Figure 9 DDR Command / Address (R[x], C[x] including BAx, RAx, CAx) Input Timing Waveforms

- ✓ The two types of NO OPERATION (NOP) command (RNOP, CNOP) must be used on any cycle where no other commands are requested.

- The READ (RD) command is used to initiate a burst read from the Low Latency HBM.

- ✓ The READ with PRECHARGE (RDA) command is used to initiate a burst read and automatic PRECHARGE (PRE) operation.

- ✓ The WRITE with PRECHARGE (WRA) command is used to initiate a burst write and automatic PRECHARGE (PRE) operation.

- ✓ WRA command needs ACT command.

- ✓ The Mode Register set (MRS) command is used to configure the Low Latency HBM following a reset. Because READ and WRITE commands require one cycle to fully transfer their associated address in burst length 2/4 mode.

### **5.7. Command Functional Description**

**Notes.** tRWD/tWRD here is the value specified by Low Latency HBM device internal bus turnaround time and it is strongly recommended to add extra NOP to keep the system bus turnaround time

Notes. The two types of NO OPERATION (NOP) command (RNOP, CNOP) must be used on any cycle where no other commands are requested.

**Notes.** CL is Cas Latency (READ). CWL is Cas Write Latency(Write)

Notes. This figure is a conceptual diagram. For example, RDQS / WDQS preamble and postamble cycle are omitted.

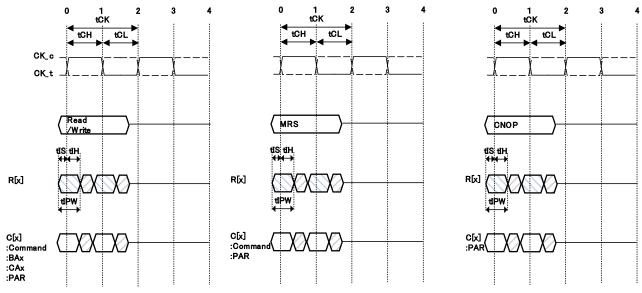

#### Figure 10 Single cycle activate command description of burst length2 (Configuration1)

#### Table 17 AC timing parameters ; Configuration1 (example)

|       | j    | pa.a         | garanor (onampio/     |

|-------|------|--------------|-----------------------|

|       | Cor  | nfiguration1 | comment               |

|       | BL2  |              |                       |

|       | Сус  | ns           | Minimum spec example. |

| tCK   | 1GHz | 1.00         |                       |

| tRC   | 12   | 12.00        | Fast Random ROW Cycle |

| tRCD  | 0    | 0.00         |                       |

| tRAS  |      |              | tRAS+tRP=tRC          |

| tRP   |      |              | tRAS+tRP=tRC          |

| tRL   |      |              | Read command To Data  |

| tWL   |      |              | Write command To Data |

| tRRD  |      |              | ROW to ROW            |

| tCCD1 |      |              | COL to COL            |

| tCCD2 |      |              | COL to COL(same bank) |

| tRWD  |      |              | Read to Write         |

| tWRD  |      |              | Write to Read         |

**Notes.** tCCD1 is the case of another banks access / tCCD2 is the same of same bank access. **Notes.** tRAS means tRTP at ACT with READ. Refer to tRTP in burst access case.

This figure is a conceptual diagram. This datasheet is digest edition. Please contact Mail Inquires for more information. Mail Inquiries : LowLatencyHBM@lm.renesas.com

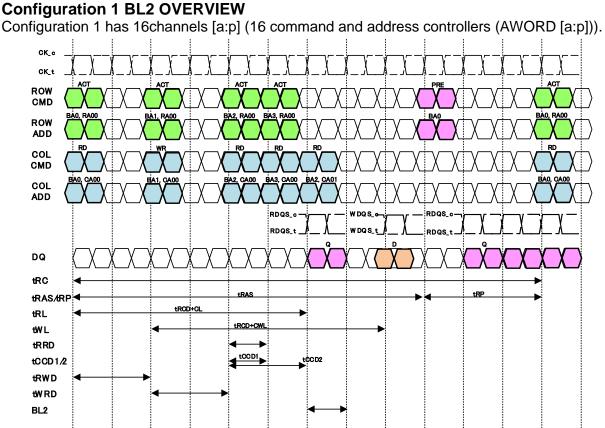

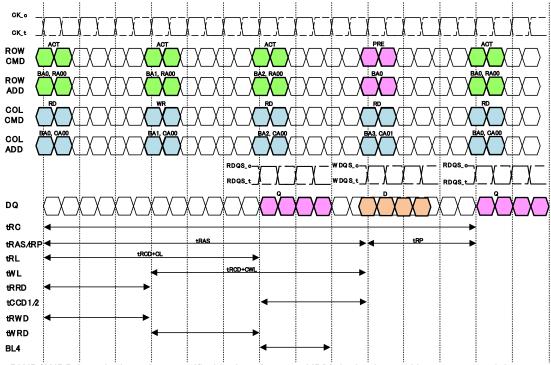

### Configuration 2 BL4 OVERVIEW

Configuration 1 has 16channels [a:p] (16 command and address controllers (AWORD[a:p])). Configuration 2 has 8channels [a:h](8 command and address controllers (AWORD [a:h])). Channel size of configuration2 is half of configuration1.This figure is just simple image for understanding. Configuration 2 is based on pseudo channel mode shown in following page.

**Notes.** tRWD/tWRD here is the value specified by Low Latency HBM device internal bus turnaround time and it is strongly recommended to add extra NOP to keep the system bus turnaround time

Notes. The two types of NO OPERATION (NOP) command (RNOP, CNOP) must be used on any cycle where no other

commands are requested.

Notes. CL is Cas Latency (READ). CWL is Cas Write Latency (Write)

Notes. This figure is a conceptual diagram. For example, RDQS / WDQS preamble and postamble cycle are omitted.

#### Figure 11 Single cycle activate command description of burst length4 (Configuration2)

#### Table 18 AC timing parameters ; Configuration2 (example)

|       | Cor  | nfiguration2 | comment               |  |  |  |  |  |

|-------|------|--------------|-----------------------|--|--|--|--|--|

|       | BL4  |              |                       |  |  |  |  |  |

|       | Сус  | ns           | Minimum spec example. |  |  |  |  |  |

| tCK   | 1GHz | 1.00         |                       |  |  |  |  |  |

| tRC   | 16   | 16.00        | Fast Random ROW Cycle |  |  |  |  |  |

| tRCD  | 0    | 0.00         |                       |  |  |  |  |  |

| tRAS  |      |              | tRAS+tRP=tRC          |  |  |  |  |  |

| tRP   |      |              | tRAS+tRP=tRC          |  |  |  |  |  |

| tRL   |      |              | Read command To Data  |  |  |  |  |  |

| tWL   |      |              | Write command To Data |  |  |  |  |  |

| tRRD  |      |              | ROW to ROW            |  |  |  |  |  |

| tCCD1 |      |              | COL to COL            |  |  |  |  |  |

| tCCD2 |      |              | COL to COL(same bank) |  |  |  |  |  |

| tRWD  |      |              | Read to Write         |  |  |  |  |  |

| tWRD  |      |              | Write to Read         |  |  |  |  |  |

**Notes.** tCCD1 is the case of another banks access / tCCD2 is the same of same bank access. **Notes.** tRAS means tRTP at ACT with READ. Burst access refers to tRTP.

This figure is a conceptual diagram. This datasheet is digest edition. Please contact Mail Inquires for more information. Mail Inquiries : LowLatencyHBM@lm.renesas.com

### 5.8. Data mask

This function is not supported.

### 5.9. Data inversion

To reduce simultaneous switch noise, I/O current and average I/O power, the Low Latency HBM provides the ability to invert all data pins. Because the nominal design for Low Latency HBM I/O signals is not termination.

### 5.10. Data bus turn-around

Because the DQn-DQ0 and DBIm-DBI0 pins are bidirectional, care must be taken to ensure that the Low Latency HBM and the system chip connected to it do not drive these pins simultaneously. To guarantee this, a rapid DQ and DBI turn-off time is required. The actual bus turn-around time is dependent on many system parameters, including BL, RL, WL, pre-amble, post-amble, controller I/O timing, DRAM I/O timing, PCB delays; and the system must ensure that neither Low Latency HBM, nor the system chip is driving the bus during that time. This is accomplished by inserting a sufficient number of NOP commands between each READ-to-WRITE command transition and between each WRITE-to-READ transition. Additional NOP commands may be required to allow settling of the bus to insure no adverse effect on I/O timing.

### 5.11. Command cycles

A command to the Low Latency HBM is initiated by driving the R[x], C[x] pin low at the rising edge of CK the appropriate state corresponding to the command.

READ and WRITE commands each require 1 clock to send the full command in burst length 2/4 mode, due to the multiplexed nature of Address loading. The ACT, PRE, NOP and AUTO REFRESH commands are each a single cycle in length.

### 5.12. Write data cycles

DQ0-DQn, DBI0-DBIm associated with a WRITE command are received by the Low Latency HBM in a DDR burst, starting on a rising edge of WDQS\_t that is offset WL clock cycles from rising edge of the CK signal corresponding to the first cycle that the WRITE command was initiated. This delay of WL cycles is intended to ensure that the write data are not driven at the same time that data from a previous READ command are being driven from the Low Latency HBM.

## 5.13. Read data cycles

DQ0-DQn and DBI0-DBIm associated with a READ command are driven by the Low Latency HBM in a DDR burst, RL clock cycles from the rising edge of the CK signal corresponding to the first cycle that the READ command was initiated. This delay of RL cycles is equal to the delay required for the internal logic and memory within the Low latency HBM to read data and make it available on the bus.

### 5.14. Automatic Refresh

Refresh cycles of the internal memory are initiated via the Automatic "Refresh command". Each refresh command causes a single refresh cycle to occur on the bank specified in the command. The minimum data retention time is 2ms over the temperature range specified in "**1**. Electrical Specifications", and there are 8192 words in each bank. Therefore, each bank must receive 8192 refresh commands every 2ms in order to ensure proper data retention.

## 6. Initialization

Prior to functional use, Low Latency HBM must be initialized and configured. The steps described in this chapter will ensure that the internal logic of Low Latency HBM has been properly reset and that the functional timing parameters of the chip have been configured.

## 7. Test Specification

Low Latency HBM supports direct access test mode (DA) as for product qualifications and specifications, and a limited set of test functions as in test mode via command pin.

## 8. APPENDIX

**Revision History**

RENESAS Low Latency High Bandwidth Memory (Low Latency DRAM family Gen.5th)

|           |          | Description |                                          |

|-----------|----------|-------------|------------------------------------------|

| Rev.      | Date     | Page        | Summary                                  |

| Rev.0.001 | '19.1.13 | -           | New Preliminary Datasheet Digest Edition |

|           |          |             |                                          |

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power is supplied until the power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable. Voltage application waveform at input pin

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.)

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a systemevaluation test for the given product.

### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.