## 3A デュアル出力、1MHz/2.5MHz 動作、 高効率同期整流降圧型レギュレータ

#### ISL8036, ISL8036A

ISL8036/ISL8036A は低消費電力で低電圧のアプリケーションに最適な降圧レギュレータです。定格 3A のデュアル出力またはカレントシェアによる 6A 出力に対応し、スイッチング周波数は 1MHz (ISL8036) または 2.5MHz (ISL8036A) です。入力RMS電流と EMI を抑えるために、2 系統のチャネルは180°異なる位相で動作します。両方のチャネルともに 0.8Vを下限とする低電圧出力に最適化されています。入力電圧範囲は 2.8V  $\sim$  6V で、シングルセルの Li イオンバッテリ、3 セルの NiMH バッテリ、または 5V レギュレート電源が使えます。180°異なる位相で動作する 2 系統のチャネルはそれぞれ 3A以上の出力電流が保証されているほか、カレントシェア・モードで回路を構成すると 1 系統の 6A 出力が得られます。なお、カレントシェア動作では PWM スイッチングがインターリーブ動作となるため、入力リップルと出力リップルが抑えられます。

ISL8036/ISL8036A は、低オン抵抗の P チャネル MOSFET と N チャネル MOSFET をそれぞれペアで内蔵して、変換効率の向上と外付け部品数の削減とを実現しています。100% デューティサイクル動作が可能であり、それぞれのチャネルともに 3A 出力時のドロップ電圧は 250mV 以下です。

パワーアップ時に動作するチャネルごとの1msのパワーグッド (PG) タイマと、シャットダウン時に動作する出力コンデンサの放電回路を内蔵しています。そのほか、ソフトスタート機能、パワーシーケンスを実現するイネーブル機能、過電流保護機能、サーマル・シャットダウン機能を備えています。

ISL8036/ISL8036A は 4mm×4mm サイズで最大高さ 1mm 0 24 リード QFN パッケージで供給されます。 コンバータ回路は 1.5cm<sup>2</sup> 以下のサイズで構成可能です。

### 特長

- 最高効率 95%の、3A 出力同期整流降圧レギュレータ

- ・ 温度範囲 / 負荷範囲 / 入力電圧範囲の全域で出力精度 2%

- 1.5ms のソフトスタート内蔵

- 6A 出力が得られるカレントシェア・モード

- 最高 6MHz まで外部同期可能

- 電流モード補償回路内蔵

- ピーク電流制限と hiccup (脈動)モードによる短絡保護

- 逆過電流保護

### アプリケーション

- DC/DC POL モジュール

- マイクロコントローラ / マイクロプロセッサ、FPGA や DSP の電源

- ルータやネットワーク・スイッチ用のプラグイン DC/DC モジュール

- 計測機器

- リチウムイオン・バッテリでアプリケーション・ノート 動作するモバイル機器

- バーコード・リーダ

### 関連ドキュメント

- アプリケーション・ノート AN1616

「ISL8036CRSHEVAL1Z Current Sharing 6A Low Quiescent Current High Efficiency Synchronous Buck Regulator」

- ・ アプリケーション・ノート <u>AN1617</u> 「ISL8036DUALEVAL1Z Dual 3A Low Quiescent Current High Efficiency Synchronous Buck Regulato」

- アプリケーション・ノート AN1615

「ISL8036ACRSHEVAL1Z Current Sharing 6A Low Quiescent Current High Efficiency Synchronous Buck Regulator」

- アプリケーション・ノート AN1618

「ISL8036ADUALEVAL1Z Dual 3A Low Quiescent Current

High Efficiency Synchronous Buck Regulator」

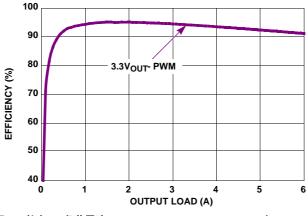

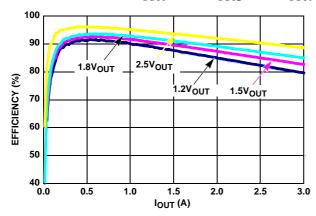

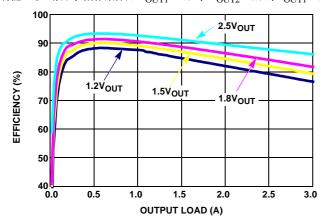

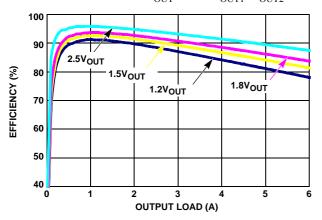

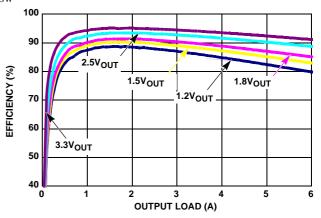

図 1. 効率 vs 負荷電流、1MHz、V<sub>IN</sub> = 5V、PWM モード、T<sub>A</sub> = +25 ℃

### アプリケーション回路例

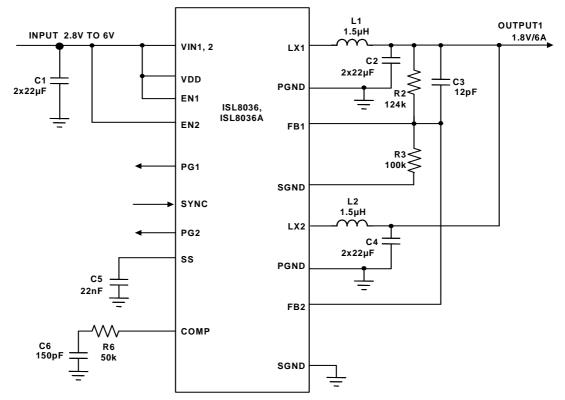

図 2. アプリケーション回路例 - 6A シングル出力

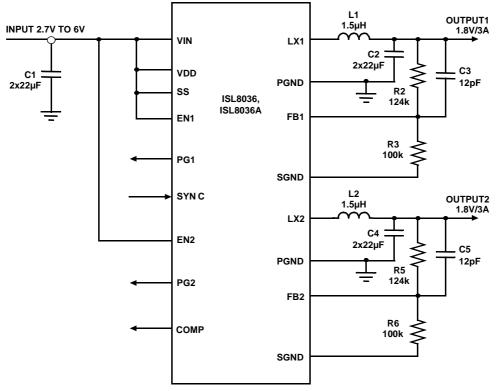

図 3. アプリケーション回路例 - 3A デュアル出力

## ISL8036, ISL8036A

#### 表 1. デュアル出力構成時の部品定数

| V <sub>OUT</sub> | 0.8V      | 1.2V      | 1.5V      | 1.8V      | 2.5V      | 3.3V      |

|------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| C1               | 2x22μF    | 2x22μF    | 2x22μF    | 2x22μF    | 2x22μF    | 2x22µF    |

| C2(またはC4)        | 2X22μF    | 2Χ22μF    | 2Χ22μF    | 2X22μF    | 2X22μF    | 2X22μF    |

| L1(またはL2)*       | 1.0~2.2µH | 1.0~2.2µH | 1.0~2.2µH | 1.0~3.3µH | 1.0~3.3µH | 1.0~4.7µH |

| R2(またはR5)        | 0         | 50k       | 87.5k     | 124k      | 212.5k    | 312.5k    |

| R3(またはR6)        | 100k      | 100k      | 100k      | 100k      | 100k      | 100k      |

<sup>\*</sup> ISL8036A の L1 (または L2) に使用する値は、各  $V_{OUT}$  ともに上記で指定された値の 1/2 とします。

#### 表 2. カレントシェア構成時の部品定数

| V <sub>OUT</sub> | 0.8V      | 1.2V      | 1.5V      | 1.8V      | 2.5V      | 3.3V      |

|------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| C1               | 2x22μF    | 2x22μF    | 2x22μF    | 2x22μF    | 2x22μF    | 2x22μF    |

| C2(またはC4)        | 2X22μF    | 2X22μF    | 2Χ22μF    | 2Χ22μF    | 2Χ22μF    | 2X22μF    |

| L1(またはL2)*       | 1.0~2.2µH | 1.0~2.2µH | 1.0~2.2µH | 1.0~3.3µH | 1.0~3.3µH | 1.0~4.7µH |

| R2               | 0         | 50k       | 87.5k     | 124k      | 212.5k    | 312.5k    |

| R3               | 100k      | 100k      | 100k      | 100k      | 100k      | 100k      |

| R6               | 30k       | 33k       | 31k       | 30k       | 29k       | 28k       |

| C6               | 250pF     | 180pF     | 150pF     | 150pF     | 150pF     | 150pF     |

<sup>\*</sup> ISL8036A の L1 (または L2) に使用する値は、各  $V_{OUT}$  ともに上記で指定された値の 1/2 とします。

Note: 所望のソフトスタート時間を得る C5 の容量 (22nF) は式 1 で与えられます。

#### 表 3. 2 品種の違い

| 型番       | スイッチング周波数                            |

|----------|--------------------------------------|

| ISL8036  | 内部スイッチング周波数 F <sub>SW</sub> = 1MHz   |

| ISL8036A | 内部スイッチング周波数 F <sub>SW</sub> = 2.5MHz |

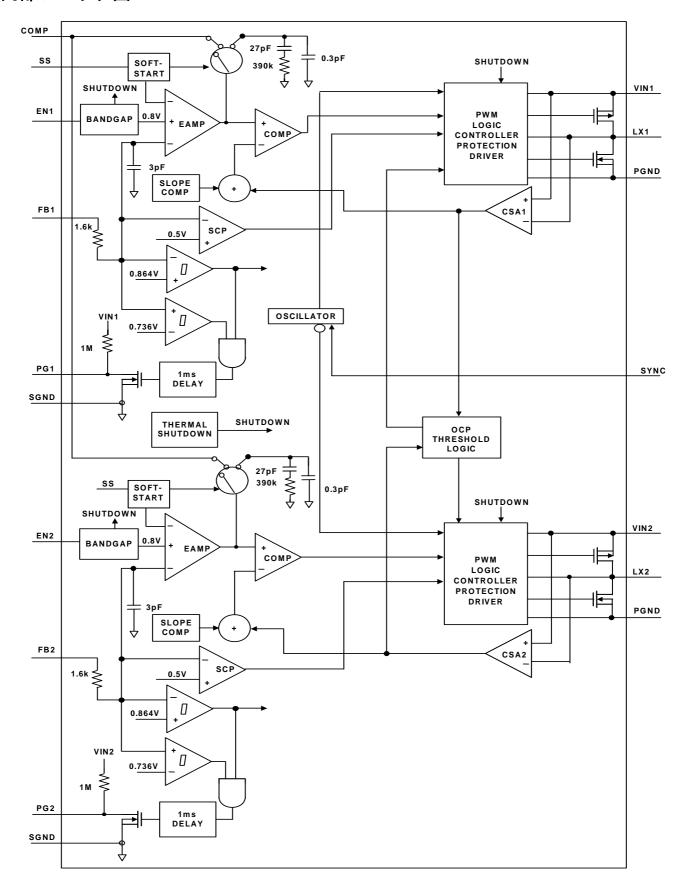

### 内部ブロック図

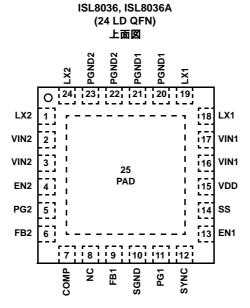

## ピン配置

### ピンの説明

| ピン番号   | ピン名称  | 説明                                                                                                                                                                                                                                                                                   |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 24  | LX2   | チャネル2のスイッチング・ノードです。VOUT2の出力インダクタの一方の端子に接続してください。                                                                                                                                                                                                                                     |

| 22, 23 | PGND2 | チャネル2のパワーステージ用の負極性電源入力です。                                                                                                                                                                                                                                                            |

| 4      | EN2   | チャネル2のイネーブルピンです。High を与えると出力 VOUT2 が有効になります。Low を与えると VOUT2 をシャットダウンし、出力コンデンサを放電します。開放のまま使用しないでください。                                                                                                                                                                                 |

| 5      | PG2   | 1ms タイマの出力です。パワーアップのとき、または EN ピンに High を与えたとき、PG2 ピンには VOUT2<br>電圧の状態を示すパワーグッド信号が 1ms だけ遅延して出力されます。                                                                                                                                                                                  |

| 6      | FB2   | チャネル 2 レギュレータの帰還ネットワーク入力です。カレントシェア動作のときは FB1 ピンに接続してください。                                                                                                                                                                                                                            |

| 7      | COMP  | カレントシェアとして動作させるときは、ループ補償性能を高めるために、COMP ピンと SGND との間に補償ネットワークを外付けしてください。また、SS ピンには外付けコンデンサを接続してください。デュアルモードとして動作させるときは、COMP ピンは NC としてください。この場合、内部補償回路が使われます。<br>SS ピンにソフトスタート・コンデンサが接続される場合 (VIN に接続しない場合)、外部補償回路が使われます。カレントシェアとして動作させるときには、COMP ピンに RC 回路を接続してください。                 |

| 8      | NC    | 未使用ピンです。グラウンドに接続してください。                                                                                                                                                                                                                                                              |

| 9      | FB1   | チャネル1レギュレータの帰還ネットワーク入力です。FB1はトランスコンダクタンス誤差アンプの負入力(反転入力)に内部で接続されています。レギュレータの出力電圧はFB1に接続した分圧抵抗によって設定します。分圧比を適切に選択すれば、電源レール(コンバータ損失を引いた電圧)を上限とし、0.8Vを下限とする範囲で、出力電圧を任意の電圧に設定可能です。一般的なアプリケーションでは内蔵の補償回路のままで問題ありません。FB1ピンは、チャネル1のレギュレータ出力電圧をモニタする目的で、レギュレータのパワーグッド回路とアンダーボルテージ保護回路にも使われます。 |

| 10     | SGND  | システム・グラウンドです。                                                                                                                                                                                                                                                                        |

| 11     | PG1   | 1ms タイマの出力です。パワーアップのとき、または EN ピンに High を与えたとき、PG1 ピンには VOUT1<br>電圧の状態を示すパワーグッド信号が 1ms だけ遅延して出力されます。                                                                                                                                                                                  |

| 12     | SYNC  | 内部発振周波数でスイッチングさせる場合は、SYNC ピンにロジック High レベルを与えるか入力電圧 VIN を接続します。外部同期を行うには SYNC ピンに外部クロックを与えます。立ち下がりエッジ・トリガです。<br>SYNC ピンは開放のまま使用してはなりません。また、Low レベルのまま使用したり、SGND に接続してはなりません。                                                                                                         |

| 13     | EN1   | チャネル 1 のイネーブルピンです。High を与えると出力 VOUT2 が有効になります。Low を与えると VOUT1 をシャットダウンし出力コンデンサを放電します。開放のまま使用しないでください。                                                                                                                                                                                |

### ピンの説明

| ピン番号           | ピン名称          | 説明                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | SS            | SS ピンを使ってソフトスタート時間を設定します。SS ピンを VIN に接続したときのソフトスタート時間は、1.5ms になります。デュアルモード動作では、SS ピンを VIN に接続してください。 カレントシェア動作では、SS ピンをコンデンサ $C_{SS}$ に接続し、外部補償回路を使用します。SS ピンと SGND の間に接続した $C_{SS}$ によってソフトスタート時間(カレントシェア)が設定されます。 $C_{SS}$ は 33nF 以下を使用してください。 $C_{SS}$ と内蔵 $5\mu$ A 定電流源によってコンバータのソフトスタート時間 $t_{SS}$ が決まります。 $C_{SS}[\mu F] = 6.25 \cdot t_{SS}[s]$ |

| 15             | VDD           | ロジック部分の電源入力です。VDD には VIN の +0.3/-0.5V の範囲の電圧を与えてください。                                                                                                                                                                                                                                                                                                  |

| 20, 21         | PGND1         | チャネル1のパワーステージ用の負極性電源入力です。                                                                                                                                                                                                                                                                                                                              |

| 18, 19         | LX1           | チャネル1のスイッチング・ノードです。VOUT1の出力インダクタの一方の端子に接続してください。                                                                                                                                                                                                                                                                                                       |

| 16, 17<br>2, 3 | VIN1,<br>VIN2 | 電源入力です。電源グラウンドとの間に 22µF のセラミック・コンデンサをチャネルごとに接続してください。                                                                                                                                                                                                                                                                                                  |

| 25             | PAD           | 適切な電気的特性を得るために、エキスポーズド・パッドは SGND に接続してください。また、放熱性能を<br>最大限に高めるために、パッドを実装するランドにはできるだけ多くのサーマルビアを設けてください。                                                                                                                                                                                                                                                 |

### 注文情報

| 部品番号 (Note 2、3)        | マーキング     | 温度範囲(℃)          | パッケージ(鉛フリー)   | パッケージの外形図 |  |  |  |

|------------------------|-----------|------------------|---------------|-----------|--|--|--|

| ISL8036IRZ             | 80 36IRZ  | -40 <b>~</b> +85 | 24 Ld 4x4 QFN | L24.4x4D  |  |  |  |

| ISL8036IRZ-T (Note 1)  | 80 36IRZ  | -40 ~ +85        | 24 Ld 4x4 QFN | L24.4x4D  |  |  |  |

| ISL8036AIRZ            | 80 36AIRZ | -40 <b>~</b> +85 | 24 Ld 4x4 QFN | L24.4x4D  |  |  |  |

| ISL8036AIRZ-T (Note 1) | 80 36AIRZ | -40 <b>~</b> +85 | 24 Ld 4x4 QFN | L24.4x4D  |  |  |  |

| ISL8036CRSHEVAL1Z      | 評価用ボード    | 評価用ボード           |               |           |  |  |  |

| ISL8036DUALEVAL1Z      | 評価用ボード    |                  |               |           |  |  |  |

| ISL8036ACRSHEVAL1Z     | 評価用ボード    |                  |               |           |  |  |  |

| ISL8036ADUALEVAL1Z     | 評価用ボード    |                  |               |           |  |  |  |

#### Note:

- 1. リールの詳細仕様については、テクニカル・ブリーフ <u>TB347</u> を参照してください。

- 2. これら鉛フリーのプラスチック・パッケージ製品には、専用の鉛フリー素材、モールド素材、ダイ・アタッチ素材を採用するとともに、端子には亜鉛 100%の梨地メッキとアニーリングを実施しています (RoHS 指令に準拠するとともに SnPb ハンダ付け作業と鉛フリーハンダ付け作業とも互換性のある e3 端子仕上げ)。インターシルの鉛フリー製品は鉛フリー・ピークリフロー温度で MSL 分類に対応し、この仕様は IPC/JEDEC J STD-020 の鉛フリー要件と同等か上回るものです。

- 3. 湿度感受性レベル (MSL) については ISL8036 または ISL8036A のデバイス情報ページを参照してください。MSL の詳細については テクニカル ブリーフ TB363 を参照してください。

## ISL8036, ISL8036A

## 目次

| 絶対最大定格 (SGND 基準 )                           | . 8 |

|---------------------------------------------|-----|

| 温度情報                                        | . 8 |

| 推奨動作条件                                      | . 8 |

| 電気的特性                                       | . 8 |

| ISL8036 のデュアル PWM 動作時の代表的な動作特性              | 10  |

| ISL8036A のデュアル PWM 動作時の代表的な動作特性             | 15  |

| ISL8036 のカレントシェア PWM 動作時の代表的な動作特性           | 17  |

| ISL8036A のカレントシェア PWM 動作時の代表的な動作特性          | 21  |

| 動作の概要                                       | 22  |

| PWM 制御方式                                    | 22  |

| 外部同期制御出力カレントシェア                             |     |

|                                             |     |

| パワーグッド (PG)                                 | 23  |

| アンダーボルテージ・ロックアウト (UVLO)                     |     |

| イネーブル                                       |     |

| ソフトスタート<br>放電モード(ソフトストップ)                   |     |

| パワー MOSFET                                  |     |

| 100%デューティサイクル                               |     |

| サーマル・シャットダウン                                |     |

| アプリケーション情報                                  | 23  |

| ルン・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |     |

| 出力電圧の設定・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

| 入力コンデンサの選択                                  |     |

| プリント基板のレイアウト設計指針                            | 24  |

| 改訂履歴                                        | 25  |

| 製品                                          | 25  |

| パッケージナ注図                                    | 26  |

#### 絶対最大定格 (SGND 基準)

| VIN1、VIN2、VDD0.3V~6.5V (DC) または 7V (20ms)                      |

|----------------------------------------------------------------|

| LX1、LX23V/(10ns) / -1.5V (100ns) / -0.3V (DC) $\sim$ 6.5V (DC) |

| または7V (20ms)/8.5V(10ns)                                        |

| EN1, EN2, PG1, PG2, SYNC, SS0.3V $\sim$ +6.5V                  |

| FB1、FB2、COMP0.3V $\sim$ +2.7V                                  |

| NC. $-0.3V \sim +0.3V$                                         |

| ESD 定格                                                         |

| 人体モデル (JESD22-A114 に従い試験)4kV                                   |

| デバイス帯電モデル (JESD22-C101E に従い試験)2kV                              |

| 機械モデル (JESD22-A115 に従い試験)300V                                  |

| ラッチアップ (JESD78、Class 2、Level A に従い試験)100mA                     |

| ·                                                              |

#### 温度情報

| 熱抵抗(代表値)                                    | θJA ( °C /W) | θJC ( °C /W)    |

|---------------------------------------------|--------------|-----------------|

| 24 Ld 4×4 QFN (Note 4、 5)                   | 36           | 2               |

| ジャンクション温度範囲                                 |              | 55 °C ~ +150 °C |

| 保存温度範囲                                      | 6            | 55 °C ~ +150 °C |

| 周囲温度範囲                                      |              | 40 °C∼ +85 °C   |

| 鉛フリー・リフロープロファイル                             | 以下           | の URL を参照       |

| http://www.intersil.com/pbfree/Pb-FreeRefle | ow.asp       |                 |

#### 推奨動作条件

| VIN 電源電圧範囲     | $\dots 2.85V \sim 6V$ |

|----------------|-----------------------|

| チャネルあたりの負荷電流範囲 | 0A ~ 3A               |

| 周囲温度範囲         |                       |

注意:過度に長い期間にわたって最大定格点または最大定格付近でデバイスを動作させないでください。そのような動作条件を課すと製品の信頼性に影響が及ぶ恐れがあるとともに、保証の対象とはならない可能性があります。

#### Note:

- 4.  $\theta$ JA はデバイスを放熱効率の高い試験基板に実装し、自由大気中で測定した値です。詳細はテクニカル・ブルーフ <u>TB379</u> を参照してください。

- 5.  $\theta$ JC の測定における「ケース温度」位置は、パッケージ下面のエキスポーズド金属パッドの中心です。

電気的特性 特記のない限り、各仕様値は以下の条件にて測定しています。

特記のない限り、 $T_A=-40$   $\mathbb{C}\sim+85$   $\mathbb{C}$ 、 $V_{IN}=3.6V$ 、EN1=EN2=VDD、 $L=1.5\mu H$ 、 $C1=C2=C4=2\times22\mu F$ 、 $I_{OUT1}=I_{OUT2}=0A\sim3A$ 。代表値は  $T_A=+25$   $\mathbb{C}$ における値です。太字のリミット値は動作温度範囲である -40  $\mathbb{C}\sim+85$   $\mathbb{C}$ に対して適用されます。

| PARAMETER                          | SYMBOL            | TEST CONDITIONS                                                              | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS         |

|------------------------------------|-------------------|------------------------------------------------------------------------------|-----------------|------|-----------------|---------------|

| INPUT SUPPLY                       | 1                 |                                                                              | <u>'</u>        |      |                 |               |

| VIN Undervoltage Lockout Threshold | V <sub>UVLO</sub> | Rising                                                                       |                 | 2.5  | 2.85            | V             |

|                                    |                   | Hysteresis                                                                   | 50              | 100  |                 | mV            |

| Quiescent Supply Current           | I <sub>VDD</sub>  | SYNC = VDD, EN1 = EN2 = VDD,<br>F <sub>S</sub> = 1MHz, no load at the output |                 | 15   | 40              | mA            |

|                                    |                   | F <sub>S</sub> = 2.5MHz, no load at the output                               |                 | 30   | 70              | mA            |

| Shutdown Supply Current            | I <sub>SD</sub>   | V <sub>DD</sub> = 6V, EN1 = EN2 = SGND                                       |                 | 8    | 20              | μA            |

| OUTPUT REGULATION                  | •                 |                                                                              |                 |      |                 | •             |

| FB1, FB2 Regulation Voltage        | $V_{FB}$          |                                                                              | 0.790           | 8.0  | 0.810           | V             |

| FB1, FB2 Bias Current              | I <sub>FB</sub>   | VFB = 0.75V                                                                  |                 | 0.1  |                 | μA            |

| Load Regulation                    |                   | SYNC = VDD, output load from 0A to 6A                                        |                 | 2    |                 | mV/A          |

| Line Regulation                    |                   | $V_{IN} = V_{O} + 0.5V \text{ to 6V (minimal 2.85V)}$                        |                 | 0.1  |                 | %/V           |

| Soft-start Ramp Time Cycle         |                   | SS = VDD                                                                     |                 | 1.5  |                 | ms            |

| Soft-start Charging Current        | I <sub>SS</sub>   |                                                                              | 4               | 5    | 6               | μA            |

| COMPENSATION                       |                   |                                                                              |                 |      |                 |               |

| Error Amplifier Trans-Conductance  |                   | SS = VDD                                                                     |                 | 20   |                 | μ <b>A</b> /V |

|                                    |                   | SS with Capacitor                                                            |                 | 100  |                 | μΑ/V          |

| Trans-resistance                   | RT                |                                                                              | 0.180           | 0.2  | 0.220           | Ω             |

| Trans-resistance Matching          | RT_match          |                                                                              | -0.03           |      | +0.03           | Ω             |

| OVERCURRENT PROTECTION             | •                 |                                                                              |                 |      |                 | •             |

| Dynamic Current Limit ON-time      | tocon             |                                                                              |                 | 17   |                 | Clock pulses  |

| Dynamic Current Limit OFF-time     | tocoff            |                                                                              |                 | 8    |                 | SS cycle      |

| Positive Peak Overcurrent Limit    | I <sub>poc1</sub> |                                                                              | 4.1             | 4.8  | 5.5             | Α             |

|                                    | I <sub>poc2</sub> |                                                                              | 4.1             | 4.8  | 5.5             | Α             |

| Negative Peak Overcurrent Limit    | I <sub>noc1</sub> |                                                                              | -3.5            | -2.5 | -1.5            | Α             |

|                                    | I <sub>noc2</sub> |                                                                              | -3.5            | -2.5 | -1.5            | Α             |

FN6853.3 2012 年 8 月 17 日

### ISL8036, ISL8036A

電気的特性 特記のない限り、各仕様値は以下の条件にて測定しています。

特記のない限り、 $T_A=-40$   $\mathbb{C}\sim+85$   $\mathbb{C}$ 、 $V_{\rm IN}=3.6$ V、 $\mathrm{EN1}=\mathrm{EN2}=\mathrm{VDD}$ 、 $\mathrm{L}=1.5\mu\mathrm{H}$ 、 $\mathrm{C1}=\mathrm{C2}=\mathrm{C4}=2\times22\mu\mathrm{F}$ 、 $\mathrm{I}_{\rm OUT1}=\mathrm{I}_{\rm OUT2}=0$ A  $\sim$  3A。 代表値は  $T_A=+25$   $\mathbb{C}$ における値です。**太字のリミット値は動作温度範囲である -40**  $\mathbb{C}\sim+85$   $\mathbb{C}$ に対して適用されます。(続き)

| PARAMETER                                   | SYMBOL            | TEST CONDITIONS                                | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|---------------------------------------------|-------------------|------------------------------------------------|-----------------|------|-----------------|-------|

| LX1, LX2                                    |                   |                                                | l .             |      | L               |       |

| P-Channel MOSFET ON-Resistance              |                   | V <sub>IN</sub> = 6V, I <sub>O</sub> = 200mA   |                 | 50   | 75              | mΩ    |

|                                             |                   | V <sub>IN</sub> = 2.7V, I <sub>O</sub> = 200mA |                 | 70   | 100             | mΩ    |

| N-Channel MOSFET ON-Resistance              |                   | V <sub>IN</sub> = 6V, I <sub>O</sub> = 200mA   |                 | 50   | 75              | mΩ    |

|                                             |                   | V <sub>IN</sub> = 2.7V, I <sub>O</sub> = 200mA |                 | 70   | 100             | mΩ    |

| LX_ Maximum Duty Cycle                      |                   |                                                |                 | 100  |                 | %     |

| PWM Switching Frequency                     | F <sub>S</sub>    | ISL8036                                        | 0.88            | 1.1  | 1.32            | MHz   |

|                                             |                   | ISL8036A                                       | 2.15            | 2.5  | 2.85            | MHz   |

| Synchronization Frequency Range             | F <sub>SYNC</sub> | ISL8036 (Note 7)                               | 2.64            |      | 6               | MHz   |

| Channel 1 to Channel 2 Phase Shift          |                   | Rising edge to rising edge timing              |                 | 180  |                 | 0     |

| LX Minimum On Time                          |                   | SYNC = High (PWM mode)                         |                 |      | 140             | ns    |

| Soft Discharge Resistance                   | R <sub>DIS</sub>  | EN = LOW                                       | 80              | 100  | 120             | Ω     |

| LX Leakage Current                          |                   | Pulled up to 6V                                |                 | 0.1  | 1               | μΑ    |

| PG1, PG2                                    | 1                 |                                                |                 |      | 1               |       |

| Output Low Voltage                          |                   | Sinking 1mA, VFB = 0.7V                        |                 |      | 0.3             | V     |

| PG Pin Leakage Current                      |                   | PG = V <sub>IN</sub> = 6V                      |                 | 0.01 | 0.1             | μA    |

| Internal PGOOD Low Rising<br>Threshold      |                   | Percentage of nominal regulation voltage       | 89.5            | 92   | 94.5            | %     |

| Internal PGOOD Low Falling<br>Threshold     |                   | Percentage of nominal regulation voltage       | 85              | 88   | 91              | %     |

| Delay Time (Rising Edge)                    |                   | Time from VOUT_ reached regulation             |                 | 1    |                 | ms    |

| Internal PGOOD Delay Time<br>(Falling Edge) |                   |                                                |                 | 7    | 10              | μs    |

| EN1, EN2, SYNC                              | II.               |                                                |                 |      |                 |       |

| Logic Input Low                             |                   |                                                |                 |      | 0.4             | V     |

| Logic Input High                            |                   |                                                | 1.5             |      |                 | V     |

| SYNC Logic Input Leakage Current            | I <sub>SYNC</sub> | Pulled up to 6V                                |                 | 0.1  | 1               | μA    |

| Enable Logic Input Leakage Current          | I <sub>EN</sub>   | Pulled up to 6V                                |                 | 0.1  | 1               | μA    |

| Thermal Shutdown                            |                   |                                                |                 | 150  |                 | °C    |

| Thermal Shutdown Hysteresis                 |                   |                                                |                 | 25   |                 | °C    |

#### Note:

<sup>6.</sup> MIN パラメータと MAX パラメータは、特記のない限り、+25 ℃で全数試験を行っています。温度リミットは特性評価によって得ており、製造時試験は行っていません。

<sup>7.</sup> スイッチング・チャネルあたりの動作周波数は、SYNC 周波数の 1/2 の周波数になります。

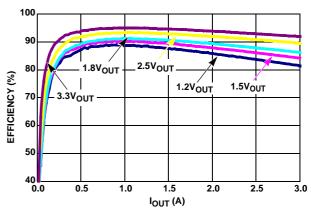

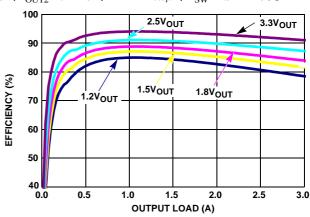

図 4. 効率 vs 負荷電流、V<sub>IN</sub> = 3.3V、T<sub>A</sub> = +25°C

図 5. 効率 vs 負荷電流、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25°C

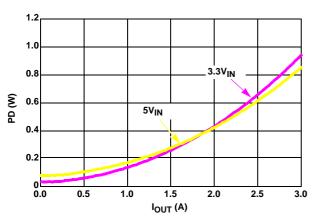

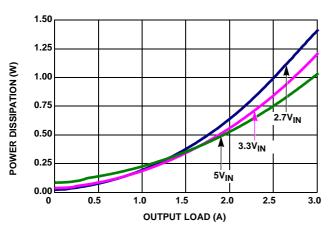

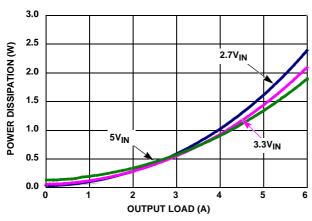

図 6. 電力損失 vs 負荷電流、V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +25°C

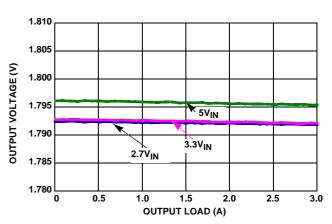

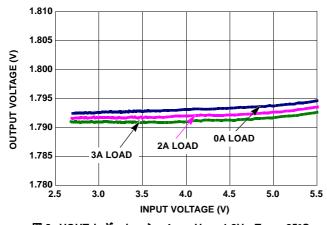

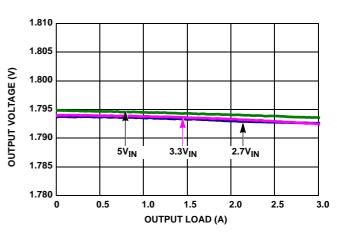

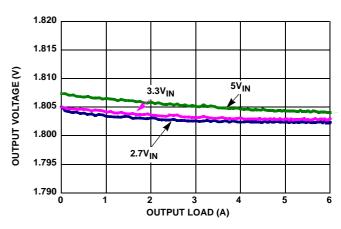

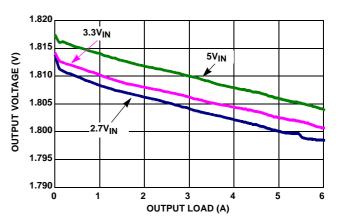

図 7. V<sub>OUT</sub> レギュレーション vs 負荷電流、1.8V、T<sub>A</sub> = +25°C

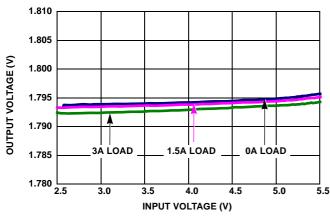

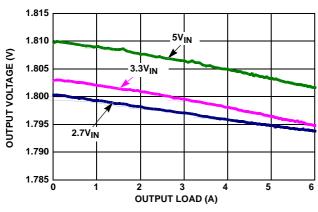

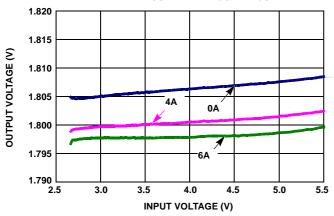

図 8. VOUT レギュレーション vs  $V_{IN}$ 、1.8V、 $T_A$  = +25°C

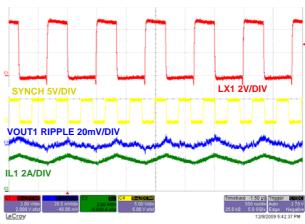

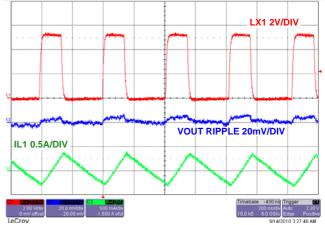

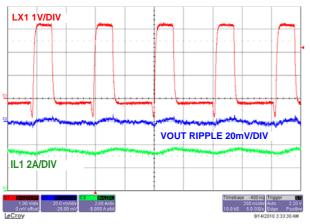

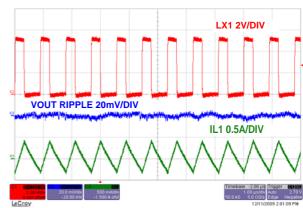

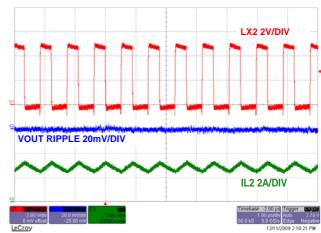

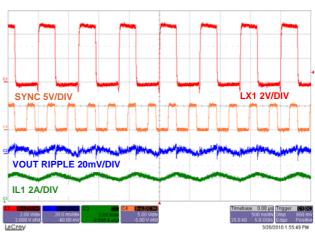

図 9. 無負荷時の安定状態動作、チャネル 1

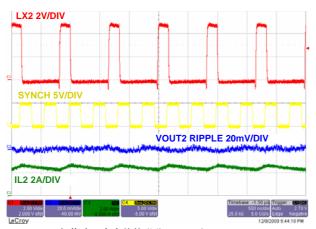

図 10. 無負荷時の安定状態動作、チャネル 2

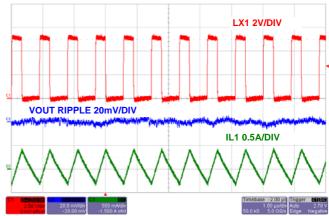

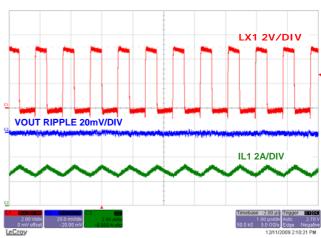

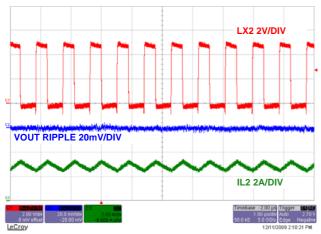

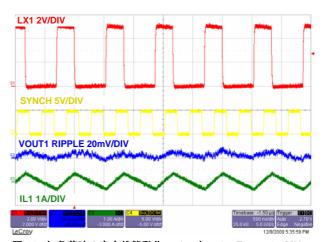

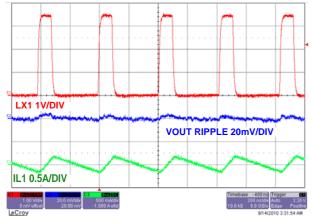

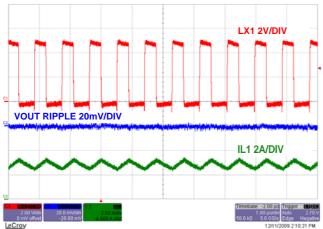

図 11. フル負荷時の安定状態動作、チャネル 1

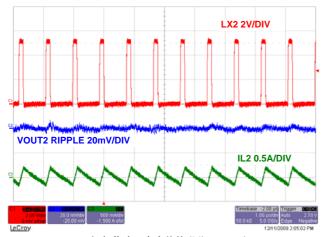

図 12. フル負荷時の安定状態動作、チャネル 2

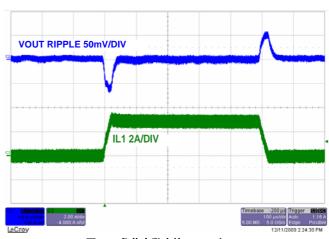

図 13. 負荷変動応答、チャネル 1

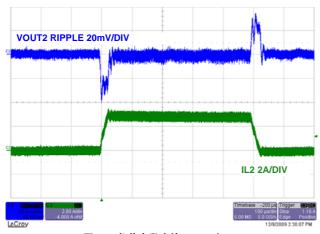

図 14. 負荷変動応答、チャネル 2

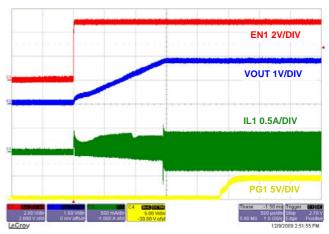

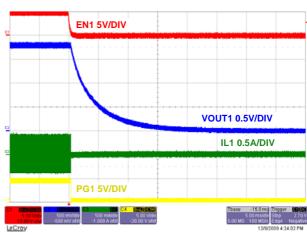

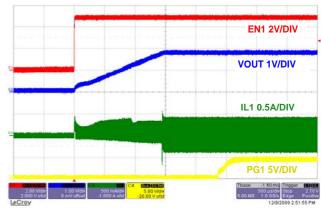

図 15. 無負荷時のソフトスタート、チャネル 1

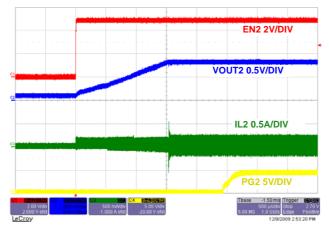

図 16. 無負荷時のソフトスタート、チャネル 2

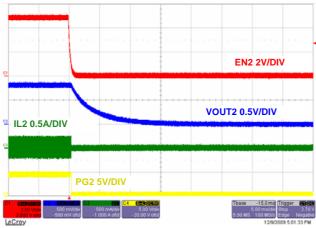

図 17. フル負荷時のソフトスタート、チャネル 1

図 18. フル負荷時のソフトスタート、チャネル 2

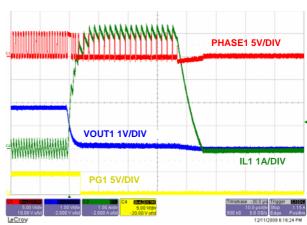

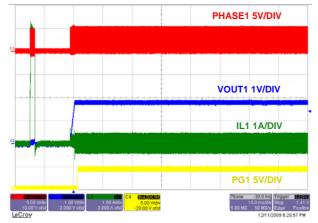

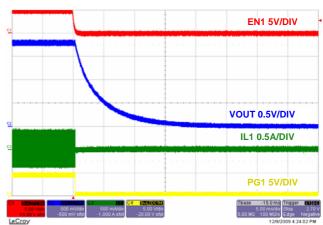

図 19. ソフト放電シャットダウン、チャネル1

図 20. ソフト放電シャットダウン、チャネル 2

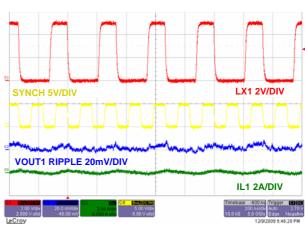

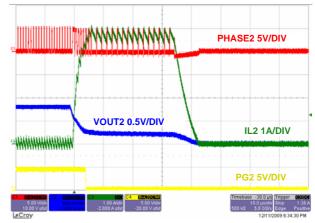

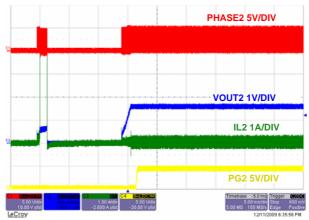

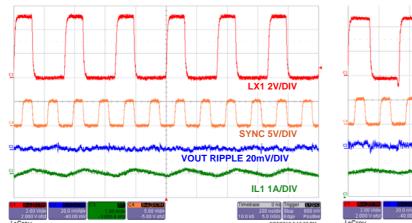

図 21. 無負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 2.4MHz

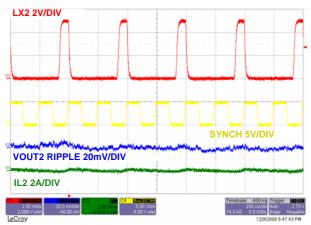

図 22. 無負荷時の安定状態動作、チャネル 2、F<sub>SW</sub> = 2.4MHz

図 23. フル負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 2.4MHz

図 24. フル負荷時の安定状態動作、チャネル 2、F<sub>SW</sub> = 2.4MHz

図 25. 無負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 6MHz

図 26. 無負荷時の安定状態動作、チャネル 2、F<sub>SW</sub> = 5MHz

図 27. 出力短絡、チャネル 1

図 28. 出力短絡からの復帰 (hiccup モードから通常モードへ)、 チャネル 1

図 29. 出力短絡、チャネル 2

図 30. 出力短絡からの復帰 (hiccup モードから通常モードへ )、チャネル 2

特記のない限り、動作条件は  $V_{OUT1}$  = 1.8V、 $V_{OUT2}$  = 0.8V、 $I_{OUT1}$  = 0.A  $\sim$  3A、 $I_{OUT2}$  = 0.A  $\sim$  3A、 $L_1$  =  $L_2$  = 0.6 $\mu$ H、 $F_{SW}$  = 2.5MHz です。

図 31. 効率 vs 負荷電流、チャネル 1、V<sub>IN</sub> = 3.3V、 T<sub>A</sub> = +25 <sup>℃</sup>

図 32. 効率 vs 負荷電流、チャネル 1、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

図 33. 電力損失 vs 負荷電流、チャネル 1、V<sub>OUT</sub> = 1.8V、 T<sub>A</sub> = +25 ℃

図 34. V<sub>OUT</sub> レギュレーション vs 負荷電流、チャネル 1、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +25 ℃

図 35. V<sub>OUT</sub> レギュレーション vs V<sub>IN</sub>、チャネル 1、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +25 <sup>°</sup>C

図 36. 無負荷時の安定状態動作、チャネル 1

図 37. 無負荷時の安定状態動作、チャネル 2

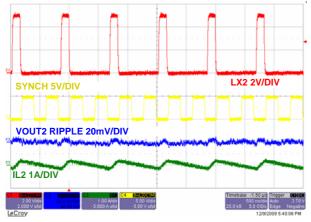

図 38. フル負荷時の安定状態動作、チャネル1

図 39. フル負荷時の安定状態動作、チャネル 2

図 40. 負荷変動応答、チャネル1

図 41. 負荷変動応答、チャネル 2

特記のない限り、動作条件は  $V_{OUT}$  = 1.8V、  $I_{OUT1}$  +  $I_{OUT2}$  = 0A  $\sim$  6A、  $F_{SW}$  = 1MHz です。

図 42. 効率 vs 負荷電流、V<sub>IN</sub> = 3.3V、T<sub>A</sub> = +25 ℃

図 43. 効率 vs 負荷電流、V<sub>IN</sub> = 5V、T<sub>A</sub> = +25 ℃

図 44. 電力損失 vs 負荷電流、V<sub>OUT</sub> = 1.8V、T<sub>A</sub>= +25 ℃

図 45. V<sub>OUT</sub> レギュレーション vs 負荷電流、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +25 ℃

図 46. V<sub>OUT</sub> レギュレーション vs 負荷電流、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = -40°C

図 47. V<sub>OUT</sub> レギュレーション vs 負荷電流、 V<sub>OUT</sub> = 1.8V、T<sub>A</sub> = +85°C

特記のない限り、動作条件は  $V_{OUT}$  = 1.8V、 $I_{OUT1}$  +  $I_{OUT2}$  = 0A  $\sim$  6A、 $F_{SW}$  = 1MHz です。( **続き** )

図 48. V<sub>OUT</sub> レギュレーション vs V<sub>IN</sub>、T<sub>A</sub> = +25 ℃

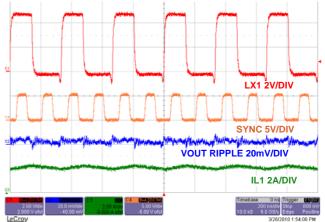

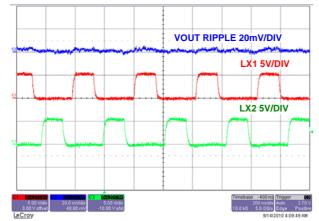

図 49. 無負荷時の安定状態動作、チャネル1

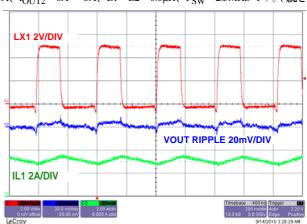

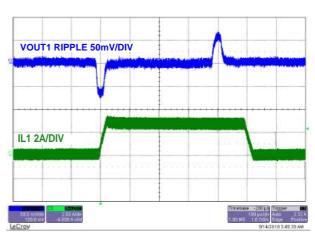

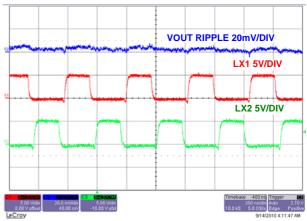

図 50. フル負荷時の安定状態動作、チャネル 1

図 51. フル負荷時の安定状態動作、チャネル 2

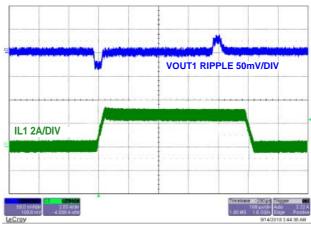

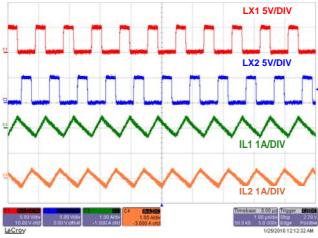

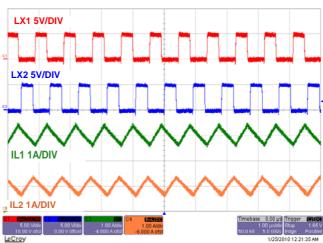

図 52. 無負荷時の安定状態動作、チャネル 1 とチャネル 2

図 53. フル負荷時の安定状態動作、チャネル 1 とチャネル 2

特記のない限り、動作条件は  $V_{OUT}$  = 1.8V、 $I_{OUT1}$  +  $I_{OUT2}$  = 0A  $\sim$  6A、 $F_{SW}$  = 1MHz です。( **続き** )

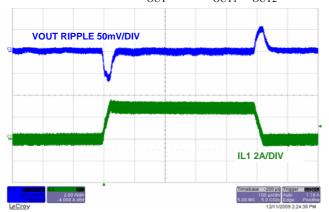

図 54. 負荷変動応答、チャネル1

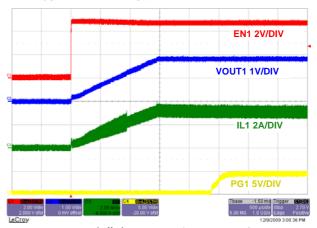

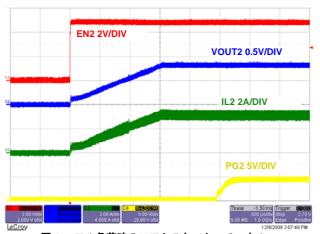

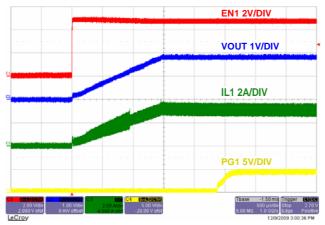

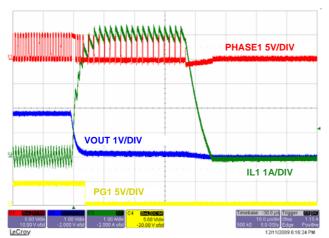

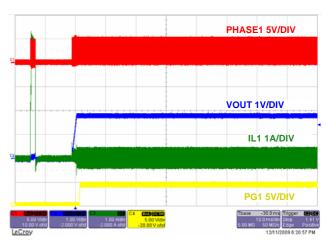

図 55. 無負荷時のソフトスタート、チャネル1

図 56. フル負荷時のソフトスタート、チャネル1

図 57. ソフト放電シャットダウン、チャネル1

図 58. 無負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 3MHz

図 59. フル負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 3MHz

特記のない限り、動作条件は  $V_{OUT}$  = 1.8V、 $I_{OUT1}$  +  $I_{OUT2}$  = 0A  $\sim$  6A、 $F_{SW}$  = 1MHz です。( **続き** )

図 60. 無負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 6MHz

図 61. フル負荷時の安定状態動作、チャネル 1、F<sub>SW</sub> = 6MHz

図 62. 出力短絡、チャネル1

図 63. 出力短絡からの復帰 (hiccup モードから通常モードへ )、 チャネル 1

特記のない限り、動作条件は  $V_{OUT}$  = 1.8V、 $I_{OUT1}$  +  $I_{OUT2}$  = 0A  $\sim$  6A、L1 = L2 = 0.6 $\mu$ H、 $F_{SW}$  = 2.5MHz です。

図 64. 無負荷時の安定状態動作

図 65. フル 6A 負荷時の安定状態動作

### 動作の概要

ISL8036 と ISL8036A は、バッテリ駆動アプリケーションやモバイル・アプリケーションに最適な、定格 3A のデュアル出力またはカレントシェアによる6A出力が可能な降圧スイッチング・レギュレータです。負荷が重い条件下で、1MHz (ISL8036)または 2.5MHz (ISL8036A)の一定周波数で動作します。2 系統のチャネルは 180° 異なる位相で動作します。レギュレータがシャットダウンしているときの電源電流はわずか 8μA です。

#### PWM 制御方式

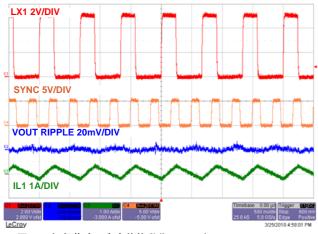

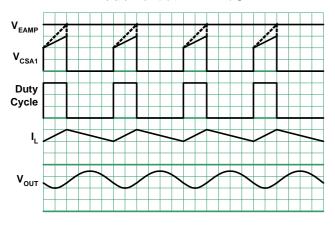

SYNC ピンに High (1.5V 以上)を与えると、負荷電流に関わらず、コンバータは次のサイクルから PWM モードに移行します。4ページの「内部ブロック図」と以下の図 66 の波形に示すように、ISL8036/ISL8036A の各チャネルともに電流モードのパルス幅変調 (PWM) 制御方式を採用し、高速な負荷変動応答とパルス単位での電流制限を実現しています。コンバータ回路の電流ループは、発振回路、PWM コンパレータ COMP、カレントシェア回路、ループ安定性を維持する傾き補償回路で構成されます。また、電流センス回路は、Pチャネル MOSFET のオン抵抗と、電流センスアンプ CSA1 とで構成されます。電流センス回路のゲインは代表値で 0.2V/Aです。電流ループの制御リファレンス信号は、電圧ループ内の誤差アンプ EAMP で生成しています。

PWM動作は発振回路のクロックによって始まります。Pチャネル MOSFET は PWM サイクルの開始時にターンオンし、MOSFET の電流は上昇を始めます。電流アンプ CSA1 (チャネル 2 は CSA2) と、補償傾き信号 ( $0.46V/\mu s$ ) の和が電流ループの制御リファレンスに達すると、P チャネル MOSFET をターンオフし、かつ、N チャネル MOSFET をターンオンするように、PWM コンパレータ COMP は PWM ロジックに信号を送出します。N チャネル MOSFET は PWM サイクルが終わるまでオンの状態を維持します。図 66 に PWM 動作中の動作波形の一例を示します。点線は補償傾き信号と電流センスアンプ CSA の出力の和を表しています。

図 66. PWM 動作波形

電流ループに与えるリファレンス電圧を制御して、出力電圧のレギュレーションを行っています。バンドギャップ回路から 0.8V リファレンス電圧が電圧制御ループに出力されます。帰還信号は  $FB_{-}$  ピンから与えられます。ソフトスタート・ブロックはスタートアップ時のみ動作し、詳細は後述します。誤差アンプはトランスコンダクタンス・アンプで、電圧誤差信号を電流出力へと変換します。電圧ループは 27pF と  $390k\Omega$

で構成される内蔵 RC ネットワークで補償されています。 EAMP出力の最大電圧はバンドギャップ電圧(1.172V)で高精 度にクランプされます。

#### 外部同期制御

動作周波数は SYNC ピンに与える最高 6MHz の外部信号に 同期させることができます。SYNC の先頭の立ち下がりエッ ジによって、チャネル 1 の PWM オンパルスの立ち上がり エッジがトリガされます。SYNC 信号の 2 番目の立ち下がり エッジによって、チャネル 2 の PWM オンパルスの立ち上が りエッジがトリガされます。このようにして両チャネルは 180° 異なる位相で動作します。

#### 出力カレントシェア

ISL8036/ISL8036A の 2 系統の出力を並列に接続すると、マルチフェーズ動作になり 6A 出力が得られます。カレントシェアを行うにはFBピンと COMPピンをそれぞれ互いに結線します。チャネル 1 とチャネル 2 は位相が 180° 異なる状態で動作します。カレントシェア構成で動作させる場合は、ソフトスタートを外部で制御して、フル負荷時の適切なスタートアップを保証してください。カレントシェア・モードで 6A 出力を得るには、あらかじめ PWM モードをイネーブルにしておかなければなりません。なお、複数のレギュレータのFBピン、COMPピン、SSピンを互いに接続して並列構成にすれば、より大きな電流出力も得られます。カレントシェア動作では外部補償回路が必要です。

#### 過電流保護

チャネル1の負荷電流とチャネル2の負荷電流は、それぞれ CSA1と CSA2でモニタされます。図4に示すように、CSA 出力はOCP スレッショルド・ロジックを使いモニタして、過電流保護を実現しています。カレントシェア回路のPチャネル MOSFET 電流から CSA\_ 出力までのゲインは0.2V/Aです。 CSA1 出力が OCP スレッショルドに達すると、OCP コンパレータがトリップして即座に P チャネル MOSFET をターンオフします。このように過電流保護は、ハイサイド MOSFET を流れる電流をモニタすると、スイッチング・コンバータ回路を出力短絡から保護します。

過電流状態が検出されるとハイサイド MOSFET は即座にターンオフし、次のスイッチング・サイクルが始まるまでターンオンすることはありません。過電流状態が初めて検出されると、過電流状態フラグが Low から High にセットされるとともに、過電流状態フラグが Low から High にセットされます。続くサイクルでも過電流状態が検出されると過電流フォルト・カウントはインクリメントされます。17 サイクル連続して過電流フォルトが検出されると、レギュレータは過電流フォルト状態とみなしシャットダウンします。続いて、ソフトスタート8回分に相当する遅延ののち、hiccup モード(脈動動作)でのリスタートを試みます。ソフトスタート8回分の時間が経過すると、フォルト・カウンタはリセットされ、ソフトスタートがもう一度試みられます。過電流フォルト・カウンタが8に達する前に過電流状態が解消されると、過電流状態フラグはLowに戻ります。

負荷電流が負極性となり -2.5A に達すると、デバイスは負極性過電流保護状態に移行します。この時点ですべてのスイッチング動作は停止し、デバイスはハイ・インピーダンス・モードに入ると同時に、内蔵プルダウン FET によって公称

レギュレーション電圧になるまで出力を放電し、その後デバイスはリスタートします。

#### パワーグッド (PG)

チャネルごとのパワーグッド信号が用意されています。PG1 はチャネル1出力をモニタした信号で、PG2 はチャネル2出力をモニタした信号です。

オープンコレクタの  $PG_$  出力は、電源投入後に  $V_{OUT}$  が設定電圧に達したあとも、およそ 1ms にわたって Low を維持します。 $PG_$  出力は 1ms だけ遅延したパワーグッド信号と見なすこともできます。

#### アンダーボルテージ・ロックアウト (UVLO)

入力電圧がアンダーボルテージ・ロックアウト (UVLO) スレッショルドを下回ると、レギュレータはディスエーブル状態になります。

#### イネーブル

パワーアップ・シーケンスを行うには、イネーブル (EN) 入力を使って、レギュレータのイネーブルとディスエーブルを制御します。レギュレータがイネーブル状態になったあと、バンドギャップ・リファレンスの起動に代表値で 600 ps を要します。その後ソフトスタートが始まります。

#### ソフトスタート

ソフトスタートは、スタートアップ時の突入電流を抑える機能です。ソフトスタート機能によって、電圧ループと電流ループの両方に対して、ランプ・リファレンスの出力がブロックされます。インダクタ電流の立ち上がり速度と出力電圧の立ち上がり速度が制限されるため、出力電圧は制御された状態で上昇します。スタートアップが開始した直後、出力電圧は 0.5V 以下で、そのため PWM 動作周波数は通常の周波数の 1/2 に下がります。

スタートアップ時はPWMモードであっても電流をシンクできないので、ソフトスタート期間中はダイオード・エミュレーション・モードのような振る舞いを示します。

#### 放電モード(ソフトストップ)

シャットダウン・モードへの移行が発生したとき、または、 出力アンダーボルテージ・フォルトラッチがセットされたと き、出力は内蔵の  $100\Omega$  スイッチを介して PGND レベルに放 電されます。

#### パワー MOSFET

パワー MOSFET は最大限の効率が得られるように最適化されています。P チャネル MOSFET のオン抵抗は代表値で $50 m \Omega$ 、N チャネル MOSFET のオン抵抗は代表値で $50 m \Omega$  です。

#### 100%デューティサイクル

ISL8036/ISL8036A は、機器のバッテリ動作時間を最大限に確保できるように、100%デューティサイクル動作に対応しています。ISL8036 または ISL8036A が出力レギュレーションを維持できないレベルにまでバッテリ電圧が低下すると、レギュレータは P チャネル MOSFET を完全にターンオフします。100%デューティサイクル動作における最大ドロップアウト電圧は、負荷電流と P チャネル MOSFET のオン抵抗の積で求められます。

#### サーマル・シャットダウン

ISL8036/ISL8036A にはサーマル保護機能が内蔵されています。内部温度が +150 ℃に達するとレギュレータは完全にシャットダウンします。温度が+125℃にまで下がるとISL8036と ISL8036A はソフトスタート・サイクルを経て通常動作に復帰します。

### アプリケーション情報

#### 出カインダクタと出カコンデンサの選択

安定状態動作と過渡応答動作を考慮して、ISL8036 または ISL8036A の出力インダクタには 1.5μH を一般に使います。コンバータ全体のシステム性能を高めるためにこれ以外のインダクタンス値を使用してもかまいません。たとえば、出力電圧が 3.3V と高めのアプリケーションの場合、大きめのインダクタを使用するとインダクタ電流と出力電圧リップルの抑制が図れます。インダクタ・リップル電流は式 2 で表されます。

$$\Delta I = \frac{V_O \bullet \left(1 - \frac{V_O}{V_{IN}}\right)}{L \bullet f_S}$$

(£ 2)

インダクタの飽和電流定格はピーク電流よりも大きくなければなりません。ISL8036/ISL8036Aは代表値で4.8A以上のピーク電流に対して保護機能が働きます。したがって、最大出力電流を必要とするアプリケーションの場合で、飽和電流定格は4.8A以上が必要です。

ISL8036/ISL8036A は補償ネットワークを内蔵していますが、出力コンデンサの容量は出力電圧によって決定します。推奨品は X5R または X7R タイプのセラミック・コンデンサです。出力コンデンサの推奨最小容量を表 4 に示します。

表 4. 出力コンデンサ容量と VOUT

| V <sub>OUT</sub> (V) | C <sub>OUT</sub><br>(µF) | L<br>(μH) |

|----------------------|--------------------------|-----------|

| 0.8                  | 2 x 22                   | 1.0~2.2   |

| 1.2                  | 2 x 22                   | 1.0~2.2   |

| 1.6                  | 2 x 22                   | 1.0~2.2   |

| 1.8                  | 2 x 22                   | 1.0~3.3   |

| 2.5                  | 2 x 22                   | 1.0~3.3   |

| 3.3                  | 2 x 6.8                  | 1.0~4.7   |

| 3.6                  | 10                       | 1.0~4.7   |

表 4 に、コンバータ・システム全体の安定動作に必要な出力 コンデンサの最小容量値を、それぞれの出力電圧に対応させ て示しています。

#### 出力電圧の設定

レギュレータの出力電圧は外付けの抵抗分圧回路で設定します。この分圧回路は、内部リファレンス電圧を基準とする 出力電圧の比を定めて、誤差アンプの反転入力に帰還する役割を担います。図2を参照してください。

レギュレータの所望の電圧から出力設定抵抗  $R_2$  (チャネル2 は  $R_5$ ) を選択します。帰還抵抗の抵抗値は一般に  $0\Omega$  から  $750k\Omega$  の範囲です。 $R_2=124k\Omega$  としたとき、 $R_3$  は次のよう に求められます。

FN6853.3 2012 年 8 月 17 日

$$R_3 = \frac{R_2 \times 0.8 \text{V}}{V_{\text{OUT}} - 0.8 \text{V}}$$

(£ 3)

適切な性能を得るために、 $R_2$  には並列に 12pF を接続してください。なお、出力電圧として 0.8V を得たい場合は、 $R_3$  を未実装とし、 $R_2$  を短絡してください。

#### 入力コンデンサの選択

入力コンデンサの主な機能は、寄生インダクタンスとのデカップリングと、スイッチング電流がバッテリ・レールに逆流しないようにフィルタすることです。入力コンデンサの選択にあたっては、スタートポイントとして、X5R または X7R タイプの  $22\mu F$  セラミック・コンデンサをチャネルあたり1 個設けてください。

#### プリント基板のレイアウト設計指針

設計したコンバータから所望の性能を得るには、プリント基 板のレイアウト設計がきわめて重要な役割を担います。 ISL8036/ISL8036A のパワーループは、出力インダクタ L、出 カコンデンサ C<sub>OUT1</sub> と C<sub>OUT2</sub>、LX ピン、PGND ピンで構 成されています。このパワーループをできるだけ小さく設計 する必要があるとともに、それらを接続しているトレースは 迂回させずに最短かつ幅広で設計してください。コンバータ のスイッチング・ノード LX ピンと、LX ピンに接続されて いるトレースは、多くのノイズを含んでいるため、電圧帰還 トレースはこれからできるだけ離してルーティングしてく ださい。FBネットワークはFBピンのできるだけ近くに配置 してください。SGNDは「一点アース」方式でPGNDに接続 してください。入力コンデンサは VIN ピンのできるだけ近 くに配置します。同様に、入力コンデンサのグラウンドと出 カコンデンサのグラウンドもできるだけ近くに配置します。 IC の発熱は主にサーマルパッドから拡散していきます。そ のため、サーマルパッドを実装するランドをできるだけ広く してください。また、EMI 性能を高めるにはベタグラウンド 層が有効です。放熱を高めるために、少なくとも5個以上の ビアをパッドのランド内に設けてください。

そのほかの製品については www.intersil.com/product\_tree/を参照してください。

インターシルは、www.intersil.com/design/quality/に記載の品質保証のとおり、ISO9000 品質システムに基づいて、製品の製造、組み立て、試験を行っています。

インターシルの製品は製品に関する情報のみを提供して販売されます。インターシルは、予告インターシルは、製品を販売するにあたって、製品情報のみを提供します。インターシルは、いかなる時点においても、予告なしに、回路設計、ソフトウェア、仕様を変更する権利を有します。製品を購入されるお客様は、必ず、データシートが最新であることをご確認くださいますようお願いいたします。インターシルは正確かつ信頼に足る情報を提供できるよう努めていますが、その使用に関して、インターシルおよび関連子会社は責を負いません。また、その使用に関して、第三者が所有する特許または他の知的所有権の非侵害を保証するものではありません。インターシルおよび関連子会社が所有する特許の使用権を暗黙的または他の方法によって与えるものではありません。

インターシルの会社概要については www.intersil.com をご覧ください。

intersil

#### 改訂履歴

この改訂履歴は参考情報として掲載するものであり、正確を期すように努めていますが、内容を保証するものではありません。 最新のデータシートについてはインターシルのウェブサイトをご覧ください。

| 日付            | レビジョン    | 変更点                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 18, 2012 | FN6853.3 | 「COMP ピンに以下の説明を追加。<br>デュアルモードとして動作させるときは、COMP ピンは NC としてください。この場合、内部補償回路が使われます。<br>SS ピンにソフトスタート・コンデンサが接続される場合 (VIN に接続しない場合)、外部補償回路が使われます。カレントシェアとして動作させるときには、COMP ピンに RC 回路を接続してください。6ページ SS ピンに以下の説明を追加。<br>SS ピンを VIN に接続したときのソフトスタート時間は、1.5ms になります。デュアルモード動作では、SS ピンを VIN に接続してください。カレントシェア動作では、SS ピンをコンデンサ C <sub>SS</sub> に接続し、外部補償回路を使用します。6ページの「注文情報」に以下の評価ボードを追加。ISL8036ACRSHEVAL1Z、ISL8036ADUALEVAL1Z、ISL8036CRSHEVAL1Z、ISL8036DUALEVAL1Z。 15ページ 図 33 のタイトルを訂正:タイトルの「1.8VIN」を「1.8VOUT」に変更。図34 のタイトルを訂正:タイトルの「1.8VIN」を「1.8VOUT」に変更。図35 のタイトルを訂正:タイトルの「1.8VIN」を「1.8VOUT」に変更。図35 のタイトルを訂正:タイトルの「1.8VIN」を「1.8VOUT」に変更。「35 のタイトルを訂正:タイトルの「1.8VIN」を「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。「1.8VOUT」に変更。 |

| 2011/10/14    | FN6853.2 | 1 ページの「関連ドキュメント」を追加。<br>8 ページ、「絶対最大定格」の<br>"LX1, LX21.5V (100ns)/-0.3V (DC) ~ 6.5V (DC) または 7V (20ms)" を<br>"LX1, LX23V/(10ns)/-1.5V (100ns)/-0.3V (DC) ~ 6.5V (DC) または 7V (20ms)/8.5V(10ns) " に変更。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2010/10/12    | FN6853.1 | 3 ページ、表 3 の ISL8036 の F <sub>SW</sub> を 1Hz から 1MHz に訂正。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2010/9/28     | FN6853.0 | 初版                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### 製品

インターシルは、高性能アナログ、ミクストシグナルおよびパワーマネジメント半導体の設計、製造で世界をリードする企業です。インターシルの製品は、通信、コンピューティング、コンシューマ、産業用機器の分野で特に急速な成長を遂げている市場向けに開発されています。製品ファミリの詳細は、<u>www.intersil.com/product\_tree/</u>をご覧ください。

ISL8036、ISL8036A に関するアプリケーション情報、関連ドキュメント、関連部品は、www.intersil.com 内の ISL8036 と ISL8036A のページを参照してください。

本データシートに関するご意見は<u>www.intersil.com/askourstaff</u>へお寄せください。

信頼性に関するデータは rel.intersil.com/reports/search.php を参照してください。

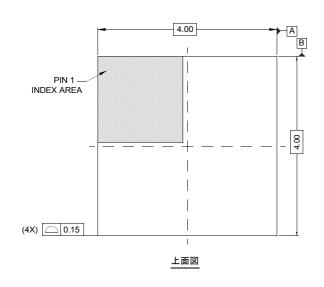

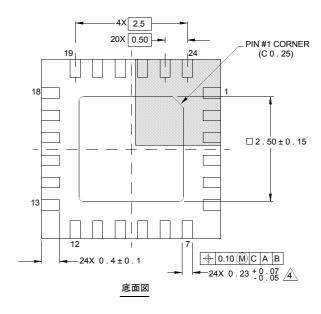

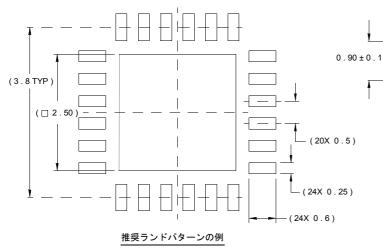

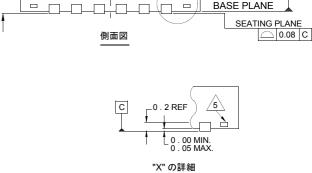

### パッケージ寸法図

#### L24.4x4D

# 24 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 2. 10/06

#### NOTE:

- 寸法の単位は mm です。

()内の寸法は参考値です。

- 2. 寸法と公差は ASME Y14.5m-1994 に従っています。

- 3. 寸法 b は金属端子に適用され、端子先端から 0.15mm  $\sim$  0.30mm の範囲で計測した値です。

- 4. 特記のない限り、公差は DECIMAL ±0.05 です

- 5. タイバー(示されている場合)は非機能性です。

- 6. 1 ピンの識別子はオプションですが、表示されているゾーン内 に配置されます。1 ピンの識別子はモールドまたはマーキング で示されます。

"X" の詳細

0.10 C

С