# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

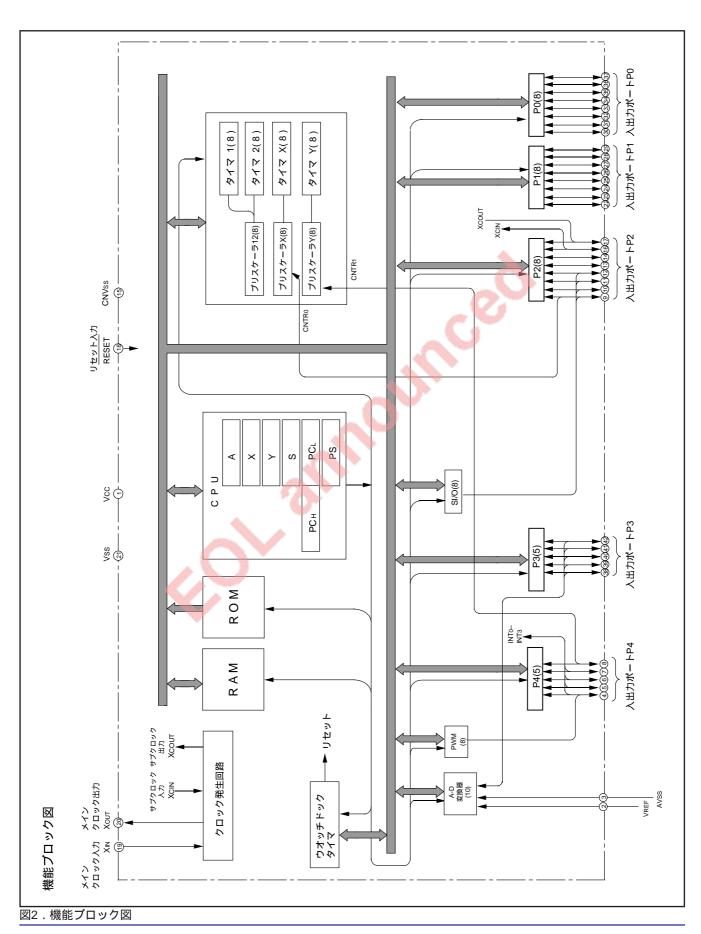

# 3850グループ

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

RJJ03B0051-0101Z Rev.1.01 2003.07.30

#### 概要

3850グループは、740ファミリコアを採用した8ビットマイクロコンピュータです。

シリアルI/O、8ビットタイマ、A-D変換器を内蔵しており、家電、OA機器に最適です。

## 特長

| J LX    |          |             |

|---------|----------|-------------|

| 基本機械語句  | 命令       | 71          |

| 命令実行時間  | <b>写</b> | 0.5 µ s     |

|         | ( 最短命令、  | 発振周波数8MHz時) |

| メモリ容量   | ROM      | 8~24Kバイト    |

|         | RAM      | 512~640バイト  |

| プログラマス  | ブル入出力ポート | 34本         |

| 割り込み    |          | 14要因、14ベクタ  |

| タイマ     |          | 8ビット×4      |

| シリアル1/0 |          | 8ビット×1      |

|         | (UART    | 又はクロック同期形)  |

| PWM     |          | 8ビット×1      |

| A-D変換器. | 10ビッ     | ト分解能×5チャネル  |

| クロック発生回路2回路内蔵<br>( セラミック共振子又は水晶発振子外付け) |

|----------------------------------------|

| ウオッチドッグタイマ16ビット×1                      |

| 電源電圧                                   |

| 高速モード時 4.0~5.5V                        |

| (発振周波数8MHz時)                           |

| 中速モード時2.7~5.5V                         |

| (発振周波数8MHz時、中速モード選択時 )                 |

| 低速モード時2.7~5.5V                         |

| (発振周波数32kHz時)                          |

| 消費電力                                   |

| 高速モード時34mW                             |

| (発振周波数8MHz時、電源電圧5V)                    |

| 低速モード時 60 µ W                          |

| (発振周波数32kHz時、電源電圧3V)                   |

| 動作周囲温度 20~85                           |

|                                        |

| <del>-</del>                           |

応用

OA機器、FA機器、家電、民生機器など

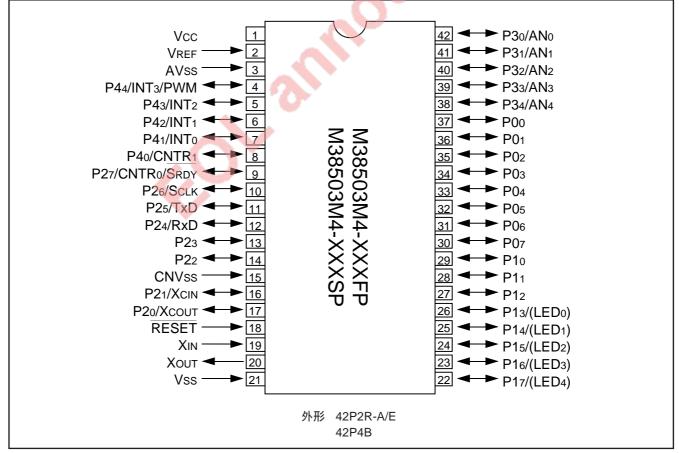

図1. M38503M4-XXXFP/SPのピン接続図

# 端子の機能説明

# 表1. 端子の機能説明

| 端子名                    | 名 称       | 機能                                                                                 | ポート以外の機能                      |  |  |  |  |  |

|------------------------|-----------|------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|

| Vcc,Vss                | 電源入力      | Vccに2.7~5.5V , Vssに0Vを印加します。                                                       |                               |  |  |  |  |  |

| CNVss                  | CNVss     | チップの動作モードを制御する端子で通常はVssに接続                                                         | 売します。                         |  |  |  |  |  |

| RESET                  | リセット入力    | アクティブ L 'のリセット入力端子です。                                                              | フティプ' L 'のリセット入力端子です。         |  |  |  |  |  |

| XIN                    | メインクロック入力 | クロック発生回路の入出力端子で、XINとXOUTの間にセラミック共振子又は水晶発振子                                         |                               |  |  |  |  |  |

| Хоит                   | メインクロック出力 | ↑を接続します。外部クロック使用時にはクロック発振減<br>↑は開放にします。                                            | 原をXIN端子に接続し、XOUT端子            |  |  |  |  |  |

| P00 ~ P07              | 入出力ポートP0  | 8ビットの入出力ポートです。プログラムにより、ビッ<br>す。CMOS入力レベルで,出力形式はCMOS3ステー                            |                               |  |  |  |  |  |

| P10 ~ P17              | 入出力ポートP1  | M38503E4/M2/M4ではP13~P17の5ビットが、M3850がLED駆動出力用の大電流出力が可能です。                           | 04E6/M6ではP10~P17の8ビット         |  |  |  |  |  |

| P20/XCOUT<br>P21/XCIN  | 入出力ポートP2  | 8ビットの入出力ポートです。プログラムにより、<br>ビット単位で入出力の指定が可能です。入力レベル<br>は、CMOS入力レベルです。出力形式はP20, P21, | サブクロック発生入出力端子<br>(共振子を接続します。) |  |  |  |  |  |

| P22<br>P23             |           | P24~P27がCMOS3ステートです。                                                               |                               |  |  |  |  |  |

| P24/RxD<br>P25/TxD     |           | P22, P23はNチャネルオープンドレインです。                                                          | シリアルI/O機能端子                   |  |  |  |  |  |

| P26/SCLK               |           |                                                                                    |                               |  |  |  |  |  |

| P27/CNTR0/<br>SRDY     |           | 70                                                                                 | シリアルI/O機能端子<br>/ タイマX機能端子     |  |  |  |  |  |

| P30/AN0 ~<br>P34/AN4   | 入出力ポートP3  | P0とほぼ同等の機能を持った8ビットの入出力ポートです。CMOS入力レベルで、出力形式はCMOS3ステートです。                           | A-D変換器入力端子                    |  |  |  |  |  |

| P40/CNTR1              | 入出力ポートP4  | POとほぼ同等の機能を持った8ビットの入出力ポート                                                          | タイマY機能端子                      |  |  |  |  |  |

| P41/INT0 ~<br>P43/INT2 |           | です。CMOS入力レベルで、出力形式はCMOS3ステートです。                                                    | 割り込み入力端子                      |  |  |  |  |  |

| P44/INT3/<br>PWM       |           |                                                                                    | 割り込み入力端子<br>PWM出力端子           |  |  |  |  |  |

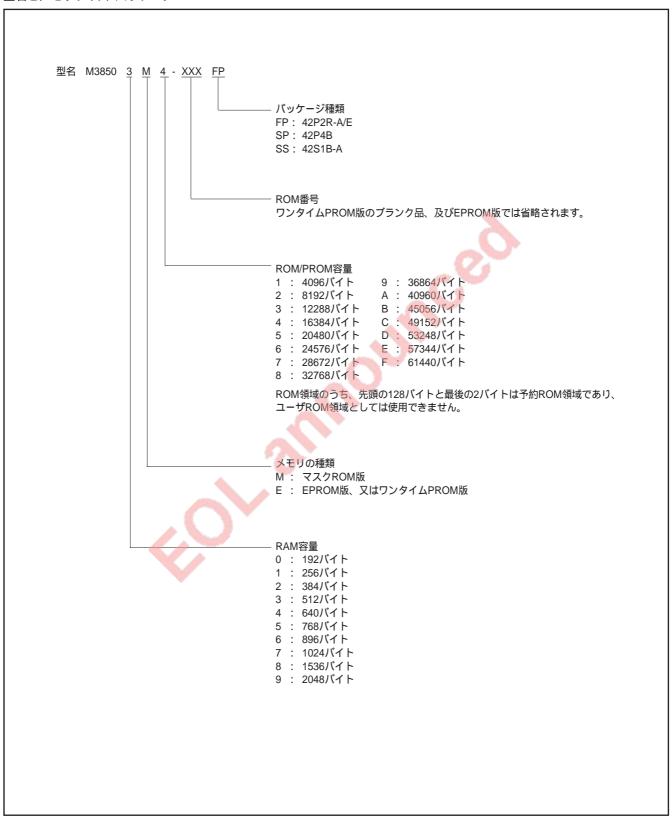

## 型名とメモリサイズ・パッケージ

図3.型名とメモリサイズ・パッケージ

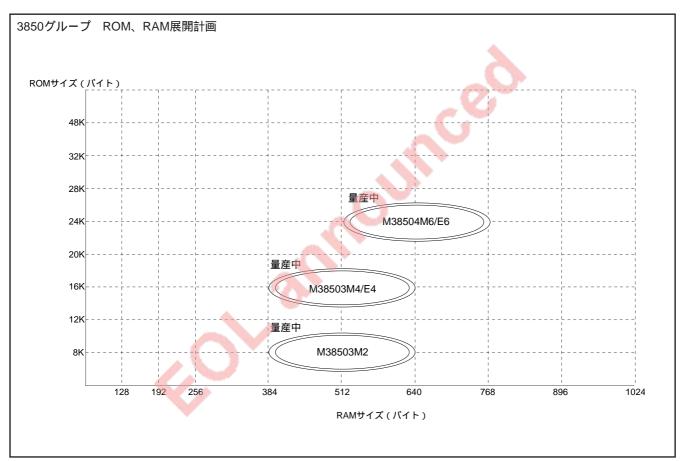

## グループ展開

3850グループは次のような展開を計画しています。

## メモリの種類

マスクROM版、ワンタイムPROM版のサポート

## メモリ容量

| ROM/PROM容量 8K~24Kバイ | 1        |

|---------------------|----------|

| RAM容量512~640バイ      | <b> </b> |

## パッケージ

図4.ROM及びRAM展開計画

現在サポートを行っている製品を下記に示します。

表2. サポート製品一覧 2003年7月現在

| 製品型名           | ROM容量(バイト)<br>( )内はユーザROM容量 | RAM容量<br>(バイト) | パッケージ     | 備考                |

|----------------|-----------------------------|----------------|-----------|-------------------|

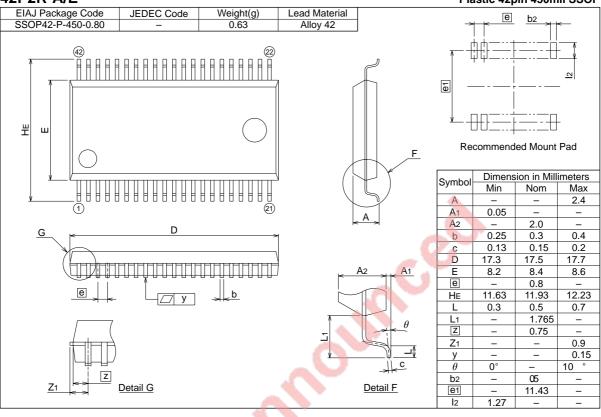

| M38503M2-XXXSP | 8192                        | 512            | 42P4B     | マスクROM版           |

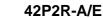

| M38503M2-XXXFP | (8062)                      | 312            | 42P2R-A/E | マスクROM版           |

| M38503M4-XXXSP |                             |                |           | マスクROM版           |

| M38503E4-XXXSP |                             |                | 42P4B     | ワンタイムPROM版        |

| M38503E4SP     |                             |                |           | ワンタイムPROM版(ブランク品) |

| M38503E4SS     | 16384<br>(16254)            | 512            | 42S1B-A   | EPROM版            |

| M38503M4-XXXFP | (10=0.)                     |                | 42P2R-A/E | マスクROM版           |

| M38503E4-XXXFP |                             |                |           | ワンタイムPROM版        |

| M38503E4FP     |                             |                |           | ワンタイムPROM版(ブランク品) |

| M38504M6-XXXSP |                             |                |           | マスクROM版           |

| M38504E6-XXXSP |                             |                | 42P4B     | ワンタイムPROM版        |

| M38504E6SP     | 0.4570                      |                |           | ワンタイムPROM版(ブランク品) |

| M38504E6SS     | 24576<br>(24446)            | 640            | 42S1B-A   | EPROM版            |

| M38504M6-XXXFP |                             |                |           | マスクROM版           |

| M38504E6-XXXFP |                             |                | 42P2R-A/E | ワンタイムPROM版        |

| M38504E6FP     |                             |                |           | ワンタイムPROM版(プランク品) |

#### 機能ブロック動作説明

## 中央演算処理装置( CPU )

3850グループは740ファミリ共通のCPUを持っています。各命令の動作については740ファミリアドレッシングモード及び機械語命令一覧表又は740ファミリソフトウエアマニュアルを参照ください。

品種に依存する命令については以下の通りです。

- 1. FST, SLW命令はありません。

- 2. MUL, DIV命令が使用可能です。

- 3. WIT命令が使用可能です。

- 4.STP命令が使用可能です。

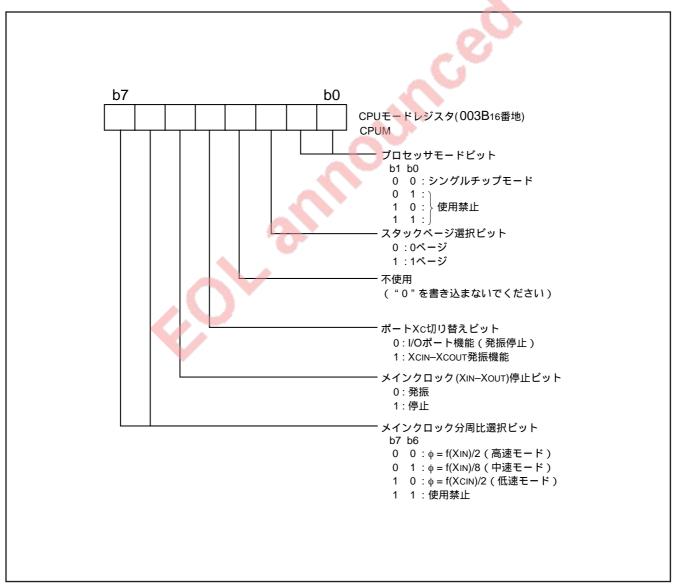

## 【CPUモードレジスタ】 CPUM

CPUモードレジスタには、スタックページ選択ビットなどが割り当てられています。

このレジスタは003B16番地に配置されています。

図5. CPUモードレジスタの構成

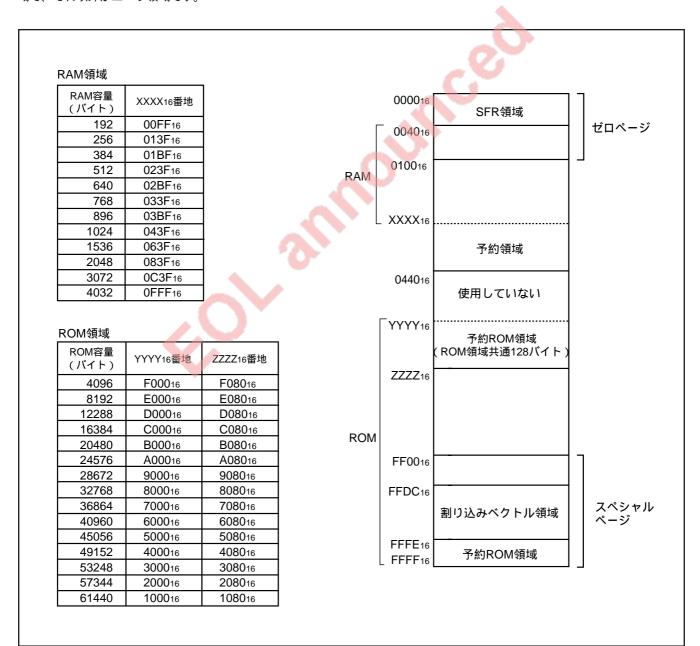

## メモリ

## SFR領域

ゼロページ内にあり、入出力ポート、タイマなどの制御レジスタが配置されています。

## RAM

データ格納、サブルーチン呼び出し及び割り込み時のス タックなどに使用します。

## **ROM**

先頭の128バイトと最後の2バイトは、製品検査用の予約領域で、それ以外がユーザ領域です。

## 割り込みベクトル領域

リセット及び割り込みのベクトル番地格納領域です。

#### ゼロページ

ゼロページアドレッシングモードを使用することにより、2語でアクセスできる領域です。

## スペシャルページ

スペシャルページアドレッシングモードを使用することにより、2語でアクセスできる領域です。

図6. メモリ配置図

| 000016 | ポートP0(P0)                | 002016             | プリスケーラ12(PRE12)         |

|--------|--------------------------|--------------------|-------------------------|

| 000116 | ポートP0方向レジスタ(P0D)         | 002116             | タイマ1(T1)                |

| 000216 | ポートP1(P1)                | 002216             | タイマ2(T2)                |

| 000316 | ポートP1方向レジスタ(P1D)         | 002316             | タイマXYモードレジスタ(TM)        |

| 000416 | ポートP2(P2)                | 002416             | プリスケーラX(PREX)           |

| 000516 | ポートP2方向レジスタ(P2D)         | 002516             | タイマX(TX)                |

| 000616 | ポートP3(P3)                | 002616             | プリスケーラY(PREY)           |

| 000716 | ポートP3方向レジスタ(P3D)         | 002716             | タイマY(TY)                |

| 000816 | ポートP4(P4)                | 002816             | タイマカウントソース設定レジスタ(TCSS)  |

| 000916 | ポートP4方向レジスタ(P4D)         | 002916             |                         |

| 000A16 |                          | 002A <sub>16</sub> | <u> </u>                |

| 000B16 |                          | 002B16             | 予約 (注)                  |

| 000C16 |                          | 002C16             | 予約 (注)                  |

| 000D16 |                          | 002D16             | 予約 (注)                  |

| 000E16 |                          | 002E16             | 予約 (注)                  |

| 000F16 |                          | 002F16             | 予約 (注)                  |

| 001016 |                          | 003016             | 予約 (注)                  |

| 001116 |                          | 003116             | 予約 (注)                  |

| 001216 |                          | 003216             |                         |

| 001316 |                          | 003316             |                         |

| 001416 |                          | 003416             | AD/DA制御レジスタ(ADCON)      |

| 001516 | 予約 (注)                   | 003516             | A-D変換下位レジスタ1(ADL)       |

| 001616 | 予約 (注)                   | 003616             | A-D変換上位レジスタ1(ADH)       |

| 001716 | 予約 (注)                   | 003716             | 予約 (注)                  |

| 001816 | 送信/受信バッファレジスタ1(TB/RB)    | 003816             | MISRG                   |

| 001916 | シリアルI/Oステータスレジスタ(SIOSTS) | 003916             | ウォチドッグタイマ制御レジスタ(WDTCON) |

| 001A16 | シリアルI/O制御レジスタ(SIOCON)    | 003A16             | 割り込みエッジ選択レジスタ(INTEDGE)  |

| 001B16 | UART制御レジスタ(UARTCON)      | 003B16             | CPUモードレジスタ(CPUM)        |

| 001C16 | ボーレートジェネレータ(BRG)         | 003C16             | 割り込み要求レジスタ1(IREQ1)      |

| 001D16 | PWM制御レジスタ(PWMCON)        | 003D16             | 割り込み要求レジスタ2(IREQ2)      |

| 001E16 | PWMプリスケーラ(PREPWM)        | 003E16             | 割り込み制御レジスタ1(ICON1)      |

| 001F16 | PWMレジスタ(PWM)             | 003F16             | 割り込み制御レジスタ2(ICON2)      |

図7 . SFR( スペシャルファンクションレジスタ )メモリマップ

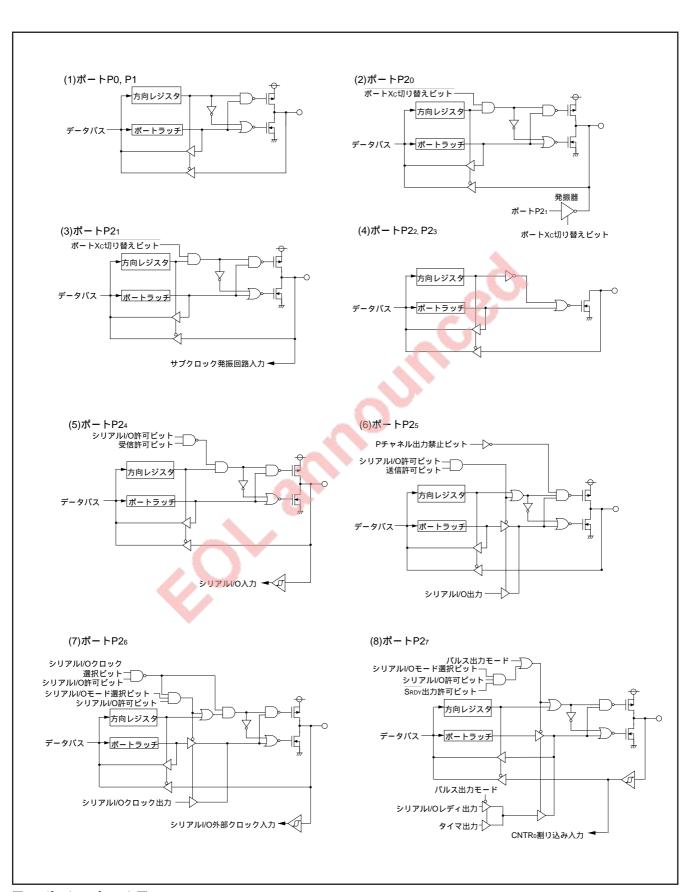

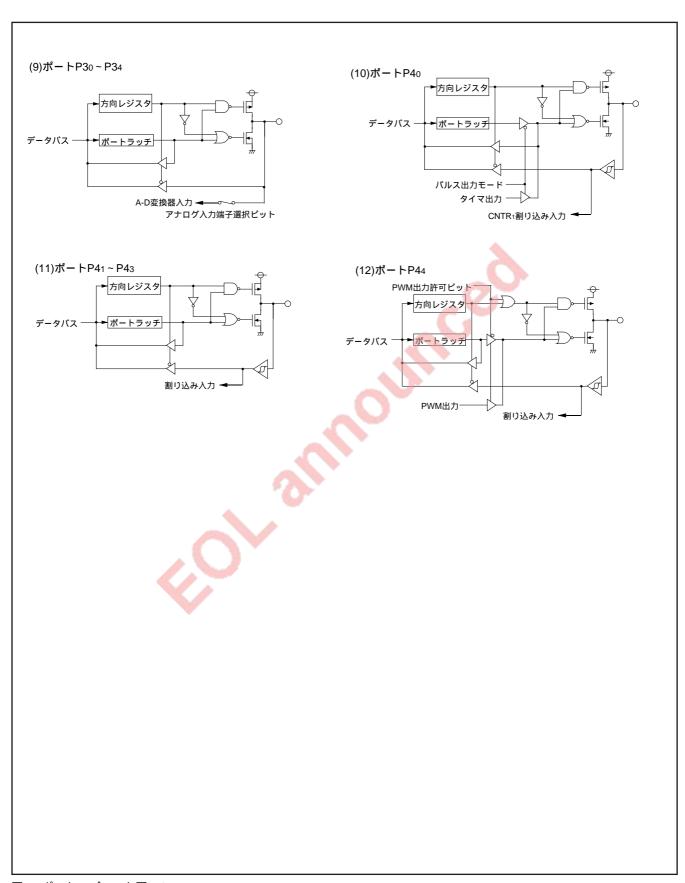

## 入出力ポート

入出力ポートは方向レジスタを持っており、入力ポートとして使用するか出力ポートとして使用するかビット単位に設定することが可能です。方向レジスタを"1"にセットするとその端子は出力ポートになります。"0"にクリアすると入力ポートになります。

出力ポートに設定されている端子から読み込んだ場合は、端子の値ではなくポートラッチの内容が読み込まれます。入力ポートに設定されている端子はフローティングとなり、端子の値を読み込むことができます。書き込んだ場合はポートラッチに書き込まれますが、端子はフローティングのままです

表3. 入出力ポートの機能一覧

| 端子名                    | 名 称   | 入出力   | 入出力形式                        | ポート以外の機能                  | 関連するSFR                               | 図番         |

|------------------------|-------|-------|------------------------------|---------------------------|---------------------------------------|------------|

| P00 ~ P07              | ポートP0 | 入出力   | CMOS入力レベル                    |                           |                                       | (1)        |

| P10 ~ P17              | ポートP1 | ビット単位 | CMOS3ステート出力                  |                           |                                       |            |

| P20/XCOUT,<br>P21/XCIN | ポートP2 |       |                              | サブクロック発振回路                | CPUモードレジスタ                            | (2)        |

| P22,<br>P23            |       |       | CMOS入力レベル<br>Nチャネルオープンドレイン出力 | 6                         |                                       | (4)        |

| P24/RXD,<br>P25/TXD    |       |       | CMOS入力レベル<br>CMOS3ステート出力     | シリアル/O機能入出力               | シリアルI/O制御<br>レジスタ                     | (5)<br>(6) |

| P26/SCLK               |       |       |                              | シリアルI/O機能入出力              | シリアルI/O制御<br>レジスタ                     | (7)        |

| P27/CNTRo/SRDY         |       |       |                              | シリアJV/O機能入出力<br>タイマX機能入出力 | シリアルI/O制御<br>レジスタ<br>タイマXYモードレジ<br>スタ | (8)        |

| P30/AN0 ~<br>P34/AN4   | ポートP3 |       |                              | A-D变換入力                   | A-D制御レジスタ                             | (9)        |

| P40/CNTR1              | ポートP4 |       |                              | タイマY機能入出力                 | タイマXYモードレジ<br>スタ                      | (10)       |

| P41/INT0 ~<br>P43/INT2 |       |       | 2                            | 外部割り込み入力                  | 割り込みエッジ選択<br>レジスタ                     | (11)       |

| P44/INT3/PWM           |       |       |                              | 外部割り込み入力<br>PWM出力         | 割り込みエッジ選択<br>レジスタ<br>PWM制御レジスタ        | (12)       |

図8.ポートのブロック図(1)

図9.ポートのブロック図(2)

#### 割り込み

割り込みはベクトル割り込みで、外部6要因、内部7要因、ソフトウエア1要因の14要因から発生することが可能です。

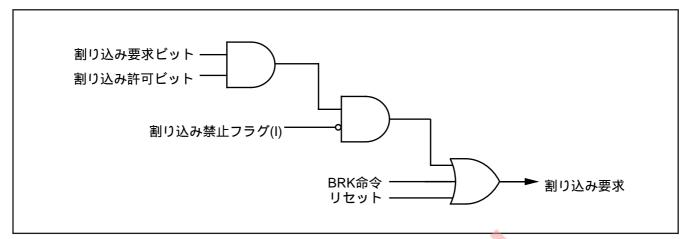

## ・割り込み制御

BRK命令割り込みを除く各割り込みは、割り込み要求ビットと割り込み許可ビットを持っており、割り込み禁止フラグの影響を受けます。割り込み許可ビット及び割り込み要求ビットが 1 "でかつ割り込み禁止フラグが 0 "のとき割り込みは受け付けられます。

割り込み要求ビットはプログラムでクリアできますが、 セットはできません。割り込み許可ビットはプログラムで セット、クリアできます。

リセットとBRK命令割り込みを禁止するフラグ又はビット はありません。これら以外の割り込みは割り込み禁止フラグ がセットされていると受け付けられません。

同時に複数の割り込み要求が発生した場合は、優先順位の高い割り込みが受け付けられます。

#### ・割り込み動作

割り込みを受け付けると、

- 1. プログラムカウンタとプロセッサステータスレジスタが 自動的に退避されます。

- 2. 割り込み禁止フラグがセットされ、割り込み要求ビットがクリアされます。

- 3. 割り込み飛び先番地がプログラムカウンタに入ります。

#### 注意事項

外部割り込み(INTo~INT3、CNTRo、CNTR1)のアクティブ エッジを切り替える際、割り込み要求ビットが 1 "になる場合 があります。

対象レジスタ:割り込みエッジ選択レジスタ(003A16番地) タイマXYモードレジスタ(002316番地)

これらの設定に同期した割り込み要求が不要な場合には、 以下の手順で設定してください。

- (1) 該当する割り込み許可ビットを"0(禁止)にする。

- (2)割り込みエッジ選択ビット(極性切り替えビットを設定する。

- (3) **一命令以上おいてから、該当する割り込み要求ビットを** "0"にする。

- (4) 該当する割り込み許可ビットを"1(許可)にする。

表4. 割り込みベクトル番地と優先順位

| \$4.233.7. #F.F.  | 優先 ベクトル番地(注 |        | 番地(注1)             | DU 022 - T-274 1 - 774         | /# +                  |  |

|-------------------|-------------|--------|--------------------|--------------------------------|-----------------------|--|

| 割り込み要因            | 順位          | 上位     | 下位                 | 割り込み要求発生条件                     | 備考                    |  |

| リセット(注2)          | 1           | FFFD16 | FFFC16             | リセット時                          | ノンマスカブル               |  |

| INT <sub>0</sub>  | 2           | FFFB16 | FFFA16             | INTo入力の立ち上がり又は<br>立ち下がりエッジ検出時  | 外部割り込み<br>(極性プログラマブル) |  |

| 予約                | 3           | FFF916 | FFF816             | 予約                             |                       |  |

| INT1              | 4           | FFF716 | FFF616             | INT1入力の立ち上がり又は<br>立ち下がりエッジ検出時  | 外部割り込み<br>(極性プログラマブル) |  |

| INT2              | 5           | FFF516 | FFF416             | INT2入力の立ち上がり又は<br>立ち下がりエッジ検出時  | 外部割り込み<br>(極性プログラマブル) |  |

| INT3              | 6           | FFF316 | FFF216             | INT3入力の立ち上がり又は<br>立ち下がりエッジ検出時  | 外部割り込み<br>(極性プログラマブル) |  |

| 予約                | 7           | FFF116 | FFF016             | 予約                             |                       |  |

| タイマX              | 8           | FFEF16 | FFEE16             | タイマXアンダフロー時                    |                       |  |

| タイマY              | 9           | FFED16 | FFEC16             | タイマYアンダフロー時                    |                       |  |

| タイマ1              | 10          | FFEB16 | FFEA <sub>16</sub> | タイマ 1 アンダフロー時                  | STP解除タイマアンダフロー        |  |

| タイマ 2             | 11          | FFE916 | FFE816             | タイマ2アンダフロー時                    |                       |  |

| シリアルI/O受信         | 12          | FFE716 | FFE616             | シリアルI/Oデータ受信完了時                | シリアルI/O選択時のみ有効        |  |

| シリアルI/O送信         | 13          | FFE516 | FFE416             | シリアルI/Oシフト終了時<br>又は送信バッファ空き時   | シリアルI/O選択時のみ有効        |  |

| CNTR <sub>0</sub> | 14          | FFE316 | FFE216             | CNTRo入力の立ち上がり又は<br>立ち下がりエッジ検出時 | 外部割り込み<br>(極性プログラマブル) |  |

| CNTR1             | 15          | FFE116 | FFE016             | CNTR1入力の立ち上がり又は<br>立ち下がりエッジ検出時 | 外部割り込み<br>(極性プログラマブル) |  |

| A-D変換             | 16          | FFDF16 | FFDE16             | A-D变換終了時                       |                       |  |

| BRK命令             | 17          | FFDD16 | FFDC16             | BRK命令実行時                       | ノンマスカブルソフトウエア割り込み     |  |

図10.割り込み制御図

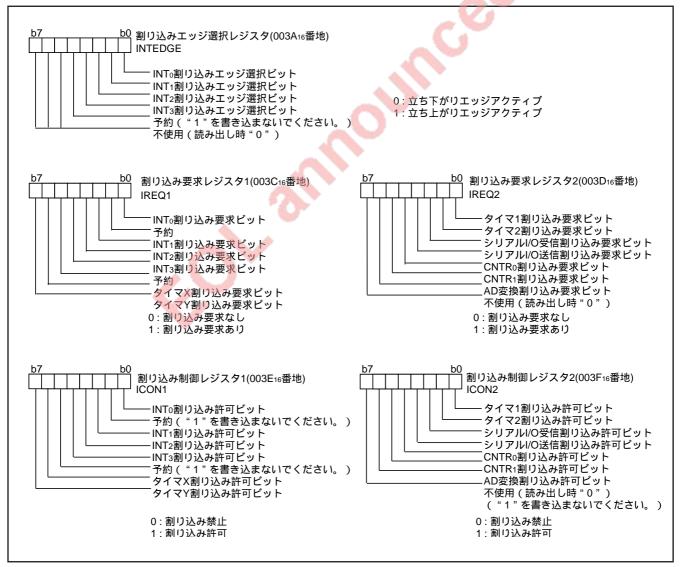

図11.割り込み関係レジスタの構成(1)

#### タイマ

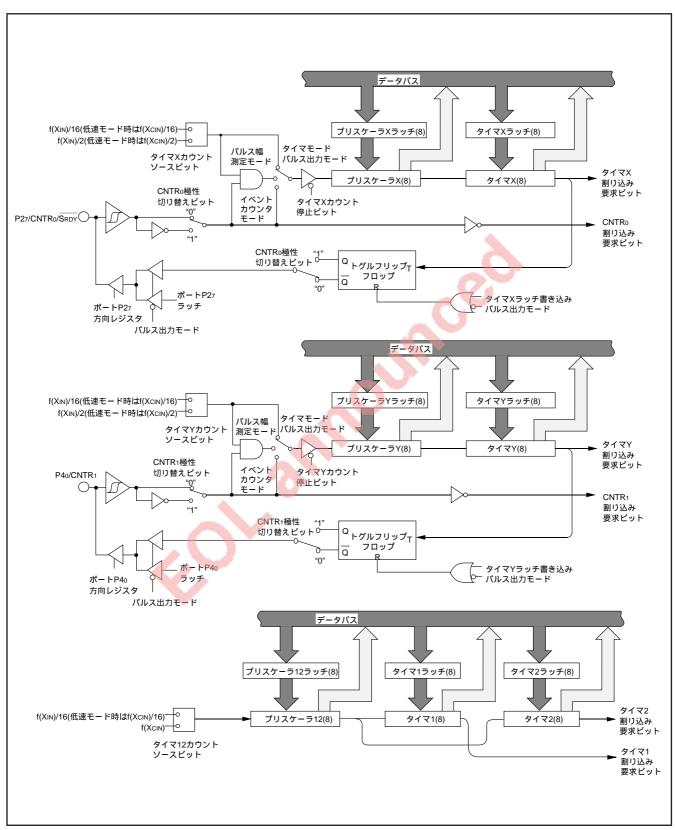

タイマはタイマX、タイマY、タイマ1及びタイマ2の4本あります。

すべてのタイマ及びプリスケーラの分周比は、タイマラッチ 又はプリスケーララッチの内容をnとすると1/(n+1)になります。

タイマはカウントダウン方式で、カウンタの内容が 0 "になった次のカウントパルスでアンダフローし、タイマラッチの内容が再びタイマにロードされます。またタイマがアンダフローすると各タイマに対応する割り込み要求ビットが 1 "にセットされます。

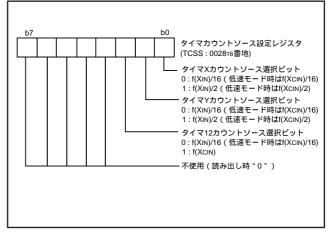

## タイマ1、タイマ2

プリスケーラ12は、タイマカウントソース選択ビットにより選ばれた信号をカウントします。タイマ1及びタイマ2は、常にプリスケーラの出力をカウントし、周期的に割り込み要求ビットをセットします。

#### タイマX、タイマY

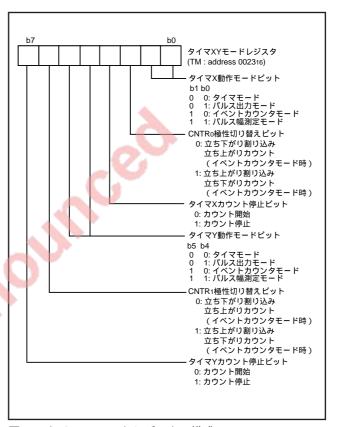

タイマX、タイマYはタイマXYモードレジスタを設定することにより、それぞれ4つの動作モードを選択することができます。

## (1)タイマモード

タイマカウントソース選択ビットにより選ばれた信号を力 ウントします。

#### (2)パルス出力モード

タイマカウントソース選択ビットにより選ばれた信号をカウントし、タイマの内容が 0 %になるたびに極性の反転する出力をCNTRo/CNTR1端子より出力します。CNTRo/CNTR1極性切り替えビットが 0 %ときは、CNTRo/CNTR1端子の出力は "H"出力から開始します。"1 %ときは、"L"出力から開始します。このモードを使用する場合はポートP27/ポートP40の方向レジスタを出力モードに設定してください。

## (3)イベントカウンタモード

CNTRo/CNTR1端子からの入力信号をカウントすることを除けばタイマモードと同じ動作をします。

CNTRo/CNTR1極性切り替えビットが"0"のときは、CNTRo/CNTR1端子の立ち上がりエッジを、"1"のときは立ち下がりエッジをカウントします。

#### (4)パルス幅測定モード

CNTRo/CNTR1極性切り替えビットが"0"のときは、CNTRo/CNTR1端子が"H"の期間、タイマカウントソース選択ビットにより選ばれた信号をカウントします。"1"のときは、"L"の期間、カウントします。

いずれのモードでも、タイマX/タイマYカウント停止ビットを"1"に設定することによりカウントを停止することが可能です。また、タイマがアンダフローするたびに割り込み要求ビットをセットします。

図12.タイマXYモードレジスタの構成

図13.タイマカウントソース設定レジスタ

## 注意事項

タイマ12カウントソース選択ビット及びタイマXカウントソース選択ビット、タイマYカウントソース選択ビットによりタイマのカウントソースを切り替えるとき、カウント入力信号に細いパルスが生じてタイマのカウント値が大きく変わることがあります。したがって、タイマのカウントソースを設定した後、プリスケーラ及びタイマに値を設定してください。

図14. タイマX, タイマY, タイマ1及びタイマ2のブロック図

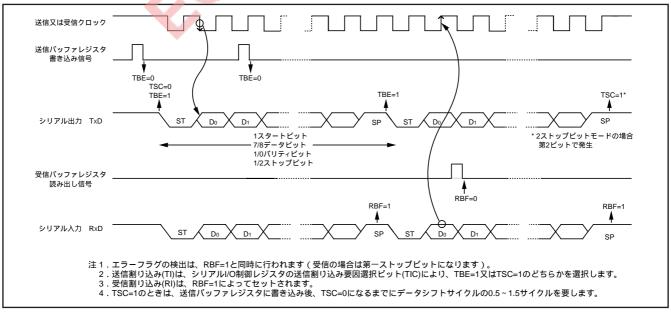

#### シリアル/(0

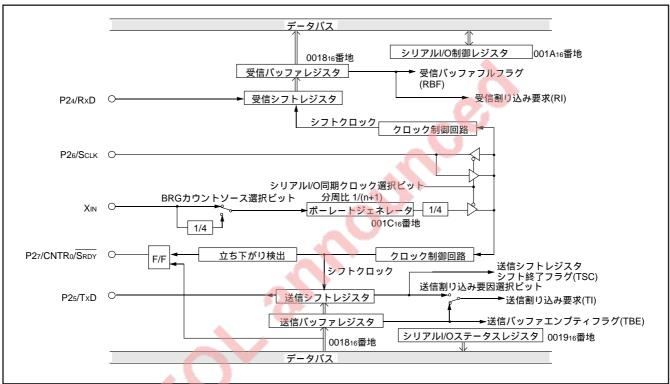

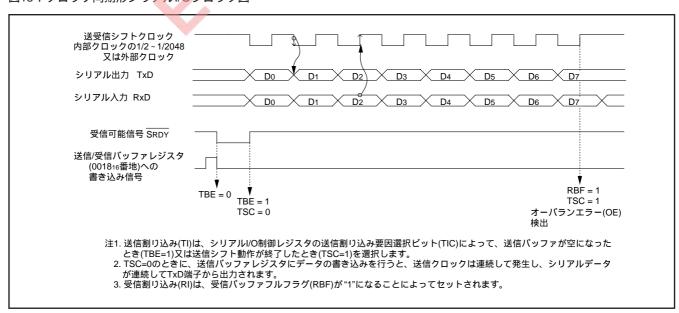

シリアルI/Oはクロック同期形、非同期形(UART)のどちらでも動作可能です。また、シリアルI/O動作時のボーレート発生専用タイマ(ボーレートジェネレータ)を備えています。

## (1) クロック同期形シリアル I/Oモード

シリアルI/O制御レジスタのモード選択ビットを"1"にする ことによってクロック同期形シリアルI/Oが選択されます。

クロック同期形シリアルI/Oでは、シリアルI/Oの動作クロックに、送信側マイコン、受信側マイコンとも同一のクロックを用います。動作クロックとして内部クロックを用いた場合、送/受信の開始は送信/受信バッファレジスタへの書き込み信号により行われます。

図15.クロック同期形シリアルI/Oブロック図

図16.クロック同期形シリアルI/O動作図

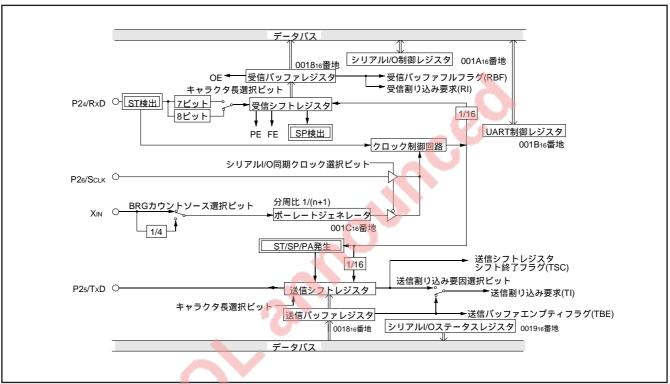

#### (2) 非同期形シリアルI/Q( UART )モード

シリアルI/O制御レジスタのシリアルI/Oモード選択ビット (b6)を 0 "にすることによってUARTが選択されます。

8つのシリアルデータ転送フォーマットが選択可能です。この転送フォーマットは送受信側で統一しておく必要があります。

シリアルデータの送信、受信を行う送信シフトレジスタ、

受信シフトレジスタにそれぞれのバッファレジスタを持っています(メモリ上の番地は同一)。シフトレジスタは直接読み書きすることができませんので、送信データの書き込み、受信データの読み出しはそれぞれのバッファレジスタに対して行います。また、これらのバッファレジスタによって次に送信すべきデータを書き込んでおいたり、2バイトの受信データを連続して受信することができます。

図17.UART形シリアルI/Oブロック図

図18. UART形シリアルI/O動作図

## 【送信バッファレジスタ/受信バッファレジスタ TB/RB

送信バッファレジスタと受信バッファレジスタは同じアドレスに配置されており、送信バッファレジスタは書き込み専用、受信バッファレジスタは読み出し専用です。また、キャラクタビット長が7ビットの場合、受信バッファレジスタに格納される受信データのMSBは"0"となります。

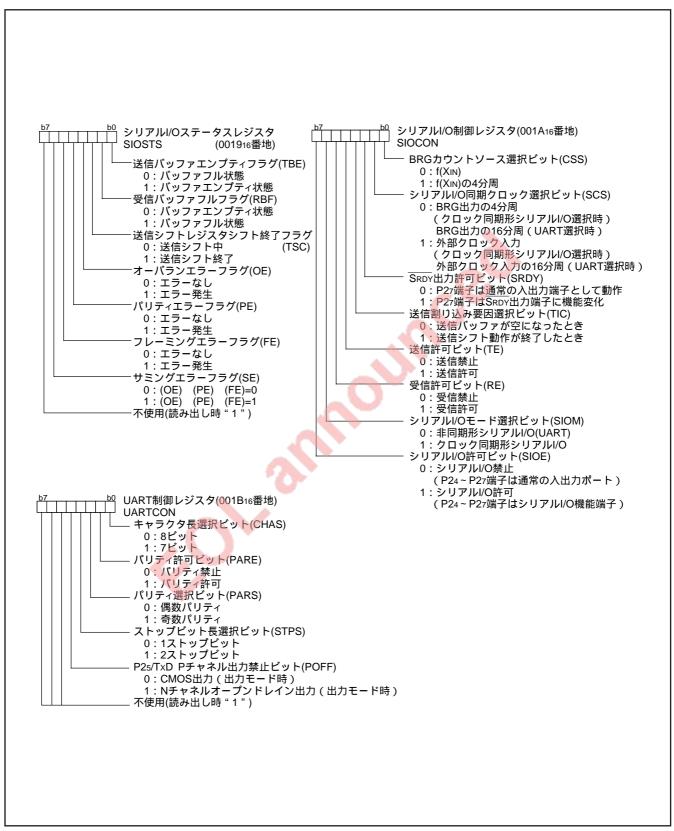

#### 【シリアルI/Oステータスレジスタ】SIOSTS

シリアルI/Oの動作状態を示すフラグ及び各種エラーフラグで構成された7ビットの読み出し専用レジスタです。ビット4~6の3ビットはUARTモード時のみ有効です。

受信バッファフルフラグは受信バッファレジスタを読み出すど 0 %にクリアされます。

エラー検出は、データが受信シフトレジスタから受信バッファレジスタに転送され、受信バッファフルフラグがセットされると同時に行われます。シリアルI/Oステータスレジスタへの書き込みですべてのエラーフラグ(OE、PE、FE、SE)がクリアされます。また、シリアルI/O許可ビット(b7)に0%を書き込むとエラーフラグを含む全てのステータスフラグが0%にクリアされます。

このレジスタのビット0からビット6はリセット時 0 に初期 化されますが、シリアルI/O制御レジスタの送信許可ビット (b4)を17にしたときビット2とビット0ば17になります。

## 【シリアルI/O制御レジスタ】SIOCON

シリアルI/O制御レジスタはシリアルI/Oの各種制御を行う8 ビットの選択ビットで構成されています。

## 【UART制御レジスタ】UARTCON

UART選択時有効な4ビットの制御ビットと1ビットの常に有効な制御ビットより構成された5ビットのレジスタです。このレジスタの内容でシリアルデータ送受信時のデータフォーマット、P25/TxD端子の出力形式などを設定します。

## 【ボーレートジェネレータ】BRG

シリアル転送のビットレートを決定します。

リロードレジスタを持った8ビットのカウンタで、値nを設定することにより、カウントソースを1/(n+1)の分周比で分周します。

#### 注意事項

シリアルI/Oの送信許可ビットを11にしたとき、シリアルI/O送信割り込み要求ビットが11になります。送信許可に同期した割り込み発生が不要な場合は、以下の手順で設定してください

- (1) シリアルI/O送信割り込み許可ビットを 0 (禁止)にする。

- (2) 送信許可ビットを"1"にする。

- (3) 一命令以上おいてから、シリアルI/O送信割り込み要求 ビットを'0'にする。

- (4) シリアルI/O送信割り込み許可ビットを1"(許可)にする。

図19.シリアルI/O関係レジスタの構成

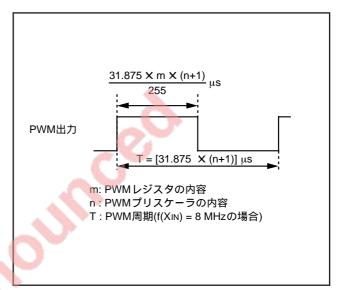

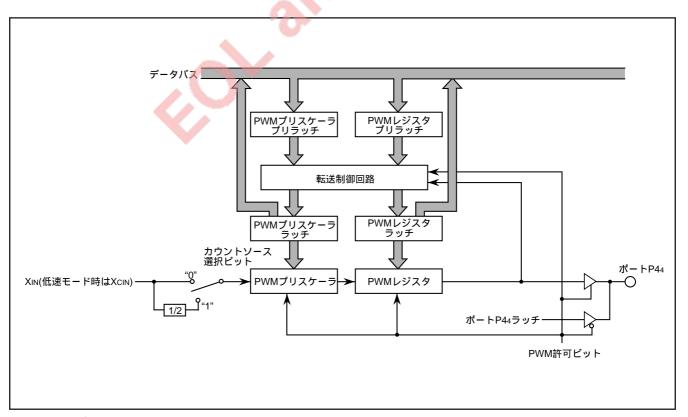

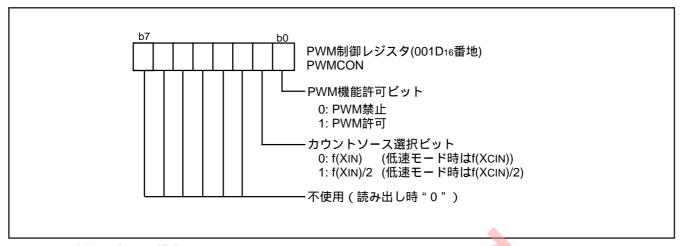

PWM (PWM: Pulse Width Modulation)

PWMは8ビット分解能を持ち、クロック入力XIN又はXINを2分周した信号を基本としています。

## ・データの設定

PWMの出力端子はポートP44と共用しています。PWMプリスケーラによりPWM周期を設定し、PWMレジスタにより出力パルスの"H"期間を設定します。

PWMプリスケーラの値をn、PWMレジスタの値をmとすると、以下のようになります。(ただし、 $n=0\sim255$ 、 $m=0\sim255$ です。)

PWM周期 =

$$\frac{255 \times (n+1)}{f(XIN)}$$

= 31.875 × (n+1)  $\mu$ s ( $f(XIN)$  = 8MHz、カウントソース選択ビット="0"の場合) 出力パルスの" H '期間 =  $\frac{PWM周期 \times m}{255}$

(f(XIN) = 8MHz、カウントソース選択ビット="0"の場合)

$= 0.125 \times (n+1) \times m \mu s$

#### PWMの動作

PWM制御レジスタのビット(X PWM許可ビット)を"1"にすると、PWM出力回路は初期状態より動作を開始し、"H"から始まるパルスを出力します。

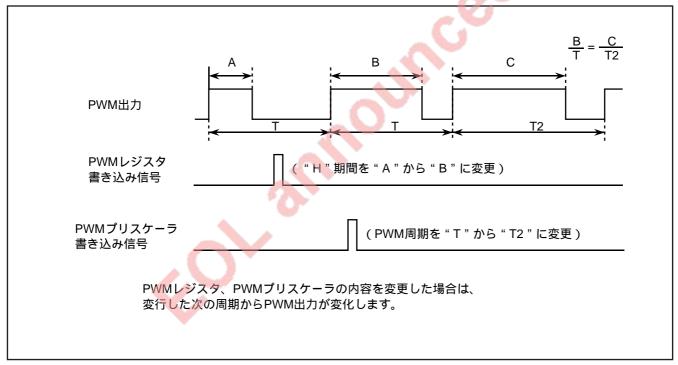

PWM出力PWM中にPWMレジスタ、PWMプリスケーラを変更した場合には、変更した次の周期から変更した内容に対応したパルスが出力されます。

図20.PWM周期のタイミング図

図21 . PWMブロック図

図22. PWM制御レジスタの構成

図23. PWMレジスタ及びPWMプリスケーラ変更時のPWM出力タイミング図

### 注意事項

PWM機能許可ビットが許可に設定され、PWMouT端子から "L"レベルが出力された後、PWMは開始します。この"L"レベ ル出力時間は次のとおりです。

・カウントソース選択ビット = "0"、n = プリスケーラ設定値

$$\frac{n+1}{2 \times f(XIN)}$$

(秒)

・カウントソース選択ビット = "1"、n = プリスケーラ設定値

#### A-D変換器

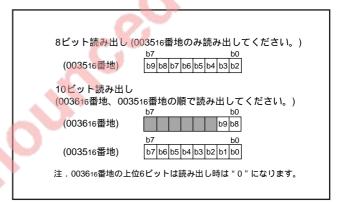

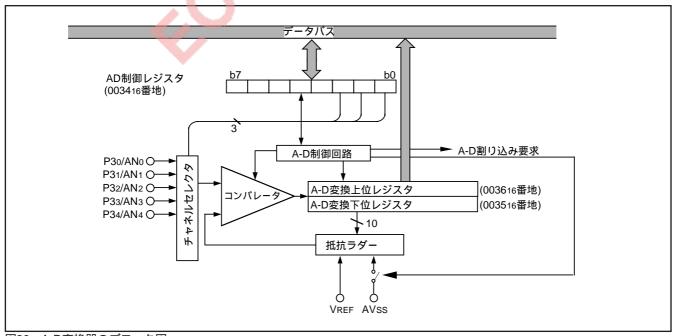

## 【A-D変換レジスタ】AD

A-D変換結果が格納される読み出し専用のレジスタです。 A-D変換中はこのレジスタを読み出さないでください。

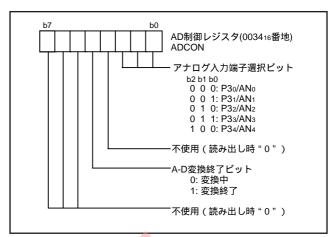

#### 【AD制御レジスタ】ADCON

A-D変換器の制御を行うためのレジスタです。ビット2~ビット0はアナログ入力端子選択ビットです。ビット4はAD変換終了ビットで、A-D変換中は'0"、A-D変換が終了すると'1"になります。このビットに'0"を書き込むことにより、A-D変換が開始されます。

## 【比較電圧発生器】

AVSSとVREFの間の電圧を1024分割し分圧を出力します。

## 【チャネルセレクタ】

ポートP34/AN4~P30/AN0より1本を選択し、コンパレータ に入力します。

## 【コンパレータ及び制御回路】

アナログ入力電圧と比較電圧の比較を行い、その結果をA-D変換レジスタに格納します。また、A-D変換終了時にAD変換終了ビット及びAD割り込み要求ビットを"1"にセットします。コンパレータは容量結合で構成されていますので、A-D変換中はf(XIN)を500kHz以上にしてください。

M38504E6/M6では内蔵の自己発振回路を用いてA-D変換を 実行するため、低速モードでのA-D変換が可能です。

図24.A-D制御レジスタの構成

図25. A-D変換レジスタの構成

図26 . A-D変換器のブロック図

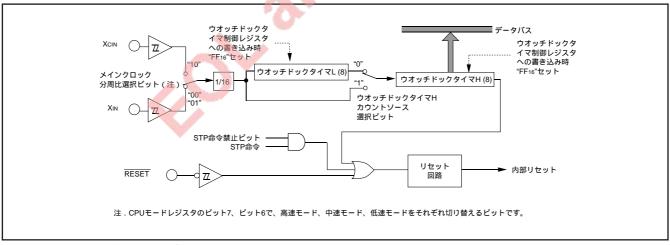

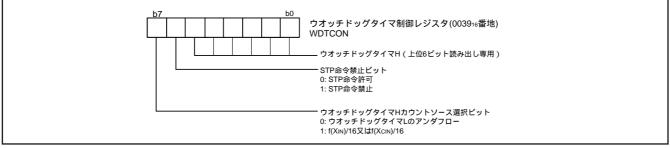

#### ウオッチドッグタイマ

ウオッチドッグタイマは、暴走などによりプログラムが正常なループを走らなかった場合に、リセット状態に復帰する手段を与えるものです。

ウオッチドッグタイマは8ビットのウオッチドッグタイマH と8ビットのウオッチドッグタイマLの計16ビットのカウンタ で構成されています。

## ・ウオッチドッグタイマの基本動作

リセット後ウオッチドッグタイマ制御レジスタ(003916番地)への書き込みがない場合、ウオッチドッグタイマは停止状態です。ウオッチドッグタイマ制御レジスタ(003916番地)に任意の値を書き込むことによりカウントダウンを開始し、ウオッチドッグタイマHのアンダフローにより内部リセットが発生します。したがって、通常はアンダフローする前にウオッチドッグタイマ制御レジスタ(003916番地)に書き込みを行うようにプログラムを組みます。ウオッチドッグタイマ制御レジスタ(003916番地)を読み出した場合は、ウオッチドッグタイマHのカウンタの上位6ビット、STP命令禁止ビット、ウオッチドッグタイマHカウントソース選択ビットの値が読まれます。

### ・ウオッチドッグタイマの初期値

リセット又はウオッチドッグタイマ制御レジスタ(003916 番地)への書き込みによりウオッチドッグタイマHは"FF16" に、ウオッチドッグタイマLは FF16 "に設定されます。

・ウオッチドッグタイマHカウントソース選択ビットの動作 ウオッチドッグタイマ制御レジスタ(003916番地)のビット7 によりウオッチドッグタイマHのカウントソースの選択が可能 です。

このビットが 0 'の場合、カウントソースはウオッチドッグ タイマLのアンダフロー信号となります。検出時間はf(XIN) =8MHz時131.072ms、f(XCIN)=32kHz時32.768sになります。

このビットが 1 "の場合、カウントソースはf(XIN)(又はf(XCIN))の16分周信号となります。この場合の検出時間はf(XIN)=8MHz時512  $\mu$  s、f(XCIN)=32kHz時128msになります。

このビットはリセット後 0 たなります。

## ・STP命令禁止ビットの動作

ウオッチドッグタイマ制御レジスタ(003916番地)のビット6 によりウオッチドッグタイマ動作時のSTP命令を禁止することができます。

このビットが 0 'の場合、STP命令は許可です。

このビットが 1 'の場合、STP命令は禁止され、STP命令が 実行されると内部リセットが発生します。このビットは一旦 "1 'にするとプログラムで'0 'に書き換えることはできなくな ります。

このビットはリセット後(0)になります。

図27. ウオッチドッグタイマのブロック図

図28. ウオッチドッグタイマ制御レジスタの構成

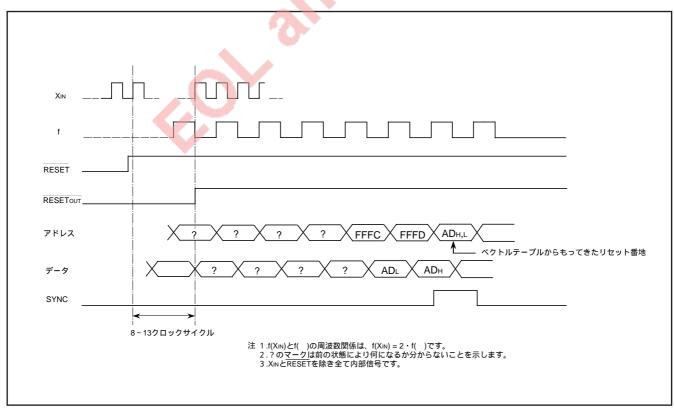

#### リセット回路

電源電圧が2.7~5.5Vにあり、XINが安定発振しているとき、RESET端子をXINの20サイクル以上"L"レベルに保つとリセット状態になり、その後RESET端子を"H"レベルに戻すとリセット解除されます。FFFD16番地の内容を上位アドレス、FFFC16番地の内容を下位アドレスとする番地からプログラムスタートします。

リセット入力電圧は、電源電圧が2.7Vを通過する時点で0.54V以下になるようにしてください。

図29. リセット回路例

図30. リセット時のタイミング図

|      |                                 | 番地 レシ                  | <sup>ブ</sup> スタの内容 |

|------|---------------------------------|------------------------|--------------------|

| (1)  | ポートP0方向レジスタ                     | 000116                 | 0016               |

| (2)  | ポートP1方向レジスタ                     | 000316                 | 0016               |

| (3)  | ポートP2方向レジスタ                     | 000516                 | 0016               |

| (4)  | ポートP3方向レジスタ                     | 000716                 | 0016               |

| (5)  | ポートP4方向レジスタ                     | 000916                 | 0016               |

| (6)  | シリアルI/Oステータスレジスタ                | 001916 1 0             | 000000             |

| (7)  | シリアルI/O制御レジスタ                   | 001A <sub>16</sub>     | 0016               |

| (8)  | UART制御レジスタ                      | 001B <sub>16</sub> 1 1 | 100000             |

| (9)  | PWM制御レジスタ                       | 001D <sub>16</sub>     | 0016               |

| (10) | プリスケーラ12                        | 002016                 | FF16               |

| (11) | タイマ1                            | 002116                 | 0116               |

| (12) | タイマ2                            | 002216                 | 0016               |

| (13) | タイマXYモードレジスタ                    | 002316                 | 0016               |

| (14) | プリスケーラX                         | 002416                 | FF16               |

| (15) | タイマX                            | 002516                 | FF16               |

| (16) | プリスケーラY                         | 002616                 | FF16               |

| (17) | タイマY                            | 002716                 | FF16               |

| (18) | タイマカウントソース <mark>設</mark> 定レジスタ | 002816                 | 0016               |

| (19) | 予約                              | 002C <sub>16</sub>     | 不定                 |

| (20) | 予約                              | 002D16                 | 不定                 |

| (21) | 予約                              | 002E <sub>16</sub>     | 不定                 |

| (22) | 予約                              | 002F <sub>16</sub>     | 不定                 |

| (23) | 予約                              | 003016                 | 不定                 |

| (24) | 予約                              | 003116                 | 不定                 |

| (25) | AD制御レジスタ                        | 003416 0 0             | 010000             |

| (26) | MISRG                           | 003816                 | 0016               |

| (27) | ウオッチドッグタイマ制御レジスタ                | 003916 0 0             | 1 1 1 1 1 1        |

| (28) | 割り込みエッジ選択レジスタ                   | 003A <sub>16</sub>     | 0016               |

| (29) | CPUモードレジスタ                      | 003B <sub>16</sub> 01  | 0 0 1 0 0 0        |

| (30) | 割り込み要求レジスタ1                     | 003C <sub>16</sub>     | 0016               |

| (31) | 割り込み要求レジスタ2                     | 003D <sub>16</sub>     | 0016               |

| (32) | 割り込み制御レジスタ1                     | 003E <sub>16</sub>     | 0016               |

| (33) | 割り込み制御レジスタ2                     | 003F <sub>16</sub>     | 0016               |

| (34) | プロセッサステータスレジスタ                  | (PS)XX                 | XXX1XX             |

| (35) | プログラムカウンタ                       | (PCH) FFF              | D16番地の内容           |

|      | 注 . 🗙 は不定です。                    | (PCL) FFF              | C16番地の内容           |

図31. リセット時の内部状態

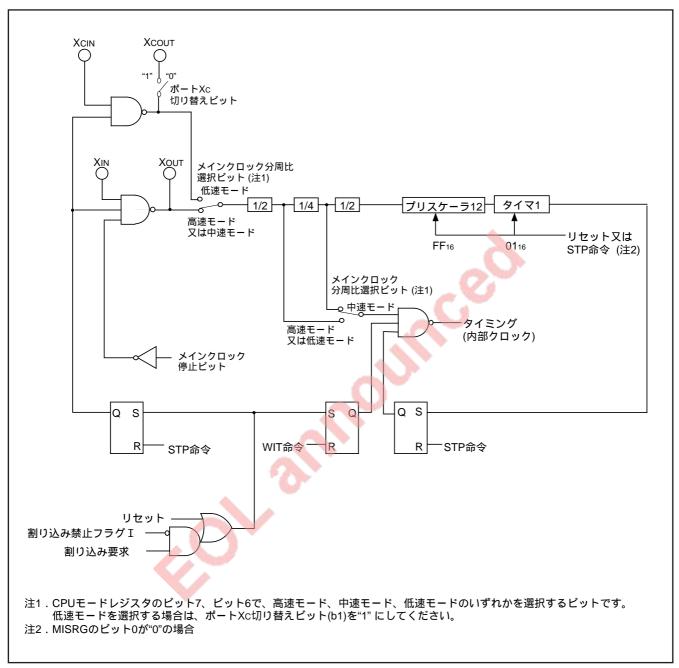

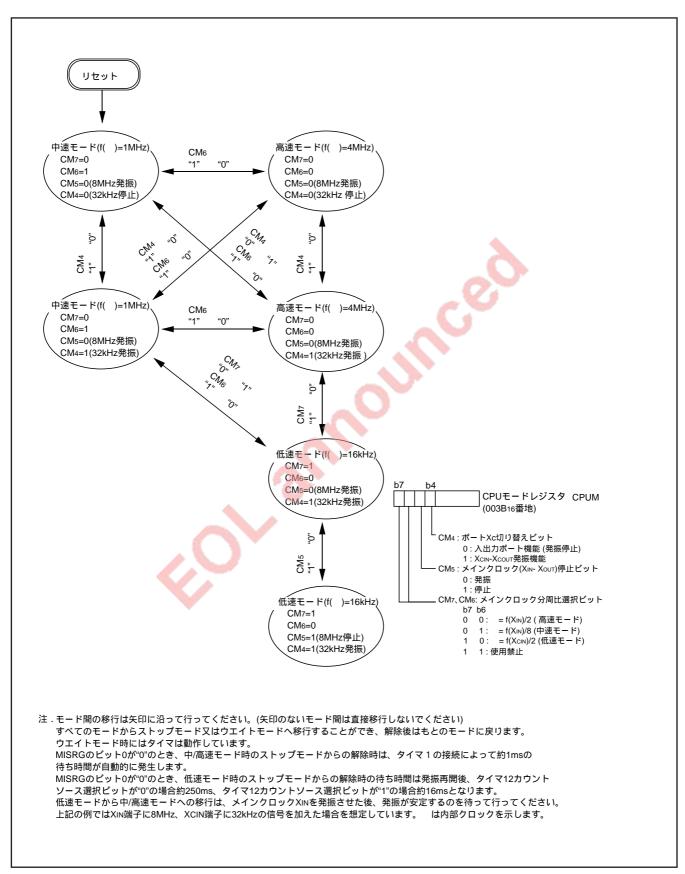

### クロック発生回路

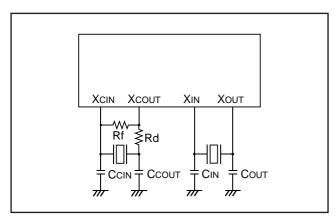

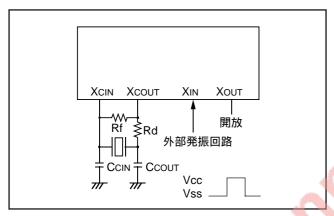

3850グループは2つの内部発振回路を内蔵しています。XINとXOUT又はXCINとXCOUTの間に共振子を接続することにより発振回路を形成することができます。容量などの定数は、共振子によって異なりますので共振子メーカの推奨値をご使用ください。XIN - XOUT端子間には帰還抵抗が内蔵されていますので外付けの抵抗を省略することができます。XCIN - XCOUT間には抵抗は内蔵されていませんので外部に帰還抵抗をつけてください。

電源投入直後はXIN側の発振回路のみが発振を開始し、 XCIN、XCOUT端子は入出力ポートとして機能します。

#### 周波数制御

## (1) 中速モード

XIN端子に加わった周波数の8分周したものが内部クロックとなります。リセット解除後はこのモードになります。

#### (2) 高速モード

XIN端子に加わった周波数の2分周したものが内部クロックの周波数になります。

## (3) 低速モード

XCIN端子に加わった周波数の2分周したものが内部クロックになります。

注. 中/高速モードと低速モード間の移行を行う場合はXIN側、XCIN側ともに発振が安定している必要があります。特に、XCIN側の発振立ち上がりは時間を要するので、電源投入直後やストップからの復帰時は注意してください。また、移行するときはf(XIN) >3・f(XCIN)である必要があります。

#### (4) 低消費電力モード

低速モード時には、CPUモードレジスタのメインクロック 停止ビット(b5)を'1'にすることによりメインクロックXINを停止させて、低消費電力動作が実現できます。この場合、メインクロックXIN発振再開時はメインクロック停止ビットを'0"にした後、発振が安定するまでの待ち時間をプログラムで生成する必要があります。

XCIN-XCOUT発振回路は外部クロック入力による使用はできませんので、必ず外付け発振子による発振をさせてください。

#### 発振制御

#### (1) ストップモード

STP命令を実行すると内部クロック が H "の状態で停止 し、XIN及びXCINの発振が停止します。このとき、STP命令解 除後の発振安定時間設定ビットが"0"の時、タイマ1には "0116"、プリスケーラ12には"FF16"が設定されます。一方、 STP命令解除後の発振安定時間設定ビットが 1 'のときは、タ イマ1、プリスケーラ12には何も設定されませんので、ご使用 になる発振子の発振安定時間にあった待ち時間を設定してく ださい。プリスケーラ12の入力にはXIN又はXCINの16分周が 強制的に接続されます。発振は外部割り込みが受け付けられ ると再開しますが、内部クロックは、タイマ1がアンダフ ローするまで H 'のままです。タイマ1がアンダフローしては じめて内部クロックが供給されます。これは、セラミック 発振などを使用した場合、発振の立ち上がりに時間を要する ためです。リセットによって発振を再開させた場合は、待ち 時間が生成されませんので、発振が安定するまでの期間 RESET端子に"L"レベルを印加してください。

## (2) ウエイトモード

WIT命令を実行すると、内部クロック が H 'の状態で停止しますが、発振器は停止しません。リセット又は割り込みを受け付けると内部クロック の停止を解除します。発振器は停止していませんので直ちに命令を実行できます。

STPあるいはWIT状態を解除する場合、割り込みが受け付けられるためには、STPあるいはWIT命令を実行する前に対応する割り込み許可ビットを"1"にしておく必要があります。また、STP状態の解除の場合、プリスケーラ12、タイマ1はXINを16分周したクロックをカウントしますので、STP命令を実行する前にタイマ1割り込み許可ビットを"0"にしてください。

#### 注意事項

STP命令解除後の発振安定時間設定ビットを'1"で使用される場合は、使用される発振子の発振安定時間を十分評価した上で、タイマ1、プリスケーラ12に値を設定してください。

図32. セラミック共振子外付け回路

図33.外部クロック入力回路

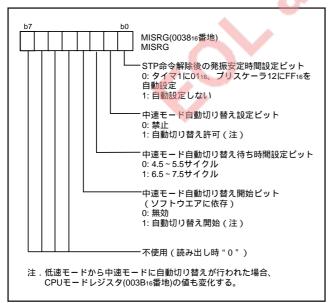

図34.MISRGの構成

#### [MISRG] MISRG

ounced

MISRGは中速モード自動切り替えに関する各種制御を行うビットと、STP命令解除後の発振安定時間の設定を制御するビットで構成されています。

中速モード自動切り替え設定ビットが"1"で、低速モードで動作中に、中速モード自動切り替え開始ビットに"1"を書き込むことによって、自動的にXIN発振が開始し、中速モードに切り替わります。

図35.システムクロック発生回路ブロック図(シングルチップモード)

図36.システムクロックの状態遷移図

## プログラミング上の注意事項

## プロセッサステータスレジスタに関するもの

プロセッサステータスレジスタ(PS)は割り込み禁止フラグIが 1 "であることを除いて、リセット直後は不定です。このため、プログラムの実行に影響を与えるフラグの初期化が必要です。

特に、演算そのものに影響を与えるTフラグ、Dフラグについては初期化が必須となります。

## 割り込みに関するもの

割り込み要求ビットの内容をプログラムで変更した直後に、BBC、BBS命令を実行しても、変更前の内容に対して実行されるので、変更後の内容に対して実行するためには、1命令以上後に行ってください。

## 10進演算に関するもの

- ・10進演算を行う場合は、10進モードフラグDを"1"に設定して、ADC命令又はSBC命令を実行しますが、その場合、SEC命令、CLC命令又はCLD命令はADC命令又はSBC命令から1命令以上後に行ってください。

- ・10進モードでは、N( ネガティブ ) V( オーバフロー ) Z ( ゼロ )フラグが無効となります。

## タイマに関するもの

タイマラッチに値r(0~255)を書き込んだ場合の分周期は、 1/(n+1)です。

#### 乗除算命令に関するもの

- ・MUL、DIV命令は、T、Dフラグの影響を受けません。

- ・乗除算命令の実行ではプロセッサステータスレジスタの 内容は変化しません。

## ポートに関するもの

ポート方向レジスタの値は読み出すことができません。すなわち、LDA命令をはじめ、Tフラグが 1 で場合のメモリ演算命令、方向レジスタの値を修飾値とするアドレッシングモード、BBC、BBSなどのビットテスト命令は使用できません。また、CLB、SEBなどのビット操作命令、RORなどの演算を始めとする方向レジスタのリード・モディファイ・ライト命令も使用できません。方向レジスタの設定はLDM命令、STA命令などを使用してください。

#### シリアルI/Oに関するもの

クロック同期形シリアルI/Oにおいて、外部クロックを用いて受信側がSRDY出力を行う場合、受信許可ビット及びSRDY出力許可ビットとともに、送信許可ビットも"1"に設定してください。

また、シリアルI/Oでは、送信終了後、TxD端子が最終ビットをラッチし出力し続けます。

シリアルI/O(クロック同期形モード)において、同期クロックとして外部クロックを選択した場合、転送クロックの入力レベルが H 'の時に、それぞれ送信バッファレジスタへ送信データを書き込んでください。

## A-D変換に関するもの

比較器は容量結合で構成されており、クロック周波数が低いと電荷が失われます。そのため、A-D変換中はf(XIN)を500kHz以上にしてください。

また、A-D変換中はSTP命令、WIT命令を実行しないでください。

#### 命令の実行時間に関するもの

命令の実行時間は機械語命令一覧表に記載されているサイクル数に内部クロック の周期をかけることによって得られます。内部クロック の周期は高速モードではXIN周期の2倍です。

## 使用上の注意事項

## 電子端子の取扱いに関する注意事項

ご使用の際には、ラッチアップ現象防止のため、素子の電源端子(Vcc端子)とGND端子(Vss端子)との間、及び電源端子(Vcc端子)とアナログ電源入力端子(AVss端子)との間に高周波特性の良いコンデンサをバイパスコンデンサとして付加してください。バイパスコンデンサは0.01 μ F ~ 0.1 μ F のセラミックコンデンサを推奨いたします。

また、バイパスコンデンサは電源端子とGND端子との間、電源端子とアナログ電源入力端子との間を最短距離で付加してくださるようお願いいたします。

ワンタイムPROM版/マスクROM版の相違点に関する注意事項 ワンタイムPROM版及びマスクROM版は、製造プロセス、 内蔵ROM、レイアウトパターンの相違などにより、電気的特性の範囲内で、特性値、動作マージン、ノイズ耐量、ノイズ 幅射量などが異なる場合があります。マスクROM版への切り 換え時は、ワンタイムPROM版で実施したシステム評価試験 と同等の試験を実施してください。

#### マスク化発注時の提出資料

マスクROM版のマスク化発注時、次の資料を提出してください。

- ・マスク化確認書

- ・マーク指定書

- ・ROMのデータ ..... EPROM 3セット

## ROM書き込み発注時の提出資料

ワンタイムPROM版の工場書き込み発注時、次の資料を提出してください。

- ・ROM書き込み確認書

- ・マーク指定書(客先ロゴ入り特殊マークのみ)

- ・ROMのデータ ...... EPROM 3セット

\*マスク化確認書、ROM書き込み確認書、マーク指定書につきましては、ルネサステクノロジホームページ ROM発注 (http://www.renesas.com/jp/rom)を参照してください。

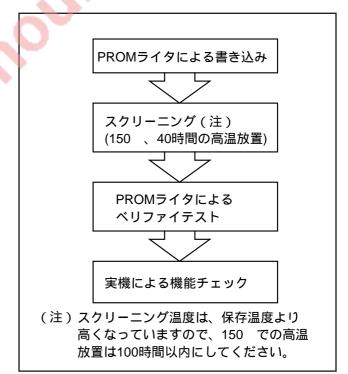

#### ROM書き込み方法

ワンタイムPROM版(ブランク品)及びEPROM内蔵版は、専用の書き込みアダプタを使用することにより汎用のPROMライタで内蔵PROMの書き込み、読み出しを行うことができます。なお、PROMライタのアドレス設定は、ユーザROM領域に設定してご使用ください。

表5.専用書き込みアダプタ

| パッケージ          | 書き込みアダプタ型名   |

|----------------|--------------|

| 42P4B, 42S1B-A | PCA4738S-42A |

| 42P2R-A/E      | PCA4738F-42A |

ワンタイムPROM版(プランク品)は、当社でのアセンプリ 工程以降PROMの書き込みテスト、スクリーニングを行って いません。書き込み以降の信頼性を向上するため、図37に示 すフローで書き込み、テストを行った後使用されることを推 奨いたします。

図37.ワンタイムPROM版書き込みとテスト

## 電気的特性

# 絶対最大規格

表6. 絶対最大定格

| 記号   | 項目                                        | 条件                   | 定格値               | 単位 |

|------|-------------------------------------------|----------------------|-------------------|----|

| Vcc  | 電源電圧                                      |                      | - 0.3 ~ 7.0       | V  |

| VI   | 入力電圧                                      |                      | - 0.3 ~ Vcc + 0.3 | V  |

|      | P00 ~ P07, P10 ~ P17, P20, P21, P24 ~ P27 | 21, P24 ~ P27        |                   |    |

|      | P30 ~ P34, P40 ~ P44, VREF                |                      |                   |    |

| Vı   | 入力電圧 P22~P23                              | Vss端子を基準にし           | - 0.3 ~ 5.8       | V  |

| Vı   | 入力電圧 RESET, XIN                           | 一て測定する。              | - 0.3 ~ Vcc + 0.3 | V  |

| Vı   | 入力電圧 CNVss                                | │出力トランジスタは<br>│遮断状態。 | - 0.3 ~ 13        | V  |

| Vo   | 出力電圧                                      |                      | - 0.3 ~ Vcc + 0.3 | V  |

|      | P00 ~ P07, P10 ~ P17, P20, P21, P24 ~ P27 |                      |                   |    |

|      | P30 ~ P34, P40 ~ P44, XOUT                |                      | . 676             |    |

| Vo   | 出力電圧 P22, P23                             | 4                    | - 0.3 ~ 5.8       | V  |

| Pd   | 消費電力                                      | Ta = 25              | 1000(注)           | mW |

| Topr | 動作周囲温度                                    | 4                    | - 20 ~ 85         |    |

| Tstg | 保存温度                                      |                      | - 40 ~ 125        |    |

注 . 42P2R-A/Eパッケージの場合は300mWです。

### 推奨動作条件

表7.推奨動作条件(1)(指定のない場合はVcc=2.7~5.5V, Ta=-20~85)

| 記号      |      | 項目                           |             |                                                                                           | 規格値    |     | 単位       |      |

|---------|------|------------------------------|-------------|-------------------------------------------------------------------------------------------|--------|-----|----------|------|

| 記       | 号    |                              | J           | <b>頁 目</b>                                                                                | 最 小    | 標準  | 最大       | 甲位   |

| /cc     |      | 電源電圧                         | 8MHz時       | (高速モード)                                                                                   | 4.0    | 5.0 | 5.5      | ٧    |

| 700     |      | 电冰电压                         | 8MHz時       | (中速モード)、4MHz時 (高速モード)                                                                     | 2.7    | 5.0 | 5.5      | V    |

| /ss     |      | 電源電圧                         |             |                                                                                           |        | 0   |          | V    |

| /REF    |      | A-D変換器基準管                    | 電圧          |                                                                                           | 2.0    |     | Vcc      | ٧    |

| AVss    |      | アナログ電源電圧                     | Ē           |                                                                                           |        | 0   |          | V    |

| /IA     |      | アナログ入力電圧                     | E ANo ~ AN  | 4                                                                                         | AVss   |     | Vcc      | V    |

| /IH     |      | " H " 入力電圧                   |             |                                                                                           | 0.8Vcc |     | Vcc      | V    |

|         |      | P00 ~ P07, P10               | o ~ P17, P2 | o ~ P27, P30 ~ P34                                                                        |        |     |          |      |

|         |      | P40 ~ P44                    |             |                                                                                           |        |     |          |      |

| /IH     |      | " H " 入力電圧 R                 | RESET, XIN  | , CNVss                                                                                   | 0.8Vcc |     | Vcc      | V    |

| /IL     |      | " L " 入力電圧                   |             |                                                                                           | 0      | 10  | 0.2 Vcc  | V    |

|         |      | P00 ~ P07, P10               | o ~ P17, P2 | 0 ~ P27, P30 ~ P34                                                                        |        |     |          |      |

|         |      | P40 ~ P44                    |             |                                                                                           |        |     |          | V    |

| /IL     |      | " L " 入力電圧 R                 | ESET, CN    | Vss                                                                                       | 0      |     | 0.2 Vcc  | V    |

| /IL     |      | " L " 入力電圧 X                 | IN          |                                                                                           | 0      |     | 0.16 Vcc | V    |

| IOH(pe  | eak) | " H " 出力総尖頭<br>P0o~P07, P10  |             | (注)<br>0~P34                                                                              |        |     | -80      | mA   |

| IOH(pe  | eak) | " H " 出力総尖頭<br>P20, P21, P24 |             | (注)<br>~ P44                                                                              |        |     | -80      | mA   |

| IOL(pea | ak)  | " L " 出力総尖頭                  | 電流 (注)      | P00 ~ P07, P10 ~ P12, P30 ~ P34<br>(M38503E4/M2/M4)<br>P00 ~ P07, P30 ~ P34 (M38504E6/M6) |        |     | 80       | mA   |

| IOL(pea | 2k)  | <br>" L " 出力総尖頭              | 雷流 (注)      | P13 ~ P17 (M38503E4/M2/M4)                                                                |        |     | 80       | mA   |

| Юцрес   | ak)  |                              | 电/ル (/工)    | P10~P17 (M38504E6/M6)                                                                     |        |     | 120      | IIIA |

| IOL(pea | ak)  | " L " 出力総尖頭<br>P20~P27, P40  |             | (注)                                                                                       |        |     | 80       | mA   |

| IOH(av  | rg)  | " H " 出力総平均<br>P00~P07, P10  |             | (注)<br>0~P34                                                                              |        |     | -40      | mA   |

| IOH(av  | rg)  | " H " 出力総平均<br>P20, P21, P24 |             | (注)<br>~ P44                                                                              |        |     | -40      | mA   |

| IOL(avç | g)   | " L " 出力総平均                  | 電流 (注)      | P00 ~ P07, P10 ~ P12, P30 ~ P34<br>(M38503E4/M2/M4)<br>P00 ~ P07, P30 ~ P34 (M38504E6/M6) |        |     | 40       | mA   |

| IOL(avo | g)   | " L " 出力総平均                  | 電流 (注)      | P13 ~ P17 (M38503E4/M2/M4)                                                                |        |     | 40       | mA   |

|         |      |                              |             | P10 ~ P17 (M38504E6/M6)                                                                   |        |     | 60       |      |

| IOL(avç | g)   | " L " 出力総平均<br>P20~P27, P40  |             | (注)                                                                                       |        |     | 40       | mA   |

注. 出力総平均電流は該当するポートすべてに流れる電流の総和です。総平均電流は100msの期間内での平均値で、総尖頭電流は総和のピーク値です。

表8. 推奨動作条件(2)(指定のない場合はVCC=2.7~5.5V, Ta=-20~85)

|           |                                                  |                                                                           |     | 規格( | 直    |      |

|-----------|--------------------------------------------------|---------------------------------------------------------------------------|-----|-----|------|------|

| 記号        |                                                  | 項目                                                                        | 最 小 | 標準  | 最大   | 単位   |

| IOH(peak) | " H " 出力尖頭電流<br>P00~P07, P10~F<br>P30~P34, P40~F | (注1)<br>P17, P20, P21, P24~P27<br>P44                                     |     |     | - 10 | mA   |

| IOL(peak) | " L " 出力尖頭電流<br>(注1)                             | P00 ~ P07, P10 ~ P12, P20 ~ P27, P30 ~ P34,<br>P40 ~ P44 (M38503E4/M2/M4) |     |     | 10   |      |

|           |                                                  | P00 ~ P07, P20 ~ P27, P30 ~ P34, P40 ~ P44<br>(M38504E6/M6)               |     |     |      | mA   |

| IOL(peak) | " L " 出力尖頭電流                                     | P13 ~ P17 (M38503E4/M2/M4)                                                |     |     |      |      |

|           | (注1)                                             | P10 ~ P17 (M38504E6/M6)                                                   |     |     | 20   | mA   |

| IOH(avg)  | " H " 出力平均電流<br>P00~P07, P10~F<br>P30~P34, P40~F | P00 ~ P07, P10 ~ P17, P20, P21, P24 ~ P27                                 |     |     | - 5  | mA   |

| IOL(avg)  | " L " 出力平均電流<br>(注2)                             | P00 ~ P07, P10 ~ P12, P20 ~ P27, P30 ~ P34,<br>P40 ~ P44 (M38503E4/M2/M4) | _Q  | 9   | 5    | mA   |

|           |                                                  | P00 ~ P07, P20 ~ P27, P30 ~ P34, P40 ~ P44<br>(M38504E6/M6)               | C   |     | 5    | IIIA |

| IOL(avg)  | " L " 出力平均電流                                     | P13 ~ P17 (M38503E4/M2/M4)                                                |     |     |      |      |

|           | (注2)                                             | P10 ~ P17 (M38504E6/M6)                                                   |     |     | 15   | mA   |

| f(XIN)    | 内部クロック発振周<br>(Vcc=4.0~5.5V)                      | 波数 (注3)                                                                   |     |     | 8    | MHz  |

| f(XIN)    | 内部クロック発振周<br>(Vcc=2.7~5.5V)                      | 波数 (注3)                                                                   |     |     | 4    | MHz  |

- 注1. 出力尖頭電流は1ポートごとに流れる電流のピーク値を規定します。

- 2 . 平均出力電流IOL(avg) , IOH(avg)は100msの期間での平均値です。

- 3.発振周波数はデューティ50%の場合です。

### 電気的特性

表9. 電気的特性(1)(指定のない場合はVcc=2.7~5.5V, Vss=0V, Ta=-20~85)

| 記号   | 項目           |                                                                                 | 測定条件                              |           | 規格値 |     | 単位 |  |

|------|--------------|---------------------------------------------------------------------------------|-----------------------------------|-----------|-----|-----|----|--|

| 10 3 |              | - H                                                                             | //J //C // 11                     | 最 小       | 標準  | 最 大 | 12 |  |

| Voн  | 1            |                                                                                 | IOH = - 10mA<br>VCC = 4.0 ~ 5.5V  | Vcc - 2.0 |     |     | V  |  |

|      | P24 ~ P27, P | '30~P34, P40~P44<br>(注)                                                         | IOH = - 1.0mA<br>VCC = 2.7 ~ 5.5V | Vcc - 1.0 |     |     | V  |  |

| VoL  | " H " 出力電圧   | P00 ~ P07, P10 ~ P17,<br>P20 ~ P27, P30 ~ P34,<br>P40 ~ P44<br>(M38503E4/M2/M4) | IOL = 10mA<br>VCC = 4.0 ~ 5.5V    |           |     | 2.0 | V  |  |

|      |              | P00 ~ P07, P20 ~ P27,<br>P30 ~ P34, P40 ~ P44<br>(M38504E6/M6)                  | IOL = 1.0mA<br>VCC = 2.7 ~ 5.5V   |           |     | 1.0 | V  |  |

| VoL  | " L " 出力電圧   | P13 ~ P17<br>(M38503E4/M2/M4)                                                   | IOL = 20mA<br>VCC = 4.0 ~ 5.5V    |           |     | 2.0 | V  |  |

|      |              | P10 ~ P17<br>(M38504E6/M6)                                                      | IOL = 10mA<br>VCC = 2.7 ~ 5.5V    |           |     | 1.0 | V  |  |

注. P25に関しては, UART制御レジスタのP25/TxD Pチャネル出力禁止ビット(001B16番地のビット4)が 0 "の場合です。

表10. 電気的特性(2)(指定のない場合はVcc=2.7~5.5V, Vss=0V, Ta=-20~85)

| +7 - 17    |                                                                        | No. 27 47 14 | 規               | 見格 値 |       | *** 45- |  |

|------------|------------------------------------------------------------------------|--------------|-----------------|------|-------|---------|--|

| 記号         | 項 目                                                                    | 川 別定条件       | 最 小 標 準         |      | 最大    | 単位      |  |

| VT+ - VT - | ヒステリシス<br>CNTRo, CNTR1, INTo~INT3                                      |              |                 | 0.4  |       | V       |  |

| VT+ - VT - | ヒステリシス<br>RxD, Sclk                                                    |              |                 | 0.5  |       | V       |  |

| VT+ - VT - | ヒステリシス RESET                                                           |              |                 | 0.5  |       | V       |  |

| lін        | " H " 入力電流<br>P00~P07, P10~P17, P20, P21,<br>P24~P27, P30~P34, P40~P44 | VI=VCC       |                 |      | 5.0   | μА      |  |

| IIН        | " H " 入力電流 RESET, CNVss                                                | VI=VCC       |                 |      | 5.0   | μA      |  |

| Iн         | " H " 入力電流 XIN                                                         | VI=VCC       |                 | 4    |       | μΑ      |  |

| lıL        | "L"入力電流<br>P00~P07, P10~P17, P20~P27<br>P30~P34, P40~P44               | VI=VSS       | 5               |      | - 5.0 | μА      |  |

| liL        | " L " 入力電流 RESET, CNVss                                                | VI=VSS       | 17.             |      | - 5.0 | μА      |  |

| liL        | " L " 入力電流 XIN                                                         | VI=VSS       | No. of the last | - 4  |       | μА      |  |

| VRAM       | RAM保持電圧                                                                | クロック停止時      | 2.0             |      | 5.5   | V       |  |

表11. 電気的特性(3)(指定のない場合はVcc=2.7~5.5V, Vss=0V, Ta= - 20~85)

|     |      |    |                                                                                        |             |     | 規格値 |      | );; (÷ |

|-----|------|----|----------------------------------------------------------------------------------------|-------------|-----|-----|------|--------|

| 記号  | 項    | 目  | 測定条件                                                                                   | ŧ           | 最 小 | 標準  | 最大   | 単位     |

| Icc | 電源電流 |    | 高速モード時<br>f(X <sub>I</sub> N)=8MHz<br>f(X <sub>C</sub> IN)=32.768kHz<br>出カトランジスタは遮断    | (XIN)=8MHz  |     |     | 13   | mA     |

|     |      |    | 高速モード時<br>f(Xin)=8MHz (WIT命令)<br>f(Xcin)=32.768kHz<br>出力トランジスタは遮断                      |             |     | 1.6 |      | mA     |

|     |      |    | 低速モード時<br>f(X <sub>I</sub> N)=停止<br>f(X <sub>C</sub> IN)=32.768kHz<br>出カトランジスタは遮断      | <b>f</b> 状態 |     | 60  | 200  | μA     |

|     |      |    | 低速モード時<br>f(X <sub>I</sub> N)=停止<br>f(X <sub>C</sub> IN)=32.768kHz(WIT)<br>出力トランジスタは遮断 |             | 60  | 20  | 40   | μA     |

|     |      |    | 低速モード時(VCC=3V)<br>f(XIN)=停止<br>f(XCIN)=32.768kHz<br>出カトランジスタは遮断                        | <b>行状態</b>  |     | 20  | 55   | μА     |

|     |      |    | 低速モード時(Vcc=3V)<br>f(XiN)=停止<br>f(XciN)=32.768kHz(WIT<br>出力トランジスタは遮断                    |             |     | 5.0 | 10.0 | μA     |

|     |      |    | 中速モード時<br>f(X <sub>I</sub> N)=8MHz<br>f(X <sub>C</sub> IN)=停止<br>出カトランジスタは遮断           | <b>ī</b> 状態 |     | 4.0 | 7.0  | mA     |

|     |      | .0 | 中速モード時<br>f(XIN)=8MHz (WIT命令実行時)<br>f(XCIN)=停止<br>出力トランジスタは遮断状態                        |             |     | 1.5 |      | mA     |

|     |      |    | A-D変換器動作時の増量<br>f(XIN)=8MHz                                                            |             |     | 800 |      | μA     |

|     |      |    | 発振はすべて停止<br>(STP命令実行時)                                                                 | Ta = 25     |     | 0.1 | 1.0  | μА     |

|     |      |    | 出力トランジスタは<br>遮断状態                                                                      | Ta = 85     |     |     | 10   | μА     |

#### A-D変換器特性

### 表12. A-D変換器特性

(指定のない場合は, VCC=2.7~5.5V, VSS=AVSS=0= - 20~85 , f(XIN)=8MHz)

|                  |            | 271 4- //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ŧ            | 見格 値 | <u> </u> | 24 /4 |       |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|----------|-------|-------|

| 記号               | 項目         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 測定条件         | 最 小  | 標準       | 最大    | 単位    |

| - 分解能            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |      |          | 10    | bit   |

| - 絶対精度(量子化誤差は除く) |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |      |          | ± 4   | LSB   |

| tCONV            | 変換時間       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 高速モード及び中速モード |      |          | 61    | tc( ) |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 低速モード (注)    |      | 40       |       | μs    |

| RLADDER          | ラダー抵抗      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |      | 35       |       | k     |

| IVREF            | 基準電源入力電流   | VREF接続時                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VREF=5.0V    | 50   | 150      | 200   | μA    |

|                  |            | VREF切断時                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |      |          | 5.0   | μA    |

| lı(AD)           | A-Dポート入力電流 | it in the second |              |      | 0.5      | 5.0   | μA    |

注. 低速モードでのA-D変換の実行は、M38504E6/M6のみ可能です。

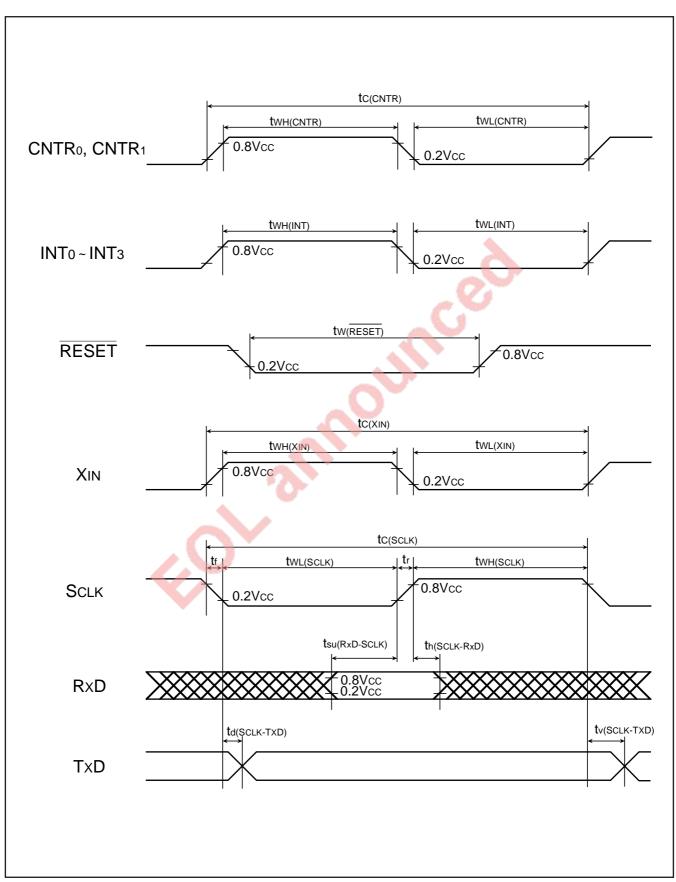

#### タイミング必要条件

### 表13. タイミング必要条件(1)

(指定のない場合はVcc=4.0~5.5V, Vss=0V, Ta=-20~85)

|               |                                  |     | 34.7- |    |         |

|---------------|----------------------------------|-----|-------|----|---------|

| 記号            | 項 目<br>                          | 最 小 | 標準    | 最大 | 単位      |

| tw(RESET)     | リセット入力 "L " パルス幅                 | 20  |       |    | XINサイクル |

| tc(XIN)       | 外部クロック入力サイクル時間                   | 125 |       |    | ns      |

| twh(XIN)      | 外部クロック入力 " H " パルス幅              | 50  |       |    | ns      |

| twL(XIN)      | 外部クロック入力 " L " パルス幅              | 50  |       |    | ns      |

| tc(CNTR)      | CNTRo, CNTR1入力サイクル時間             | 200 |       |    | ns      |

| twh(CNTR)     | CNTRo, CNTR1, INTo~INT3入力"H"パルス幅 | 80  |       |    | ns      |

| twL(CNTR)     | CNTRo, CNTR1, INTo~INT3入力"L"パルス幅 | 80  |       |    | ns      |

| tc(Sclk)      | シリアルI/Oクロック入力サイクル時間 (注)          | 800 |       |    | ns      |

| twh(Sclk)     | シリアルI/Oクロック入力 " H " パルス幅 (注)     | 370 |       |    | ns      |

| twL(Sclk)     | シリアルI/Oクロック入力 "L"パルス幅 (注)        | 370 |       |    | ns      |

| tsu(RxD-SCLK) | シリアルI/O入力セットアップ時間                | 220 | 100   |    | ns      |

| th(SCLK-RxD)  | シリアルI/O入力ホールド時間                  | 100 |       |    | ns      |

注 . f(XIN)=8MHz、001A16番地のビット6が 1 "(クロック同期式モード)の場合です。 f(XIN)=8MHz、001A16番地のビット6が 0 "(非同期式モード)の場合は,値は1/4になります。

### 表14. タイミング必要条件(2)

(指定のない場合はVcc=2.7~5.5V, Vss=0V, Ta=-20~85)

|               | 75 8                                           |      | 規格値 |    | - × /÷  |

|---------------|------------------------------------------------|------|-----|----|---------|

| 記号            | 項目                                             | 最 小  | 標準  | 最大 | 単位      |

| tw(RESET)     | リセット入力 "L " パルス幅                               | 20   |     |    | XiNサイクル |

| tc(XIN)       | 外部クロック入力サイクル時間                                 | 250  |     |    | ns      |

| twh(XIN)      | 外部クロック入力 " H " パルス幅                            | 100  |     |    | ns      |

| twL(XIN)      | 外部クロック入力 " L " パルス幅                            | 100  |     |    | ns      |

| tc(CNTR)      | CNTR <sub>0</sub> , CNTR <sub>1</sub> 入力サイクル時間 | 500  |     |    | ns      |

| twh(CNTR)     | CNTRo, CNTR1, INTo~INT3入力"H"パルス幅               | 230  |     |    | ns      |

| twL(CNTR)     | CNTRo, CNTR1, INTo~INT3入力"L"パルス幅               | 230  |     |    | ns      |

| tc(Sclk)      | シリアルI/Oクロック入力サイクル時間 (注)                        | 2000 |     |    | ns      |

| twh(Sclk)     | シリアルI/Oクロック入力" H " パルス幅 (注)                    | 950  |     |    | ns      |

| twL(Sclk)     | シリアルI/Oクロック入力 "L"パルス幅 (注)                      | 950  |     |    | ns      |

| tsu(RxD-SCLK) | シリアルI/O入力セットアップ時間                              | 400  |     |    | ns      |

| th(SCLK-RxD)  | シリアルI/O入力ホールド時間                                | 200  |     |    | ns      |

注 . f(XIN)=4MHz、001A16番地のビット6が 1 "(クロック同期式モード)の場合です。 f(XIN)=4MHz、001A16番地のビット6が 0 "(非同期式モード)の場合は,値は1/4になります。

#### スイッチング特性

### 表15. スイッチング特性(1)

(指定のない場合は, VCC=4.0~5.5V, VsS=0V, Ta=-20~85)

|               |                          |      |     | 規格               |    | - <del> </del> |    |

|---------------|--------------------------|------|-----|------------------|----|----------------|----|

| 記号            | 項 目<br>                  | 測定条件 | 最 小 | 標準               | 最大 | 単位             |    |

| twh (Sclk)    | シリアルI/Oクロック出力 " H " パルス幅 |      |     | tc(SclK1)/2 - 30 |    |                | ns |

| twl (Sclk)    | シリアルI/Oクロック出力 " L " パルス幅 |      |     | tc(SclK1)/2 - 30 |    |                | ns |

| td (SCLK-TXD) | シリアルI/O出力遅延時間            | (注1) |     |                  |    | 140            | ns |

| tv (Sclk-TxD) | シリアルI/O出力有効時間            | (注1) | 図38 | - 30             |    |                | ns |

| tr (SCLK)     | シリアルI/Oクロック出力立ち上がり時間     |      |     |                  |    | 30             | ns |

| tf (SCLK)     | シリアルI/Oクロック出力立ち下がり時間     |      |     |                  | 30 | ns             |    |

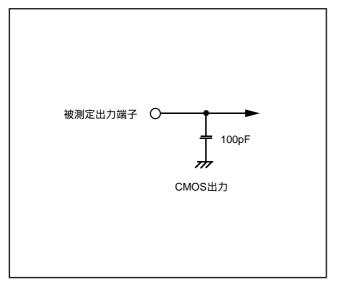

| tr (CMOS)     | CMOS出力 立ち上がり時間           |      | _   | 10               | 30 | ns             |    |

| tf (CMOS)     | CMOS出力 立ち下がり時間           | (注2) |     |                  | 10 | 30             | ns |

注1.twh (SCLK)、twL (SCLK)に関しては、UART制御レジスタのP25/TxD Pチャネル出力禁止ビット(001B16番地のビット4)が 0 'の場合です。 2.XouT端子を除きます。

### 表16.スイッチング特性(2)

(指定のない場合は, Vcc=2.7~5.5V, Vss=0V, Ta=-20~85)

|               | 項目                       |      |      | 規格               | 値  |     | 224 /2- |

|---------------|--------------------------|------|------|------------------|----|-----|---------|

| 記号            |                          |      | 測定条件 | 最 小              | 標準 | 最大  | 単位      |

| twh (Sclk)    | シリアルI/Oクロック出力 " H " パルス幅 |      |      | tc(SclK1)/2 - 50 |    |     | ns      |

| twl (Sclk)    | シリアルI/Oクロック出力 " L " パルス幅 |      |      | tc(SclK1)/2 - 50 |    |     | ns      |

| td (SCLK-TXD) | シリアルI/O出力遅延時間            | (注1) |      |                  |    | 350 | ns      |

| tv (Sclk-TxD) | シリアルI/O出力有効時間            | (注1) | 図38  | - 30             |    |     | ns      |

| tr (SCLK)     | シリアルI/Oクロック出力立ち上がり時間     | ·    |      |                  |    | 50  | ns      |

| tf (SCLK)     | シリアルI/Oクロック出力立ち下がり時間     |      |      |                  |    | 50  | ns      |

| tr (CMOS)     | CMOS出力 立ち上がり時間           | (注2) |      |                  | 20 | 50  | ns      |

| tf (CMOS)     | CMOS出力 立ち下がり時間           | (注2) |      |                  | 20 | 50  | ns      |

注1.twh (SCLK)、twL (SCLK)に関しては、UART制御レジスタのP25/TxD Pチャネル出力禁止ビット(001B16番地のビット4)が 0 'の場合です。 2.Xout端子を除きます。

図38. 出力スイッチング特性測定回路図

図39. タイミング図

### 外形寸法図

Plastic 42pin 450mil SSOP