# APPLICATION NOTE

Using DCP for Video Gain and Cable Compensation

AN1481 Rev 0.00 Jan 18, 2011

There are times when video gain control is needed. DCPs are often overlooked for this application as they are thought to have too low a bandwidth for video applications. Yet, by selecting the proper DCP, the circuit bandwidth can be extended to sufficiently support NTSC and PAL, as well as HDTV video.

# Here are 4 DCP Solutions that will be Covered

1. Video Gain from 0.5 to Gain of 2

**CENESAS**

- 2. Low Noise Video Gain Control

- 3. Low Noise Cable Compensation

- 4. Low Noise Video Gain Control and Cable Compensation

### Compensation

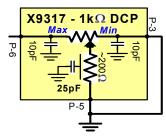

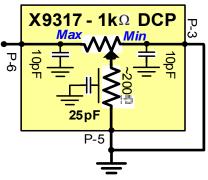

The high operating capacitance of the CMOS switches used in the DCPs with large end to end resistance values reduces the DCP's signal bandwidth (see Figure 1). A low end-to-end resistance value DCPs should be used for video to maintain as large a bandwidth as possible. The X9317ZS8Z is a good choice as its end-to-end resistance is  $1 k\Omega$ .

FIGURE 1. DCP SPICE MODEL

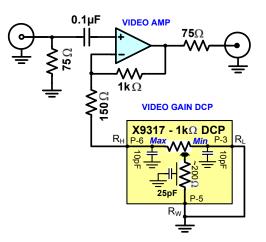

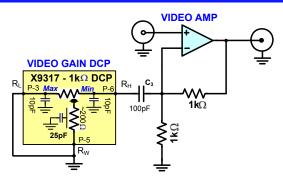

A conventional gain control design, using a DCP, provides input signal attenuation and is followed by a fixed gain op amp. However, in a video application, the DCP will require bandwidth compensation.

## Video Gain from 0.5 to Gain of 2

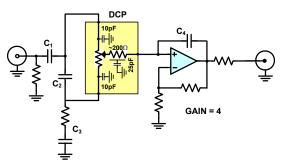

Figure 2 shows a basic design. Note that no terminal of the DCP is left open. This reduces the chance of induced noise. The gain control, in this configuration, is as linear as the DCPs linearity. The video termination requires the typical gain of 2 but using the DCP as shown in Figure 2, as a voltage divider, requires an extra gain of 2. For comparison, using a DCP in the op amp feedback path would lower the bandwidth due to the internal C's as shown in Figure 1. The design must overcome the effect of these DCP parasitic capacitors on bandwidth. The DCP is configured as a voltage divider, see Figure 2. An extra gain of 2 is required to overcome this voltage divider loss. But, the added gain will double the op amp noise. Since the op amp noise is very small, as compared to the video signal, this additional gain will not be an issue except, for large screen displays.

### **Bandwidth Enhancement**

Figure 2 uses two small capacitors,  $C_2$  and  $C_3$ , for bandwidth recovery to compensate for the bandwidth loss of the DCP. The capacitors are very small value, which have little risk of causing excess peaking. The stray DCP capacitance can cause excessive band width lost when wiper is at low end of the DCP. The wiper has ~25pF to ground forming an RC pole with the resistance of the DCP. The pole causes high frequency bandwidth roll-off.

When the wiper is at the bottom of the DCP by adding  $C_2$ , you have an AC divider with the DCPs internal capacitance. This forms the same divider ratio as the DC resistive divider of the DCP. Thus, the AC and DC gains are equal and you have reduced the risk of excessive peaking. Due to the non-linearity of the AC performance of the DCP, we added C4 to boost the gain at the middle of the DCP range. C4 generates a little positive feed back to compensate for the loss at this mid-range.

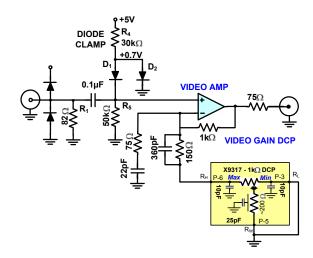

FIGURE 2. VIDEO GAIN DCP BANDWIDTH COMPENSATION

# **Circuit Biasing**

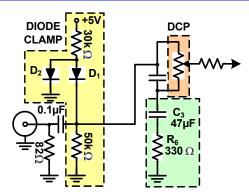

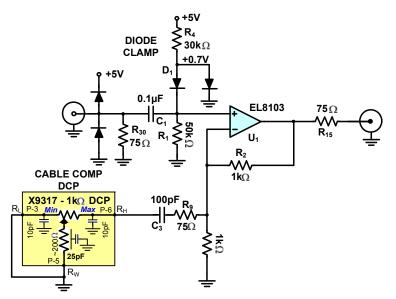

The X9317 DCP is a 0V to 5V supply part. Yet, the composite video signal is AC-coupled and the DCP would see minus voltage which would exceed the device's absolute maximum ratings. To correct for this, a two diode clamp ( $D_1$  and  $D_2$ ) is used to clamp the sync tip to approximately 100mV above ground, see Figure 3. The 100mV is the result of the difference in the bias current of the diode D2 about 16-to-1 ratio to D1 Current. The clamp circuit also reduces some power line noise on the video input signal. At the beginning of each line the sync tip is clamped to zero. Thus, any AC noise will also be clamped to zero, reducing the AC noise.

FIGURE 3. INPUT DIODE CLAMP AND BIASED NETWORK

For the DCP to attenuate the incoming signal, one end must be grounded. By placing C<sub>3</sub> from the bottom of the DCP to ground, we form an AC Ground. However, when the DCP wiper is at the bottom, there will be no video output. We need to offset this node to allow for a desired level of video out. By using R<sub>6</sub> = 330 $\Omega$ , we form a 4:1 divider with the DCP end-to-end resistance. Thus, if the input is 2V, the output of the DCP would be  $\frac{1}{4}$  or 0.5V and the gain of 4 of the amplifier, would be 2V output of the amplifier.

The C<sub>3</sub> capacitor is large enough to maintain an average value of the video signal, which can vary from ~0.4VDC to ~1VDC, is unipolar and the average value is video content dependent. Due to the size of C<sub>3</sub>, bias is very slow moving, the range of bias will work with the DCP and op amp. The op amp is a 0V to 5V supply part. Thus, the sync-tip will change from 0.1V to 0.5V caused by the DCP setting and the video content. This may require using an output coupling capacitor to remove this DC bias.

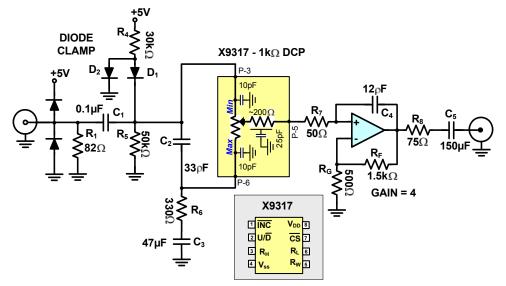

The circuit, in Figure 4, is shown with R<sub>1</sub>= 82 $\Omega$  input termination to ground for a 75 cable input. But why? The 82 $\Omega$  resistor is in parallel with the series combination of 1k DCP and R<sub>6</sub>, 330 $\Omega$  resistor. Thus, it provides about 75 termination for the incoming

cable. There is also an output series resistor  $(75\Omega)$  for backloaded cable driving.

If there is no output cable load then the op amp gain may be set at two by changing the value of the gain and feedback resistors  $R_G$  and  $R_F$  to  ${\rm 1}k\Omega$  each.

#### DCP

The X9317 is a 3-wire up/down logic control DCP and the data sheet will give all the details needed for its proper control operation over the 3-wire interface. Note that we do not cover the 3-wire interface operation in this application note. Please refer to the X9317 data sheet for details:

http://www.intersil.com/data/fn/fn8183.pdf

#### **Test Results**

The testing of this attenuation design was done with  $1V_{P,P}$  AC signal to represent a standard 1Vpp video signal. The DCP was adjusted to a  $1V_{P,P}$  out with different input AC levels and was tested to determine the 3dB bandwidth.

| TABLE 1. FIGURE 4 TEST RESULT |

|-------------------------------|

|-------------------------------|

| INPUT<br>(V <sub>P-P</sub> ) | OUTPUT<br>(V <sub>P-P</sub> ) | BW<br>(MHz) |

|------------------------------|-------------------------------|-------------|

| 0.5                          | 1.0                           | 23.5        |

| 1.0                          | 1.0                           | 17          |

| 1.8                          | 1.0                           | 32          |

Summary: The bandwidth of the design supports the bandwidth requirements for composite video.

Key Design - External comp ( $C_4$  and  $C_2$ ) were added to compensate for the effects of DCP.

FIGURE 4. COMPLETE VIDEO GAIN W/CABLE COMPENSATION

### **Low Noise Video Gain Control**

In this design, we will show how to use a DCP to program the video gain. "Low Noise Video Cable Compensation" on page 6 addresses Cable Compensation for loss of bandwidth due to the cable and "Combination - Programmable Video Gain with Cable Compensation" on page 9 combines the video gain and cable compensation while addressing the signal to noise (SNR) issue.

#### **Video Gain Control Problem**

High performance is a requirement for medical video and projection video applications need low noise to maintain image quality. This video design was done using standard design techniques but was not optimized for low noise, see "Video Gain from 0.5 to Gain of 2" on page 1. In this section, we will develop a new design which will address the low noise requirements.

#### COMPARISON

"Video Gain from 0.5 to Gain of 2" on page 1 uses a fixed gain of 4x and the DCP acting as a voltage divider to attenuate the video for a fixed  $1V_{P,P}$  output. The video as well as the noise is gained by 4x amp to achieve a 1V output level. This has an adverse effect on the normal level video signal-to-noise ratio which is not desirable for good image quality when the input video is 1V. At 0.5V video input the amp noise is the same for both designs and the low noise design is half the amp noise at 1V video input.

#### **Design Considerations**

Implementation of the DCP in the feedback loop as a gain control and not as an attenuator is shown in Figure 2. We have the Video Gain DCP out of the signal path and now as the Video Gain Control pot. The drawback to this design is the DCP stray capacitance and parasitic effects which limit the bandwidth. The parasitics cause gain changes within the frequency band of interest.

We can reduce some of the parasitic capacitance by configurating the DCP. Tying the  $R_W$  wiper and  $R_L$  of the DCP terminal to ground, we have effectively removed these pin's parasitic capacitance. Now we have just the single 10pF of  $R_H$  and the DCP resistance to ground on the (-) summing node (see Figure 5).

FIGURE 5. BASIC ADJUSTABLE VIDEO GAIN USING DCP CONTROL Problem: if you run the pot to the top (Max,  $R_H$ ), you have the ~200 wiper resistance to limit the gain but the wiper resistance can vary up to 30%. We want to limit the gain to about 4. Thus, the overall resistance of DCP leg would need to be about 330 $\Omega$ .

**Solution:** placing a 150 $\Omega$  resistor at the (-) to the Video Amp, we insure a max gain of about 4. This 150 $\Omega$  resistor has a second function, to isolate the stray capacitance of the DCP R<sub>H</sub> pin from the op amp summing node. This is to prevent capacitive loading of the node and the possibility of the op amp going into oscillations.

**Unexpected Issue:** We experience a high frequency gain loss of a few dB with the DCP at a max DC gain of 4, up to about 4MHz.

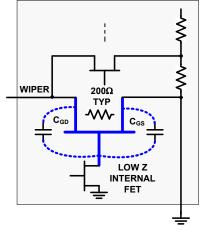

We discovered that looking closer at the DCP wiper FETs, even though it is small, ~200 $\Omega$ , the wiper resistance does influence the overall gain when the DCP is near the Max gain (see Figure 7 the tail off of the lower trace).

FIGURE 6. BASIC DCP WIPER FET

FIGURE 7. EFFECTS OF THE DCP WIPER PARASITICS

In Figure 6 on page 3, the design of these FETs is such that the capacitance Gate to Drain ( $C_{GD}$ ) and Gate to Source ( $C_{GS}$ ) are about the same. Since the wiper capacitance, from this basic model, is about 25pF and the wiper is the drain of this wiper FET, then  $C_{GD}$  is about 25pF. Now looking at the wiper FET when it is at or near  $R_H$  and we are driving the wiper (Drain) with a 5MHz video signal, the  $C_{GD}$ , will form a negative feedback path to the Gate.

As the frequency increases so does the magnitude of the negative feedback, which drives the Gate somewhat out of saturation. As the FET comes out of saturation an FET starts to operate in a non saturated region. This results in lowering the gain of the Video Amp by increasing  $R_G$ . Thus, the wiper becomes a frequency dependent impedance at higher frequency and will have a negative impact on the higher gain settings.

Looking at the lower trace in Figure 7, the top trace is the input and the lower trace the output, Notice that at the right side of the bottom trace, the gain seems to be a lower gain than at the left end. This is the wiper FET changing impedance with frequency.

#### Solution

The Impedance change due to the wiper is small but does impact the overall gain as it becomes more of the controlling impedance of the gain network. By lowering the impedance of the series  $150\Omega$  resistor as the wiper impedance increases, we can maintain the overall value of R<sub>G</sub> constant at the higher gains and higher frequency. A simple method is to parallel some value of capacitance with the  $150\Omega$  such that the impedance will decrease proportionally with the RW impedance increase.

The RC forms a frequency variable impedance to boost the high-end loss. Since we have a 150 $\Omega$  resistor, we need to select a capacitance with <150 $\Omega$  impedance at 5MHz. We found through testing, that using a 360pF in parallel with the 150 $\Omega$  compensated for the DCP wiper impedance (see Figure 8).

FIGURE 8. VIDEO GAIN DCP WITH WIPER COMPENSATION

Note: this solution is for the selected DCP X9317 as other DCPs would have different parasitic.

Using this configuration, we applied a standard NTSC video signal with the active video sweeping from 50kHz to 5.0MHz over a typical short length of cable [<25']. This short length cable does not cause any approachable frequency loss.

The wiper capacitance can be considered as a lumped capacitance but in reality it is distributed. For this application, we found using a lumped capacitance approach was sufficient to support the test results. Yet, we do represent the wiper distributed capacitance using the symbolism as shown in Figure 9 for the 25pF capacitance on the wiper terminal, P-5.

FIGURE 9. DCP PARASITIC CAPACITANCE

We discovered when the wiper is at RL we should have a gain of about 2. However, we found, at high frequencies, we have additional losses of about a few dB. What happens, is the pot should have a resistance of  $1k + 150\Omega$  which yields a DC gain just slightly under 2. Yet, the results show the gain was lower than expected but only at the high frequencies. As with any DCP, the internal resistor string is made up of a series resistors switched in and out of the signal path by FETs. These FETs have a similar feedback issue as does the wiper FET. Thus we need to take a similar approach to solve this problem. Even though the wiper resistance and the DCP's parasitic capacitance form a parallel RC network, this internal 10pF from RH to ground is not sufficient to recover the frequency loss. We need to increase the capacitance and do so by placing an external capacitor from RH to ground. By adding an external 22pF across the (-) summing node to ground, will compensate for the loss at low-end gain. However, the capacitive loading the (-) summing node might cause instability resulting in oscillation. We added 75 $\Omega$  at the summing node in series with the 22pF to isolate the node from the added capacitance but still retain the HF gain compensation. The added 75 $\Omega$  will not affect the DC gain as it is capacitively isolated from ground.

The min and max 10% range of the DCP are slightly over compensated at 5MHz so the most important mid 80% of the range will have a flat frequency response.

FIGURE 10. COMPLETE DETAILED VIDEO GAIN CONTROL

#### Summary

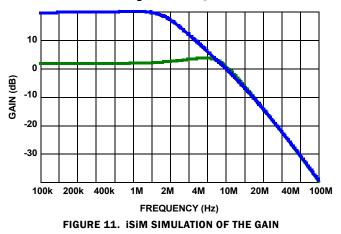

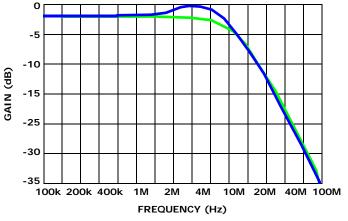

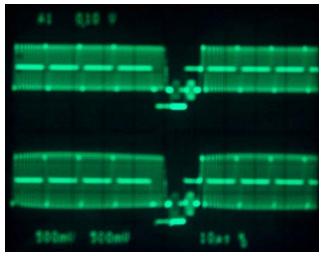

Figure 11, is the results of iSim simulation of Figure 10. The Green trace is with the DCP at  $R_H$ , minimum gain and the Blue trace is with the DCP at  $R_I$ , Maximum gain.

The simulation shows the gain is relatively constant over the video frequency range.

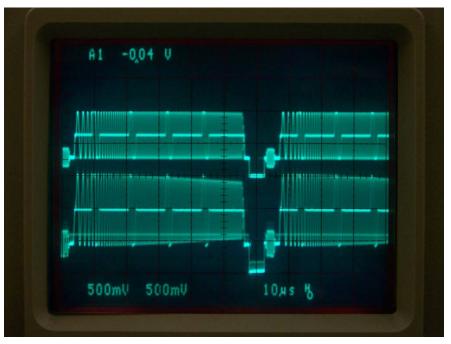

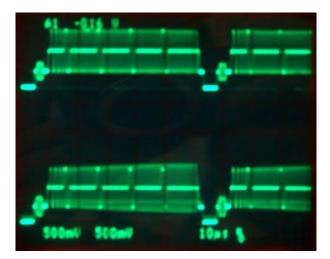

Note: all scope trace scales are 500mV per division for both top and bottom traces. The Video signal spans 0.1MHz to 5MHz. Also, we are only interested in the envelope shape of the video signal from 0.1MHz to 5MHz and not the fine details of the content of these envelopes.

#### Low Noise Gain Control Figure 10 Test Results

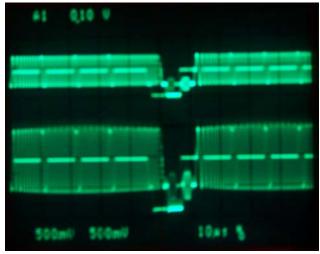

FIGURE 12. VIDEO DCP AT MIN SETTING

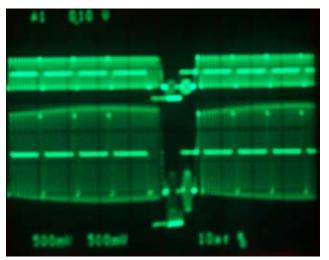

FIGURE 13. VIDEO DCP AT MID SCALE

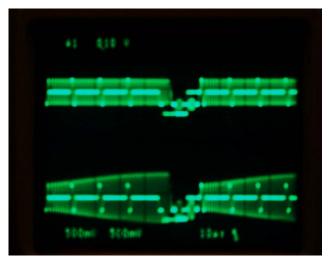

FIGURE 14. VIDEO DCP AT MAX SETTING

Note: Input was double loaded to prevent amplifier clipping.

#### **Test Results**

Figures 12, 13 and 14 Top Trace is a video scan test pattern used for the Input signal. We use this pattern as it covers the required bandwidth. The Bottom Trace is the corresponding output. The envelope shape demonstrates the effect of the design over the desired frequency spectrum: Trace A and B - 500mV/div @10µs/div. As you can see, the gain is effected by the DCP parasitic capacitance to some extent. Yet, it is relative flat over the spectrum. This will support non-professional video applications.

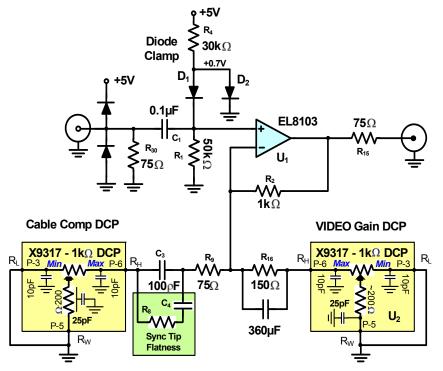

#### **Low Noise Video Cable Compensation**

What if you need Cable Compensation/Peaking but don't need Gain control? The typical video coax used is RG-59. This is a  $75\Omega$

FIGURE 15. BASIC CABLE COMPENSATION NETWORK USING A DCP

cable but at different frequencies will have different losses depending on the different characteristics of the cables. RG-59 comes in low loss, standard loss and hi-loss cable (miniature cable). RF Coax is specifically designed for RF frequencies but has high loss at lower frequencies (under 5MHz) due to the copper clad iron core center conductor.

To correct for cable losses, resulting in losses at higher frequencies, the concept is a simple programmable RC peaking network in the gain leg of the video amp. If we change the gain of the video amp to compensate for the frequency losses of the cable, we can have a system with near flat gain over the desired frequency range, 0.1MHz to 5MHz. Using a DCP, we can compensate for a range of cable peaking problems. Figure 15 is a basic diagram of this concept. The cable compensation video gain amp is set to a gain of 2 with a  $1k\Omega$  resistor from summing node to ground. This circuitry will give us both AC peaking gain control and a small range of Video gain.

Similar to the programmable Video gain circuitry in "Low Noise Video Gain Control" on page 3, but using a series RC network with the DCP replacing the R, we can offer a simple solution. We still have a few similar issues to address:

- 1. Capacitive loading of the op amp summing node which can cause the summing node of the Video Op-Amp to oscillate.

- 2. The selection of the series C for the peaking network plus compensate for the DCP parasitic capacitance.

#### **Capacitive Loading of the Summing Node**

As with the Programmable Video Amp, the series C is isolated from the summing node by placing a resistor in series to the Video Amp (-) input. This 75 $\Omega$  resistor, shown in Figure 16 as R<sub>9</sub>, will isolate the fixed capacitance from the summing node. As in the Video Gain DCP, the 75 $\Omega$  resistor will have no impact on the DC gain as it is isolated from ground via the series capacitor C<sub>3</sub>. The resistor prevents capacitive loading of the node and prevents the possibility of the op amp going into oscillations.

FIGURE 16. CABLE COMPENSATION CIRCUIT

# Selecting the Value of the Series $C_3$ and Dealing with the Parasitic Capacitance

Here we address two issues:

- 1. What is a reasonable size for the series  $C_3$  to address the cable losses on the higher frequencies.

- 2. Reducing the effect of the DCP  $\rm R_{H}$  capacitance on the series  $\rm R_{9}C_{3}$  network.

Using a 1k $\Omega$  DCP in series with 100pF will fix the 3dB point to where we want it (see Figure 16). R<sub>H</sub> capacitance is typically 10pF. Simple rule of thumb gives us a starting point. That is, if you have two capacitors, one is 10x that of the other, the larger one will dominate to where the smaller one can be, for all intensive purposes, ignored.

Using a 100pF cap in series with the  $1k\Omega$  DCP will give us a starting point. Figure 17 is the iSim simulations of the circuit as shown in Figure 16, where the **GREEN** line is the op amp with a gain of 2, no cable compensation [wiper at Minimum]. The **BLUE** line is with the maximum Cable Comp [wiper at Maximum], only the wiper resistance,  $200\Omega$ , in series with the 100pF to ground. Note: The simulation model does not take into account any parasitics; they are meant to validate the basic circuit will be able to program the peaking to meet our needs.

#### Low Noise Video Cable Compensation with DCP Simulation and Actual Test Results

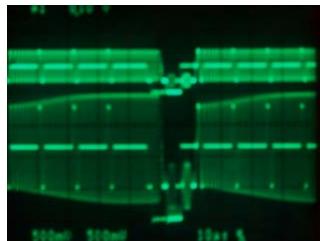

FIGURE 18. CABLE COMPENSATION DCP AT MINIMUM

**Summary:** Figures 18 and 19, The Top Trace is a video scan test pattern used for the Input signal. We use this pattern as it covers the required bandwidth. The Bottom Trace is the corresponding output. The envelope shape demonstrates the effect of the design over the desired frequency spectrum:

Note: The envelope shape, over the 0.1MHz to 5MHz sweep range, shows the results of the cable compensation network of the DCP at minimum and maximum settings. As you can see at the maximum setting (Figure 19), we have the desired results of high frequency peaking.

The Cable Compensation (Figure 16), DCP is capacitive coupled to the peaking circuit, which is used to adjust the RC time constant and thus, the gain peaking.

#### **Comment on Video Coax**

Video coax comes in a variety of types from very low loss to typical loss to high loss. Different cables with different losses will change the length that this design can compensate. This may also change cable compensation needed.

FIGURE 19. CABLE COMPENSATION DCP AT MAXIMUM

RF coax with copper clad iron core center wire will have more DC resistance and more loss at low frequency and can affect performance with video. Special cable compensation is needed with RF coax for the added DC loss.

**Note:** To correct for DC Cable losses, the video gain change is normally small.

#### **Video Cable Compensation DCP Comments**

- 1. This design can be used with input or output coax cables from 250 feet up to about 1000 feet long depending on the quality of the coax cable used.

- 2. Coax Cable losses are not linear [~6dB/octave] over the entire video frequency span. Since the Sync Tip is most susceptible to this problem, you may need to selectively tune the cable compensation network. By using band selective peaking in conjunction with the overall cable compensation network, you can tune the overall performance to match the specific cable used.

FIGURE 20. CABLE COMPENSATION WITH SELECTIVE SYNC TUNING

#### **Improving Sync Tip Flatness and Amplitude**

To improve the sync tip amplitude (see Figure 20), adding  $R_{11}$  in parallel with  $C_3$  will act as band pass boots to recover the lost amplitude on the Sync Tip at the desired frequency. For the flatness, we used a series low pass filter RC network in parallel with C3 to flatten out the Sync Tip. The Cable Comp network  $C_3$ ,  $C_4$ ,  $R_8$ ,  $R_9$  and  $R_{11}$  is dependent on the coax cable used. The values are usually determined by quantitative testing. But, here are a few ranges you can start with to correct the impact of the cable on the sync tip: [The values are set with max cable length on the input and AC DCP set for max compensation]

The R\_{11} in the range of  $\mbox{1} k\Omega$  to  $\mbox{10} k\Omega$  is set for sync tip amplitude.

The C4 ~100pF to 200pF and R8 ~1k $\Omega$  to 4k $\Omega$  are set for sync tip flatness.

The C<sub>3</sub> and R<sub>9</sub> are set for 5MHz amplitude but R<sub>9</sub> should not be <75 $\Omega$  as the DCP R<sub>W</sub> resistance is typically 200 $\Omega$ .

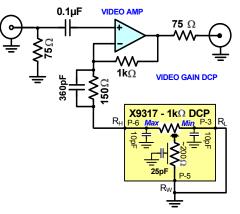

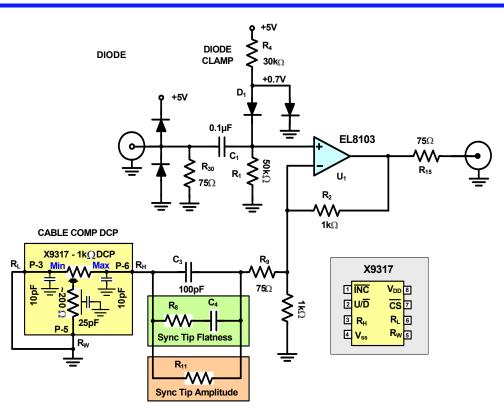

### Combination - Programmable Video Gain with Cable Compensation

Different coax cables have different loss at different frequencies. A simple solution is to combine the "Combination -

Programmable Video Gain with Cable Compensation" on page 9 with the "Low Noise Video Cable Compensation" on page 6. Using this combination will allow compensating a variety of coax cables with good results. Minor changes occur with each combination when combined and are listed as follows (see Figure 22):

- 1. Cable Compensation network The  $1k\Omega$  gain resistor is replaced with the Video Gain DCP network. The Sync Tip Amplitude resistor  $R_{11}$  is also replaced by the same Video Gain DCP network.

- 2. Video Gain network We can eliminate the 22pF to ground on the Programmable Video Gain DCP and replace it with the Cable Comp DCP network.

- 3. This design can be used with input or output coax cables from 250 feet up to about 1000 feet long depending on the quality of the coax cable used. If the max Video DCP and MaxCable Comp DCP settings are used with 1V video input, you might experience noticeable clipping of the HF portion of the video signal. If you do experience unacceptable clipping, try to use more of the coax on the input and less on the output or use better coax and do not use both DCPs at Max settings with 1V video input. Video test signals can have clipping but real video will seldom have clipping so when there are no good alternatives, max DCP settings can be used.

FIGURE 21. COMPLETE VIDEO GAIN WITH CABLE COMPENSATION

Following are the test results with the DCPs at Minimum, Middle and Maximum settings. Figures 22 thru 26 show the results of the design shown in Figure 21 with the two DCPs at the different settings.

#### Test Results Using Figure 21 (Figures 22 thru 26)

Here again we use a video scan test pattern for the input signal. The complete DCP video gain control will yield good video signal quality while maintaining the all important sync tip flatness. The value of this design is, you can control the gain and independently compensate for cable loss using a simple up/down push button DCP for control.

#### **Complete Gain Peaking and Cable Compensation, Figure 21 Test Results**

FIGURE 22. CABLE COMP AT MINIMUM - VIDEO GAIN DCP MINIMUM

FIGURE 23. CABLE COMP AT MINIMUM – VIDEO GAIN AT MIDDLE DCP SETTINGS

FIGURE 24. CABLE COMP AT MINIMUM – VIDEO GAIN AT MAXIMUM DCP SETTINGS

FIGURE 25. CABLE COMP AT MAXIMUM - VIDEO GAIN AT MINIMUM DCP SETTINGS

FIGURE 26. CABLE COMP AT MAXIMUM - VIDEO GAIN AT MAXIMUM DCP SETTINGS

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic "Standard": equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

(Rev.4.0-1 November 2017)

# RENESAS

**Renesas Electronics Corporation**

http://www.renesas.com

#### SALES OFFICES

Refer to "http://www.renesas.com/" for the latest and detailed information.

#### **Renesas Electronics America Inc.**

1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

#### Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Cent Tel: +852-2265-6688, Fax: +852 2886-9022 ntury Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Renesas Electronics Taiwan Co., Ltd.

13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malavsia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338