# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# R8C/25グループ

## 100V系IH制御

### 1. 要約

この資料はR8C/25グループのアウトプットコンペア機能および外部割り込みを使用した100V系IH制御について掲載しています。

#### 2. はじめに

この資料で説明する応用例は次のマイコン、条件での利用に適用されます。

• マイコン : R8C/25 グループ

発振周波数 : 16MHzCPUクロック : 16MHz (fl)タイマカウントソース : 16MHz (fl)

#### 3. CPU占有率

出力変更、停止の処理を含まない、PWM波形出力中のCPU占有率は以下の通りです。

- 外部トリガ入力あり: 24.1% (\*1)

- •外部トリガ入力なし: 6.9% (\*2)

- \*1 Ton幅=2[μs]、外部トリガ入力幅=18[μs]とした場合(周期=20[μs])

- \*2 出力周期を50[µs]とした場合

### 4. 100V系IH制御

### 4.1 概要

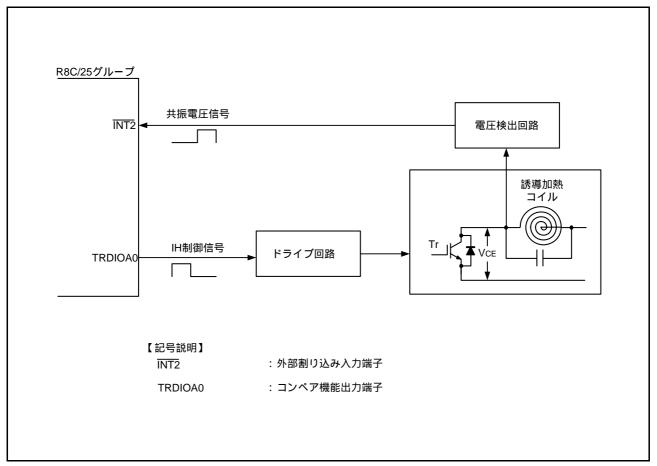

- 1. 図 4.1 に示すように、R8C/25 グループを使用して 100V 系 IH 制御を行います。

- 2. R8C/25グループ内蔵タイマにより、PWM波形を生成し、ドライブ回路へ出力します。

- 3. R8C/25 グループは IGBT のスイッチングにより発生する共振電圧 (VCE) のゼロ電圧点を検出し、PWM 波形を再出力することで 1 石電圧共振方式による IH 制御を行います。

図 4.1 100V 系 IH 制御

#### 4.2 仕様

- 1. 100V系IH制御するためのPWM波形をタイマRDで生成し、TRDIOA0端子より出力します。

- 2. IGBTのスイッチング時に発生する共振電圧信号をフィードバック信号として、外部割込み(INT2) 端子に入力します。この信号の立ち下がりエッジをトリガとして、タイマRDを"0"にクリアし、 PWM波形を再出力します。

- 3. ポート $P1_1 \sim P1_0$ へのスイッチ入力により、出力状態を選択します。スイッチ入力と出力状態の関係を表 4.1 に示します。

表 4.1 スイッチ入力と出力状態の関係

| P1_1 | P1_0 | 出力状態 | Ton[ µ s] |

|------|------|------|-----------|

| L    | L    | 停止   | -         |

| L    | Н    | 出力あり | 2         |

| Н    | L    | 出力あり | 10        |

| Н    | Н    | 出力あり | 30        |

#### 4.3 使用機能

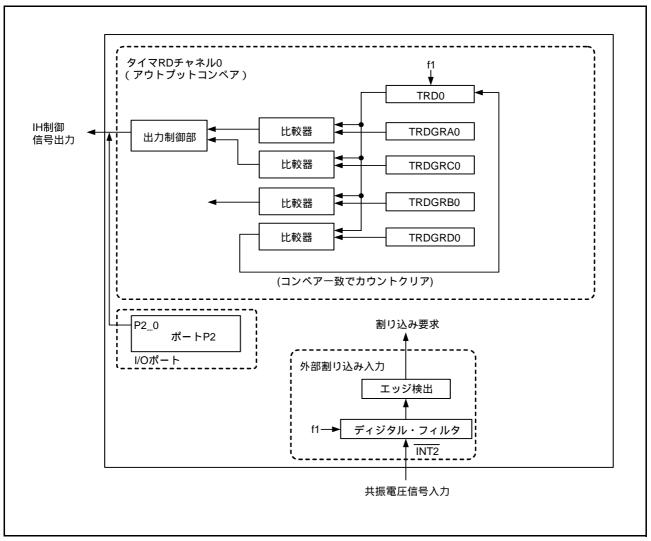

1. 図 4.2 のように R8C/25 グループのタイマ RD (アウトプットコンペア) 外部割込み入力および I/O ポートの各機能を割り付け、100 V 系 IH制御を行います。

図 4.2 100V 系 IH制御ブロック図

以下にR8C/25グループの機能割り付けについて説明します。

- タイマRDチャネル0(アウトプットコンペア): IH制御のためのPWM波形の生成を行い、TRDIOA0 端子より出 力します。

- •外部割り込み入力(INT2): IGBTのスイッチング時に発生する共振電圧信号の立ち下がりエッジを検出し、CPUに割り込みを要求します。

- ●I/Oポート (P2\_0): 初期時のOFF出力 ("L"出力) する際に使用します。

### 4.4 動作説明

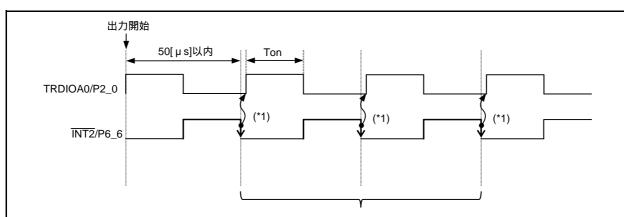

1. 図 4.3 にIH制御出力開始時の動作原理を説明します。図 4.3 に示すようにR8C/25 グループのハードウェア処理、およびソフトウェア処理によりIH制御出力を開始します。

| ハードウェア処理       | ソフトウェア処理                              |

|----------------|---------------------------------------|

| -              | (a) TRD0を初期化(0000h)                   |

|                | (b) TRDGRA0~TRGRD0を設定                 |

|                | (c) TRDIOA0端子を出力許可に設定                 |

|                | (d) IMFD0を"0" にする                     |

|                | (e) IMFB0を"0"にする                      |

|                | (f) TRDGRD0一致による割り込みを許可               |

|                | (g) TRD0をカウント開始(TSTART0=1)            |

|                | (h) タイマRD割り込みを許可                      |

|                | (i) INT2割り込みを許可                       |

| (a) INT2割り込み発生 | (a) TRDGRB0不一致、且つTRDIOA0/P2_0端子"L"レベル |

|                | (b) TRD0を"0"クリア                       |

|                | (c) IMFB0を"0"にする                      |

|                | (d) IMFD0を"0" にする                     |

|                | (e) タイマRD0割り込み要求フラグをクリア               |

TRD0:タイマRDカウンタ0

TRDGRA0: タイマRDジェネラルレジスタA0、TRDGRB0: タイマRDジェネラルレジスタB0 TRDGRC0: タイマRDジェネラルレジスタC0、TRDGRD0: タイマRDジェネラルレジスタD0

\*1 ソフトウェアにより再スタート

【注】出力信号はHigh Active信号とします。

図 4.3 IH制御出力開始時の動作原理

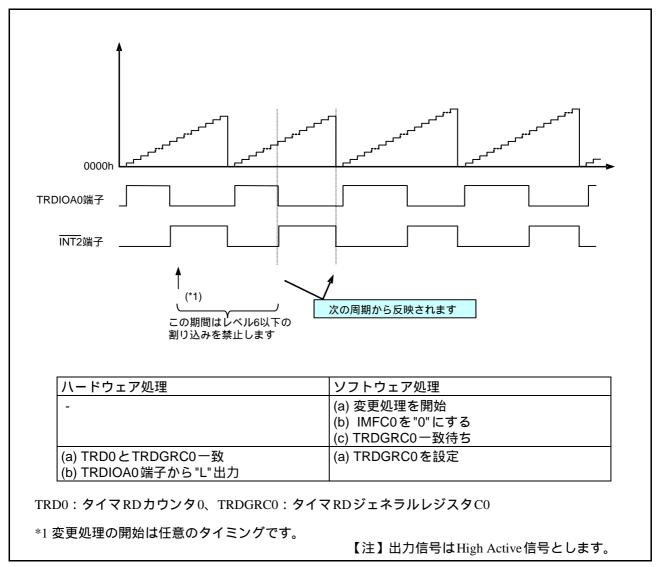

2. 図 4.4にIH制御出力変更時の動作原理について説明します。図 4.4に示すようにR8C/25 グループの ハードウェア処理、およびソフトウェア処理によりIH制御出力を変更します。

図 4.4 IH制御出力変更時の動作原理

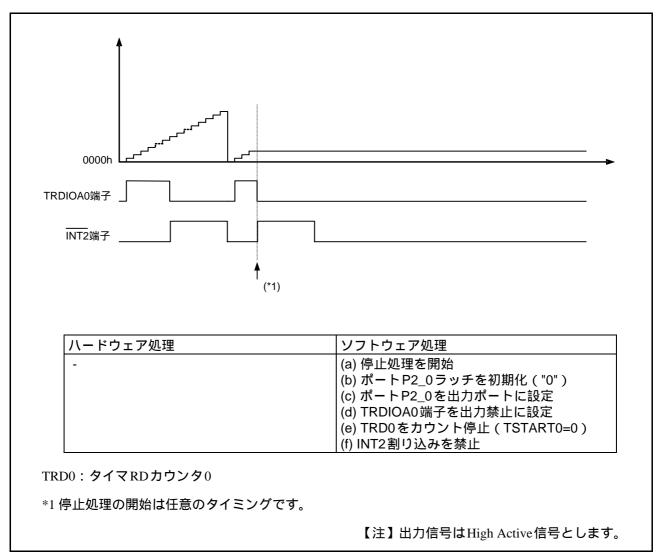

3. 図 4.5にIH制御出力停止時の動作原理について説明します。図 4.5に示すようにR8C/25 グループの ハードウェア処理、およびソフトウェア処理によりIH制御出力を停止します。

図 4.5 IH制御出力停止時の動作原理

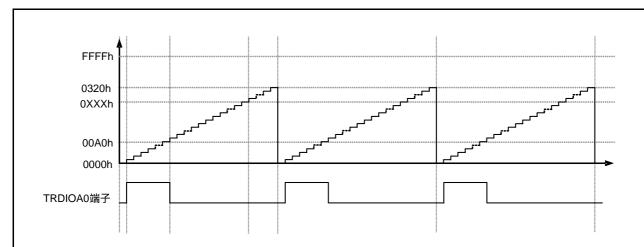

4. PWM 波形はタイマ RD のアウトプットコンペアにより生成し、TRDIOA0 端子から出力します。図 4.6にアウトプットコンペア出力波形の動作原理を説明します。

| ハードウェア処理                                                  | ソフトウェア処理                                                      |

|-----------------------------------------------------------|---------------------------------------------------------------|

| (a) TRD0とTRDGRA0一致<br>(b) TRDIOA0端子から"H"出力                | -                                                             |

| (a) TRD0とTRDGRC0一致<br>(b) TRDIOA0端子から"L"出力                | -                                                             |

| (a) TRD0とTRDGRB0一致                                        | -                                                             |

| (a) TRD0とTRDGRD0一致<br>(b) TRD0を"0000h"<br>(c) タイマRD割り込み発生 | (a) IMFB0を"0"にする<br>(b) IMFD0を"0"にする<br>(c) INT2割り込み要求フラグをクリア |

#### 設定値

TRDGRA0:0000h(遅延なし)、TRDGRC0:00A0h(Ton=10[μs])

TRDGRB0: 0XXXh (再スタート制限時間)、TRDGRD0: 0320h (周期=50[ µ s])

TRD0:タイマRDカウンタ0

TRDGRA0: タイマRDジェネラルレジスタA0、TRDGRB0: タイマRDジェネラルレジスタB0 TRDGRC0: タイマRDジェネラルレジスタC0、TRDGRD0: タイマRDジェネラルレジスタD0

\*1 再スタート制限時間は、INT2割り込み発生時にTRD0をクリアするか否かを判定するための時間です。INT2割り込み発生時にTRDIOA0端子が"L"レベルであっても、TRD0をクリアするまでにタイムラグがあるため、この時間が経過している場合はTRD0をクリアしません。

【注】出力信号はHigh Active信号とします。

図 4.6 アウトプットコンペア出力波形の動作原理

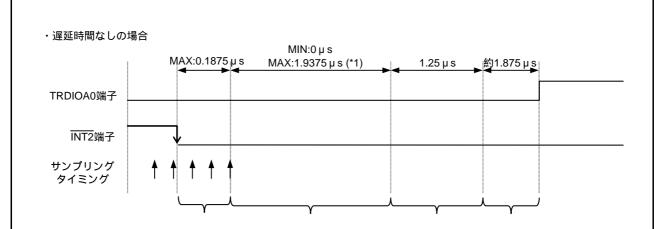

5. 図 4.7 に VCE 電圧信号による IH 出力信号の再起動の動作原理を説明します。図 4.7 に示すように R8C/25 グループのハードウェア処理、およびソフトウェア処理により IH 出力信号の再起動を行います。

| ハードウェア処理                                    | ソフトウェア処理                                                                                                                         |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| (a) ディジタルフィルタ ( f1 )                        | -                                                                                                                                |

| (a) INT2割り込み要求発生<br>(b) INT2割り込み発生待ち(命令実行中) | -                                                                                                                                |

| (a) INT2割り込み発生待ち(割り込みシーケンス)                 | -                                                                                                                                |

| (a) INT2割り込み発生                              | (a) TRDGRB0不一致、且つTRDIOA0/P2_0端<br>子"L" レベル<br>(b) TRD0を"0"クリア<br>(c) IMFB0を"0"にする<br>(d) IMFD0を"0"にする<br>(e) タイマRD0割り込み要求フラグをクリア |

\*1 最小時間は命令実行直後の場合です。最大時間はDIVX命令実行時の場合です。

TRD0: タイマRDカウンタ0、TRDGRB0: タイマRDジェネラルレジスタB0

【注】出力信号はHigh Active信号とします。

#### 図 4.7 IH出力信号の再起動の動作原理

注)図 4.7 に示す通り  $\overline{\text{INT2}}$  端子に立ち下がりエッジが入力されてから、TRDIOA0 端子から出力されるまでの処理遅延時間は、最大で約 $5.3~\mu$  s かかる可能性があります。

また、本アプリケーションノートで使用する割り込み(INT2割り込み、タイマRD0割り込み)以外の割り込みを使用される場合は、上記の時間より処理遅延時間が長くなる可能性がありますのでご注意ください。

### 4.5 使用上の注意事項

- (1) PWM波形出力中に遅延時間および出力周期の変更はできません。

- (2) 設定する遅延時間とは別に、INT2割り込み信号発生からタイマRDカウンタを"0" にクリアするまでの処理遅延についてはP.8を参照ください。

- (3) ユーザで使用される割り込みレベルは、レベル6以下に設定してください。

#### 5. 内部SFR説明

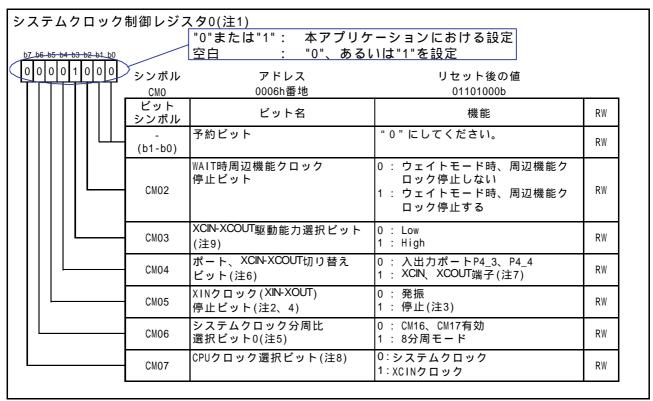

図 5.2 ~ 図 5.28 に本アプリケーションで使用する内部 SFR を示します。

図 5.1 に内部使用 SFR 図の見方を説明します。基本的なレジスタ図の見方はハードウェアマニュアルを参照ください。

また、各レジスタの内容は最新版のハードウェアマニュアルでご確認ください。

図 5.1 内部使用SFR図の見方

| システムクロ                           | コック | 制御レジス        | くタ0(注1)                           |                                                       |    |

|----------------------------------|-----|--------------|-----------------------------------|-------------------------------------------------------|----|

| b7 b6 b5 b4 b3 b2<br>0 0 0 0 1 0 |     | シンボル         | アドレス                              | リセット後の値                                               |    |

| <u>, 1, 1, 1, 1, 1, 1</u>        | ТТ' | CMO          | 0006h番地                           | 01101000b                                             |    |

|                                  |     | ビット<br>シンボル  | ビット名                              | 機能                                                    | RW |

|                                  |     | -<br>(b1-b0) | 予約ビット                             | " 0 " にしてください。                                        | RW |

|                                  |     | CM02         | WAIT時周辺機能クロック<br>停止ビット            | 0: ウェイトモード時、周辺機能クロック停止しない<br>1: ウェイトモード時、周辺機能クロック停止する | RW |

|                                  |     | CM03         | XCIN-XCOUT駆動能力選択ビット<br>(注9)       | 0 : Low<br>1 : High                                   | RW |

|                                  |     | CMO4         | ポート、XCIN-XCOUT切り替え<br>ビット(注6)     | 0 : 入出力ポートP4_3、P4_4<br>1 : XCIN、XCOUT端子(注7)           | RW |

|                                  |     | CM05         | XINクロック (XIN-XOUT)<br>停止ビット(注2、4) | 0 : 発振<br>1 : 停止(注3)                                  | RW |

|                                  |     | CM06         | システムクロック分周比<br>選択ビット0(注5)         | 0 : CM16、CM17有効<br>1 : 8分周モード                         | RW |

|                                  |     | CM07         | CPUクロック選択ビット(注8)                  | 0:システムクロック<br>1:XCINクロック                              | RW |

- 注1.CM0レジスタはPRCRレジスタのPRC0ビットを"1"(書き込み許可)にした後で書き換えてください。

- 注2.CM05ビットは高速オンチップオシレータモード、低速オンチップオシレータモードにするときXINクロッ クを停止させるビットです。XINクロックが停止したかどうかの検出には使えません。XINクロックを停 止させる場合、次のようにしてください。

- (1)OCDレジスタのOCD1 ~ OCD0ビットを "00b"にする。

- (2)OCD2ビットを"1"(オンチップオシレータクロック選択)にする。

- 注3.外部クロック入力時には、クロック発振バッファだけ停止し、クロック入力は受け付けられます。

- 注4.CM05ビットが"1"(XINクロック停止)の場合、P4\_6、P4\_7は入力ポートとして使用できます。

- 注5.ストップモードへの移行時、CM06ビットは"1"(8分周モード)になります。注6.CM04ビットはプログラムで"1"にできますが、"0"にできません。

- 注7. XCINクロックを使用する場合、CM04ビットを"1"にしてください。また、ポートP4\_3、P4\_4は入力ポー トで、プルアップなしにしてください。

- 注8.CM04ビットを"1"(XCIN-XCOUT端子)にし、XCINクロックの発振が安定した後に、CM07ビットを"0"か ら"1"(XCINクロック)にしてください。

- 注9.ストップモードへ移行したとき、CM03ビットは"1"(High)になります。CM03ビットの書き換えは、XCIN クロックの発振が安定しているときに行ってください。

図 5.2 システムクロック制御レジスタ0

| システムクロック                                  | 制御レジス       | くタ1(注1)                      |                                                                   |    |

|-------------------------------------------|-------------|------------------------------|-------------------------------------------------------------------|----|

| b7 b6 b5 b4 b3 b2 b1 b0 0 1 1 1 1 1 0 0 0 | シンボル<br>CM1 | アドレス<br>0007h番地              | リセット後の値<br>00100000b                                              |    |

|                                           | ビット<br>シンボル | ビット名                         | 機能                                                                | RW |

|                                           | CM10        | 全クロック停止制御ビット<br>(注4、7、8)     | 0 : クロック発振<br>1 : 全クロック停止(ストップモード)                                | RW |

|                                           | CM11        | XIN-XOUT内蔵帰還抵抗選択ビット          | 0 : 内蔵帰還抵抗有効<br>1 : 内蔵帰還抵抗無効                                      | RW |

|                                           | CM12        | ビット                          | 0 : 内蔵帰還抵抗有効<br>1 : 内蔵帰還抵抗無効                                      | RW |

|                                           | CM13        | ポートXIN-XOUT切り替え<br>ビット(注7、9) | 0 : 入力ポートP4_6、P4_7<br>1 : XIN-XOUT端子                              | RW |

|                                           | CM14        |                              | 0 : 低速オンチップオシレータ発振<br>1 : 低速オンチップオシレータ停止                          | RW |

|                                           | CM15        | XIN-XOUT駆動能力選択ビット(注2)        | O : LOW<br>1 : HIGH                                               | RW |

|                                           | CM16        | 選択ビット1(注3)                   | <sup>b7 b6</sup><br>0 0 : 分周なしモード<br>0 1 : 2分周モード<br>1 0 : 4分周モード | RW |

|                                           | CM17        |                              | 10:4万周モート 11:16分周モード                                              | RW |

- 注1. CM1レジスタはPRCRレジスタのPRCOビットを"1"(書き込み許可)にした後で書き換えてください。

- 注2. ストップモードへの移行時、CM15ビットは"1"(駆動能力HIGH)になります。

- 注3. CM06ビットが"0"(CM16、CM17ビット有効)の場合、CM16~CM17ビットは有効となります。

- 注4. CM10ビットが"1"(ストップモード)の場合、内蔵している帰還抵抗は無効となります。

- 注5. CM14ビットはOCD2ビットが"0"(XINクロック選択)のとき、"1"(低速オンチップオシレータ停止)にできます。OCD2ビットを"1"(オンチップオシレータクロック選択)にすると、CM14ビットは"0"(低速オンチップオシレータ発振)になります。"1"を書いても変化しません。

- 注6.電圧監視1割り込み、電圧監視2割り込みを使用する場合(デジタルフィルタを使用する場合)、CM14ビットを"0"(低速オンチップオシレータ発振)にしてください。

- 注7.CM10ビットが"1"(ストップモード)の場合、CM13ビットが"1"(XIN-XOUT端子)のとき、XOUT(P4\_7)端子は"H"になります。

- CM13ビットが"0"(入力ポートP4\_6、P4\_7)のとき、P4\_7(XOUT)は入力状態になります。

- 注8. カウントソース保護モード有効時(R8C/25グループハードウェアマニュアルの「13.2 カウントソース保護モード有効時」参照)は、CM10、CM14ビットへ書いても値は変化しません。

- 注9. CM13ビットはプログラムで一度"1"にすると、"0"にはできません。

図 5.3 システムクロック制御レジスタ1

#### 発振停止検出レジスタ(注1) b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 0 0 0 リセット後の値 シンボル アドレス 000Ch番地 00000100b OCD ビット ビット名 機能 RWシンボル 発振停止検出有効ビット 0: 発振停止検出機能無効(注2) (注7) 1: 発振停止検出機能有効 OCD0 RW 0 : 禁止(注2) 1 : 許可 発振停止検出割り込み許可 ビット OCD1 RW システムクロック選択ビット 0 : XINクロック選択(注7) (注4) 1: オンチップオシレータクロック選択 OCD2 RW (注3) クロックモニタビット 0 : XINクロック発振 1 : XINクロック停止 (注5、6) OCD3 RO 予約ビット "0"にしてください。 RW (b7-b4)

- 注1.OCDレジスタは、PRCRレジスタのPRCOビットを"1"(書き込み許可)にした後、書き換えてください。

- 注2.ストップモード、高速オンチップオシレータモード、低速オンチップオシレータモード(XINクロック停止)に移行する前にOCD1~OCD0ビットを"00b"に設定してください。

- 注3. OCD2ビットを " 1 " (オンチップオシレータクロック選択)にすると、CM14ビットは " 0 " (低速オンチップオシレータ発振)になります。

- 注4. OCD2ビットは、OCD1~OCD0ビットが"11b"のときにXINクロック発振停止を検出すると、自動的に "1"(オンチップオシレータクロック選択)に切り替わります。また、OCD3ビットが"1"(XINクロック

- 注5. OCD3ビットはOCD0ビットが"1"(発振停止検出機能有効)のとき有効です。

- 注6. OCD1 ~ OCD0ビットが "00b"のときOCD3ビットは "0"(XINクロック発振)になり、変化しません。

- 注7. 発振停止検出後、XINクロックが再発振した場合の切り替え手順は、R8C/25グループハードウェアマニュアルの「図10.12 低速オンチップオシレータからXINクロックへの切り替え手順」を参照してください。

図 5.4 発振停止検出レジスタ

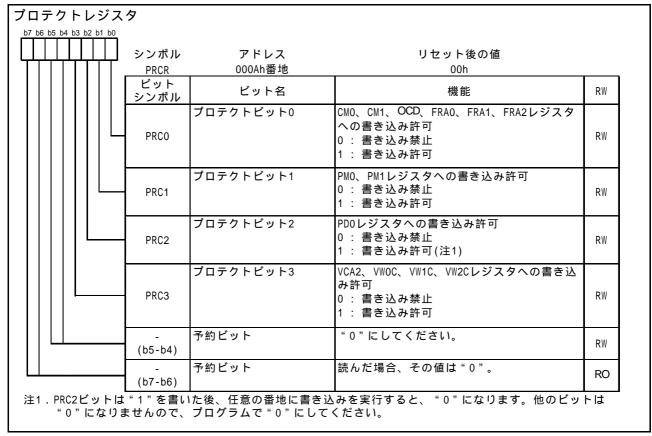

図 5.5 プロテクトレジスタ

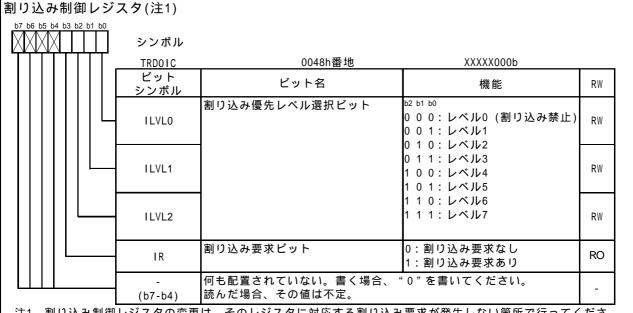

注1.割り込み制御レジスタの変更は、そのレジスタに対応する割り込み要求が発生しない箇所で行ってください。R8C/25グループハードウェアマニュアルの「12.6.6 割り込み制御レジスタの変更」を参照してください。

注2. PMRレジスタのIICSELビットで選択できます。

図 5.6 割り込み制御レジスタ

| 07 66 65 64 | <br>b0 | シンボル         |                                  | リセット後の値                                                           |            |

|-------------|--------|--------------|----------------------------------|-------------------------------------------------------------------|------------|

|             | ١,     | INT2IC       | 0055h番地                          | XX00X000b                                                         |            |

|             |        | ビット<br>シンボル  | ビット名                             | 機能                                                                | RW         |

|             |        | ILVL0        | 割り込み優先レベル選択ビット                   | b2 b1 b0<br>0 0 0 : レベル0 (割り込み禁止)<br>0 0 1 : レベル1<br>0 1 0 : レベル2 | RW         |

|             |        | ILVL1        |                                  | 0 1 0 : レベル2<br>0 1 1 : レベル3<br>1 0 0 : レベル4<br>1 0 1 : レベル5      | RW         |

|             |        | ILVL2        |                                  | 1 1 0 : レベル6<br>1 1 1 : レベル7                                      | RW         |

|             |        | IR           | 割り込み要求ビット                        | 0:割り込み要求なし<br>1:割り込み要求あり                                          | RW<br>(注1) |

|             |        | POL          | 極性切り替えビット(注4)                    | 0:立ち下がりエッジを選択<br>1:立ち上がりエッジを選択(注3)                                | RW         |

|             | =      | -<br>(b5)    | 予約ビット                            | "0"にしてください。                                                       | RW         |

|             |        | -<br>(b7-b6) | 何も配置されていない。書く場合<br>読んだ場合、その値は不定。 | 、"0"を書いてください。                                                     | -          |

- 注1. IRビットは "0"のみ書けます("1"を書かないでください)。

- 注2.割り込み制御レジスタの変更は、そのレジスタに対応する割り込み要求が発生しない箇所で行ってください。R8C/25グループハードウェアマニュアルの「12.6.6 割り込み制御レジスタの変更」を参照してください。

- 注3. INTENレジスタのINTiPLビットが"1"(両エッジ)の場合、POLビットを"0"(立ち下がりエッジを選択) にしてください。

- 注4. POLビットを変更すると、IRビットが"1"(割り込み要求あり)になることがあります。 R8C/25グループハードウェアマニュアルの「12.6.5 割り込み要因の変更」を参照してください。

図 5.7 INT2割り込み制御レジスタ

| 0 1 |  | シンボル<br>INTEN      | アドレス<br>00F9h番地         | リセット後の値<br>00h       |      |

|-----|--|--------------------|-------------------------|----------------------|------|

|     |  | ビット<br>シンボル        | ビット名                    | 機能                   | RW   |

|     |  | INTOEN             | INTO入力許可ビット             | 0:禁止<br>1:許可         | RW   |

|     |  | INTOPL             | TNT0入力極性選択ビット<br>(注1、2) | 0: 片エッジ<br>1: 両エッジ   | RW   |

|     |  | INT1EN             | TNT1入力許可ビット             | 0:禁止<br>1:許可         | RW   |

|     |  | INT1PL             | TNT1入力極性選択ビット<br>(注1、2) | 0: 片エッジ<br>1: 両エッジ   | RW   |

|     |  | INT2EN             | TNT2入力許可ビット             | 0:禁止1:許可             | RW   |

|     |  | INT2PL             | TNT2入力極性選択ビット<br>(注1、2) | 0: 片エッジ<br>1: 両エッジ   | RW   |

|     |  | INT3EN             | TNT3入力許可ビット             | 0:禁止1:許可             | RW   |

|     |  | INT3PL             | INT3入力極性選択ビット<br>(注1、2) | 0: 片エッジ<br>1: 両エッジ   | RW   |

|     |  | (i=0~3)を<br>)にしてく7 | "1" (両エッジ)にする場合、INT     | iICレジスタのPOLビットを"0"(立 | ち下がり |

図 5.8 外部入力許可レジスタ

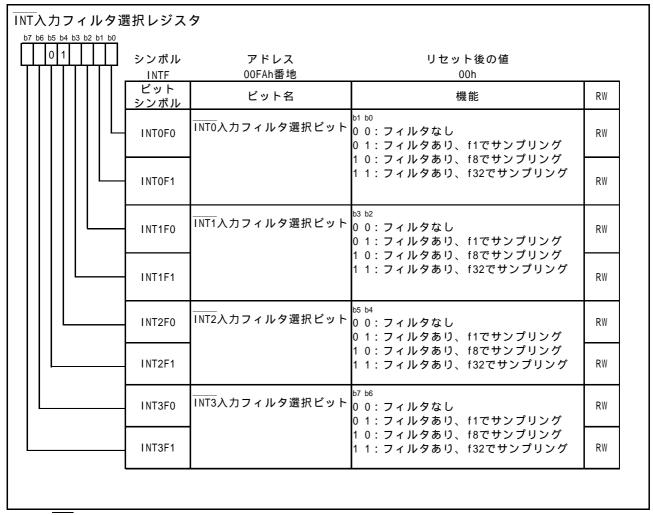

図 5.9 INT入力フィルタ選択レジスタ

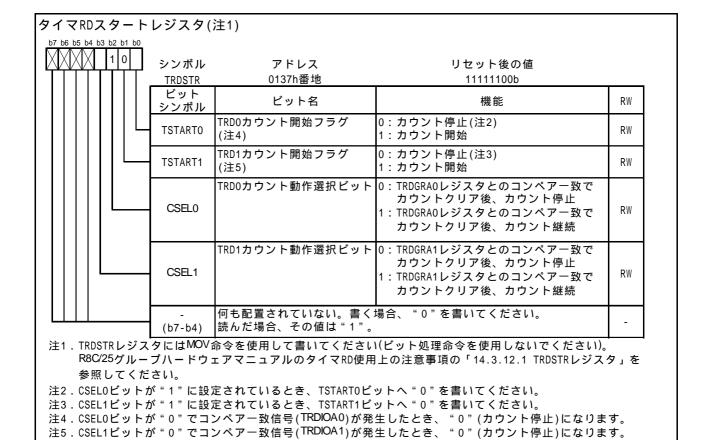

#### 図 5.10 タイマRDスタートレジスタ

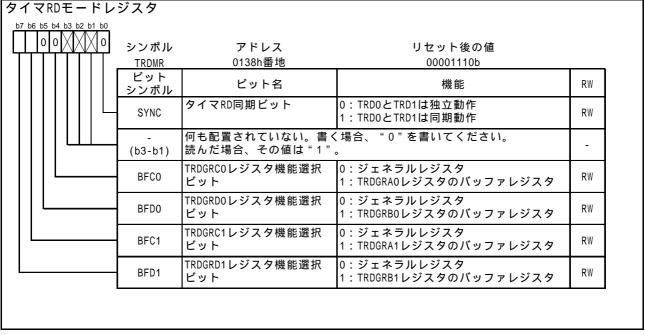

図 5.11 タイマRDモードレジスタ

| 07 b6 b5 b4 b3 b2 b1 |           | アドレス<br>0139h番地                   | リセット後の値<br>10001000b                     |    |

|----------------------|-----------|-----------------------------------|------------------------------------------|----|

|                      | ビットシンボル   | ビット名                              | 機能                                       | RW |

|                      | PWMBO     | TRDIOBO PWMモード選択ビット               | アウトプットコンペア機能では<br>" 0 " (タイマモード)にしてください。 | RW |

|                      | PWMCO     | TRDIOCO PWMモード選択ビット               | アウトプットコンペア機能では<br>"0"(タイマモード)にしてください。    | RW |

|                      | PWMDO     | TRDIODO PWMモード選択ビット               | アウトプットコンペア機能では<br>"0"(タイマモード)にしてください。    | RW |

|                      | -<br>(b3) | 何も配置されていない。書く場合<br>読んだ場合、その値は"1"。 | 合、"0"を書いてください。                           | -  |

|                      | PWMB1     | TRDIOB1 PWMモード選択ビット               | アウトプットコンペア機能では<br>"0"(タイマモード)にしてください。    | RW |

|                      | PWMC1     | TRDIOC1 PWMモード選択ビット               | アウトプットコンペア機能では<br>" 0 " (タイマモード)にしてください。 | RW |

|                      | PWMD1     | TRDIOD1 PWMモード選択ビット               | アウトプットコンペア機能では<br>"0"(タイマモード)にしてください。    | RW |

|                      | -<br>(b7) | 何も配置されていない。書く場合読んだ場合、その値は"1"。     | ・ "0"を書いてください。                           | -  |

図 5.12 タイマRD PWMモードレジスタ

| TRDFCR      | アドレス<br>013Ah番地                                | リセット後の値<br>10000000b                         |    |

|-------------|------------------------------------------------|----------------------------------------------|----|

| ビット<br>シンボル | ビット名                                           | 機能                                           | RW |

| CMDO        | コンビネーションモード選択ビッ<br>ト                           | " 00b " (タイマモード・PWMモード・                      | RW |

| CMD1        | (注1)                                           | PWM3モード)にしてください。                             | RW |

| OLS0        | 正相出力レベル選択ビット<br>(リセット同期PWMモードまたは相<br>補PWMモード時) | アウトプットコンペア機能では無効で<br>す。                      | RW |

| OLS1        | 逆相出力レベル選択ビット<br>(リセット同期PWMモードまたは相<br>補PWMモード時) | アウトプットコンペア機能では無効で<br>す。                      | RW |

| ADTRG       | A/Dトリガ許可ビット<br>(相補PWMモード時)                     | アウトプットコンペア機能では無効です。                          | RW |

| ADEG        | A/Dトリガエッジ選択ビット<br>(相補PWMモード時)                  | アウトプットコンペア機能では無効です。                          | RW |

| STCLK       | 外部クロック入力選択ビット                                  | 0:外部クロック入力無効<br>1:外部クロック入力有効                 | RW |

| PWM3        | PWM3モード選択ビット<br>(注2)                           | アウトプットコンペア機能では<br>"1"(PWM3モード以外)にしてくださ<br>い。 | RW |

図 5.13 タイマRD機能制御レジスタ

| b6 b5 b4 b3 b2 b1 b0 | シンボル<br>TRDOER1 | アドレス<br>013Bh番地 | リセット後の値<br>FFh                                |    |

|----------------------|-----------------|-----------------|-----------------------------------------------|----|

|                      | ビット<br>シンボル     | ビット名            | 機能                                            | RW |

|                      | EA0             | TRDIOA0出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOA0端子はプログ<br>ラマブル入出力ポート) | RW |

|                      | EB0             | TRDIOB0出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOB0端子はプログ<br>ラマブル入出力ポート) | RW |

|                      | EC0             | TRDIOC0出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOC0端子はプログ<br>ラマブル入出力ポート) | RW |

|                      | EDO             | TRDIOD0出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOD0端子はプログ<br>ラマブル入出カポート) | RW |

|                      | EA1             | TRDIOA1出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOA1端子はプログ<br>ラマブル入出カポート) | RW |

|                      | EB1             | TRDIOB1出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOB1端子はプログ<br>ラマブル入出力ポート) | RW |

|                      | EC1             | TRDIOC1出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOC1端子はプログ<br>ラマブル入出力ポート) | RW |

|                      | ED1             | TRDIOD1出力禁止ビット  | 0:出力許可<br>1:出力禁止(TRDIOD1端子はプログ<br>ラマブル入出力ポート) | RW |

図 5.14 タイマRDアウトプットマスタ許可レジスタ1

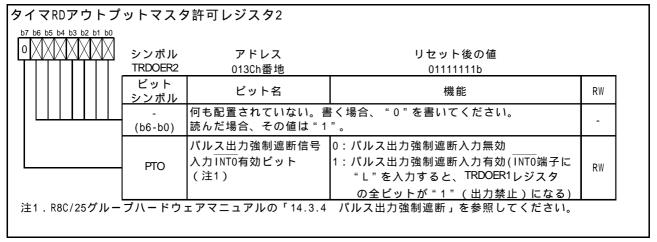

図 5.15 タイマRDアウトプット許可レジスタ2

|   |  | 0<br> | シンボル<br>TRDOCR | アドレス<br>013Dh番地           | リセット後の値<br>00h         |      |

|---|--|-------|----------------|---------------------------|------------------------|------|

|   |  |       | ビット<br>シンボル    | ビット名                      | 機能                     | RW   |

|   |  |       | TOA0           | TRDIOA0出力レベル選択ビット         | 0:初期出力"L"<br>1:初期出力"H" | RW   |

|   |  |       | TOB0           | TRDIOB0出力レベル選択ビット         | 0:初期出力"L"<br>1:初期出力"H" | RW   |

|   |  |       | TOC0           | TRDIOC0初期出力レベル選択ビット       | 0: "L"<br>1: "H"       | RW   |

|   |  |       | TOD0           | TRDIOD0初期出力レベル選択ビット       |                        | RW   |

| L |  |       | TOA1           | TRDIOA1初期出力レベル選択ビット       |                        | RW   |

|   |  |       | TOB1           | TRDIOB1初期出力レベル選択ビット       |                        | RW   |

|   |  |       | TOC1           | TRDIOC1初期出力レベル選択ビット       |                        | RW   |

|   |  |       | TOD1           | TRDIOD1初期出力レベル選択ビット       |                        | RW   |

|   |  | レジス   |                | STRレジスタのTSTARTO、TSTART1ビッ | トがともに"0"(カウント停止)の      | りとき書 |

図 5.16 タイマRDアウトプット制御レジスタ

| 1 1 0 0 0 0 0 0 0 | シンボル<br>TRDCRO | アドレス<br>0140h番地        | リセット後の値<br>00h                                                                                     |    |

|-------------------|----------------|------------------------|----------------------------------------------------------------------------------------------------|----|

|                   | ビット<br>シンボル    | ビット名                   | 機能                                                                                                 | RW |

|                   | ТСКО           |                        | b2 b1 b0<br>0 0 0 : f1<br>0 0 1 : f2<br>0 1 0 : f4                                                 | RW |

|                   | TCK1           |                        | 0 1 1:f8<br>1 0 0:f32<br>1 0 1:TRDCLK入力(注1)                                                        | RW |

|                   | TCK2           |                        | 1 1 0:fOCO40M<br>1 1 1:設定しないでください                                                                  | RW |

|                   | - CKEGO        | 外部クロックエッジ選択<br>ビット(注2) | b4 b3<br>0 0:立ち上がりエッジでカウント<br>0 1:立ち下がりエッジでカウント<br>1 0:両エッジでカウント                                   | RW |

|                   | - CKEG1        |                        | 1 1:設定しないでください                                                                                     | RW |

|                   | - CCLRO        |                        | b7 b6 b5<br>0 0 0: クリア禁止(フリーランニング<br>動作)<br>0 0 1: TRDGRAOのコンペアー致でクリア<br>0 1 0: TRDGRBOのコンペアー致でクリア | RW |

|                   | - CCLR1        |                        | 0 1 1: 同期クリア(他のチャネルのカ<br>ウンタと同時にクリア)(注3)<br>1 0 0: 設定しないでください<br>1 0 1: TRDGRCOのコンペアー致でクリア         | RW |

|                   | - CCLR2        |                        | 1 1 0:TRDGRD0のコンペアー致でクリア<br>1 1 1:設定しないでください                                                       | RW |

図 5.17 タイマRD制御レジスタ0

| タイマRD I/O制御レジスタAO |                  |                               |                                                                                     |    |

|-------------------|------------------|-------------------------------|-------------------------------------------------------------------------------------|----|

| 0 0 0 0 1 0 1 0   | シンボル<br>TRDIORA0 | アドレス<br>0141h番地               | リセット後の値<br>10001000b                                                                |    |

|                   | ビット<br>シンボル      | ビット名                          | 機能                                                                                  | RW |

|                   | IOA0             | TRDGRA制御ビット                   | b1 b0<br>0 0: コンペアー致による端子出力禁止<br>(TRDIOA0端子はプログラマブル<br>入出力ポート)                      | RW |

|                   | IOA1             |                               | 0 1: TRDGRAOのコンペアー致で"L"出力<br>1 0: TRDGRAOのコンペアー致で"H"出力<br>1 1: TRDGRAOのコンペアー致でトグル出力 | RW |

|                   | IOA2             | TRDGRAモード選択ビット<br>(注1)        | アウトプットコンペア機能では"0"(アウト<br>プットコンペア)にしてください。                                           | RW |

|                   | IOA3             | インプットキャプチャ入力<br>切替ビット         | "1"にしてください。                                                                         | RW |

|                   | IOB0             | TRDGRB制御ビット                   | b5 b4<br>0 0: コンペアー致による端子出力禁止<br>(TRDIOB0端子はプログラマブル<br>入出力ポート)                      | RW |

|                   | IOB1             |                               | 0 1:TRDGRB0のコンペアー致で"L"出力<br>1 0:TRDGRB0のコンペアー致で"H"出力<br>1 1:TRDGRB0のコンペアー致でトグル出力    | RW |

|                   | IOB2             | TRDGRBモード選択ビット<br>(注2)        | アウトプットコンペア機能では " 0 " (アウト<br>プットコンペア)にしてください。                                       | RW |

|                   | -<br>(b7)        | 何も配置されていない。書<br>読んだ場合、その値は"1" | く場合、"0"を書いてください。<br>。                                                               | -  |

- 注1. TRDMRレジスタのBFC0ビットで"1"(TRDGRA0レジスタのバッファレジスタ)を選択した場合、TRDIORA0レジスタのIOA2ビットとTRDIORC0レジスタのIOC2ビットの設定を同じにしてください。

- 注2. TRDMRレジスタのBFD0ビットで"1"(TRDGRB0レジスタのバッファレジスタ)を選択した場合、TRDIORA0レジスタのIOB2ビットとTRDIORC0レジスタのIOD2ビットの設定を同じにしてください。

図 5.18 タイマRD I/O制御レジスタA0

| タイマRD I/O制御レジスタCO        |                                                                                                                                                                                                                                  |                        |                                                                                                                         |    |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|----|--|

| b7 b6 b5 b4 b3 b2 b1 b0  |                                                                                                                                                                                                                                  |                        |                                                                                                                         |    |  |

|                          | シンボル<br>TRDIORC0                                                                                                                                                                                                                 | アドレス<br>0142h番地        | リセット後の値<br>10001000b                                                                                                    |    |  |

|                          | ビット<br>シンボル                                                                                                                                                                                                                      | ビット名                   | 機能                                                                                                                      | RW |  |

|                          | · IOC0                                                                                                                                                                                                                           | TRDGRC制御ビット            | ы ы ы<br>0 0: コンペアー致による端子出力禁止<br>0 1: TRDGRC0のコンペアー致で"L"出力                                                              | RW |  |

|                          | IOC1                                                                                                                                                                                                                             |                        | 1 0: TRDGRC0のコンペアー致で"H"出力<br>1 1: TRDGRC0のコンペアー致でトグル出力                                                                  | RW |  |

|                          | IOC2                                                                                                                                                                                                                             | TRDGRCモード選択ビット<br>(注1) | アウトプットコンペア機能では " 0 " (アウトプットコンペア)にしてください                                                                                | RW |  |

|                          | IOC3                                                                                                                                                                                                                             | TRDGRCレジスタ機能選択<br>ビット  | 0:TRDIOA出力レジスタ<br>(R8C/25シリーズハードウェアマニュアルの<br>「14.3.6.1 TRDGRC0、TRDGRD0<br>レジスタの出力端子変更」参照)<br>1:ジェネラルレジスタまたはバッファ<br>レジスタ | RW |  |

|                          | IOD0                                                                                                                                                                                                                             | TRDGRD制御ビット            | b5 b4<br>0 0:コンペアー致による端子出力禁止<br>0 1:TRDGRD0のコンペアー致で"L"出力                                                                | RW |  |

|                          | IOD1                                                                                                                                                                                                                             |                        | 1 0: TRDGRD0のコンペアー致で"H"出力<br>1 1: TRDGRD0のコンペアー致でトグル出力                                                                  | RW |  |

|                          | IOD2                                                                                                                                                                                                                             | TRDGRDモード選択ビット<br>(注2) | アウトプットコンペア機能では " 0 " (アウト<br>プットコンペア)にしてください                                                                            | RW |  |

|                          | IOD3                                                                                                                                                                                                                             | TRDGRDレジスタ機能選択<br>ピット  | 0:TRDIOB出力レジスタ<br>(R8C/25シリーズハードウェアマニュアルの<br>「14.3.6.1 TRDGRC0、TRDGRD0<br>レジスタの出力端子変更」参照)<br>1:ジェネラルレジスタまたはバッファ<br>レジスタ | RW |  |

| ジスタのIOA2<br>注2.TRDMRレジスク | 注1. TRDMRレジスタのBFC0ビットで"1"(TRDGRA0レジスタのバッファレジスタ)を選択した場合、TRDIORA0レジスタのIOA2ビットとTRDIORC0レジスタのIOC2ビットの設定を同じにしてください。<br>注2. TRDMRレジスタのBFD0ビットで"1"(TRDGRB0レジスタのバッファレジスタ)を選択した場合、TRDIORA0レジスタのIOB2ビットとTRDIORC0レジスタのIOD2ビットの設定を同じにしてください。 |                        |                                                                                                                         |    |  |

図 5.19 タイマRD I/O制御レジスタC0

| イマRDステータ                | アスレジスク         | 70                           |                                                                                            |    |

|-------------------------|----------------|------------------------------|--------------------------------------------------------------------------------------------|----|

| 07 66 65 64 63 62 61 60 | シンボル<br>TRDSRO | アドレス<br>0143h番地              | リセット後の値<br>11100000b                                                                       |    |

|                         | ビット<br>シンボル    | ビット名                         | 機能                                                                                         | RW |

|                         | IMFA           | インプットキャプチャ/コンペ<br>アー致フラグA    | [ " 0 " になる要因]<br>読んだ後、 " 0 " を書く。 (注2)<br>[ " 1 " になる要因]<br>TRDOとTRDGRAOの値が一致したとき。        | RW |

|                         | - IMFB         | インプットキャプチャ/コンペ<br>アー致フラグB    | [ " 0 " になる要因]<br>読んだ後、 " 0 " を書く。 (注2)<br>[ " 1 " になる要因]<br>TRDOとTRDGRBOの値が一致したとき。        | RW |

|                         | IMFC           | インプットキャプチャ/コンペ<br>アー致フラグC    | [ " 0 " になる要因]<br>読んだ後、 " 0 " を書く。(注2)<br>[ " 1 " になる要因]<br>TRDOとTRDGRCOの値が一致したとき。<br>(注3) | RW |

|                         | - IMFD         | インプットキャプチャ/コンペ<br>アー致フラグD    | [ " 0 " になる要因]<br>読んだ後、 " 0 " を書く。(注2)<br>[ " 1 " になる要因]<br>TRDOとTRDGRDOの値が一致したとき。<br>(注3) | RW |

|                         | OVF            | オーバフローフラグ                    | [ " 0 " になる要因]<br>読んだ後、 " 0 " を書く。 (注2)<br>[ " 1 " になる要因]<br>TRDOがオーパフローしたとき。              | RW |

|                         | UDF            | アンダフローフラグ(注1)                | アウトプットコンペア機能では無効です                                                                         | RW |

|                         | -<br>(b7-b6)   | 何も配置されていない。書く場読んだ場合、その値は"1"。 | 合、"0"を書いてください。                                                                             | -  |

- 注1. TRDSR0レジスタのb5には何も配置されていません。b5に書く場合、"0"を書いてください。読んだ場合、その値は"1"です。

- 注2. 書き込み結果は次のようになります。

- ・読んだ結果が"1"の場合、同じビットに"0"を書くと"0"になります。

- ・読んだ結果が"0"の場合、同じビットに"0"を書いても変化しません(読んだ後で、"0"から"1"に変化した場合、"0"を書いても"1"のままです)。

- ・"1"を書いた場合は変化しません。

- 注3. TRDMRレジスタのBFjiビット(j=CまたはD)が"1"(TRDGRjiはバッファレジスタ)の場合を含む。

図 5.20 タイマRDステータスレジスタ0

| b7 b6 b5 b4 b | 0 0 0 0 | シンボル<br>TRDIERO | アドレス<br>0144h番地                   | リセット後の値<br>11100000b                                         |    |

|---------------|---------|-----------------|-----------------------------------|--------------------------------------------------------------|----|

|               |         | ビット<br>シンボル     | ビット名                              | 機能                                                           | RW |

|               |         | IMIEA           | インプットキャプチャ/コンペア<br>一致割り込み許可ビットA   | 0:IMFAビットによる割り込み(IMIA)<br>禁止<br>1:IMFAビットによる割り込み(IMIA)<br>許可 | RW |

|               |         | IMIEB           | インプットキャプチャ/コンペア<br>一致割り込み許可ビットB   | 0:IMFBビットによる割り込み(IMIB)<br>禁止<br>1:IMFBビットによる割り込み(IMIB)<br>許可 | RW |

|               |         | IMIEC           | インプットキャプチャ/コンペア<br>一致割り込み許可ビットC   | 0:IMFCビットによる割り込み(IMIC)<br>禁止<br>1:IMFCビットによる割り込み(IMIC)<br>許可 | RW |

|               |         | IMIED           | インプットキャプチャ/コンペア<br>一致割り込み許可ビットD   | 0:IMFDビットによる割り込み(IMID)<br>禁止<br>1:IMFDビットによる割り込み(IMID)<br>許可 | RW |

|               |         | OVIE            | オーバフロー/アンダフロー割り<br>込み許可ビット        | 0:OVFビットによる割り込み(OVI)<br>禁止<br>1:OVFビットによる割り込み(OVI)<br>許可     | RW |

|               |         | -<br>(b7-b5)    | 何も配置されていない。書く場合<br>読んだ場合、その値は"1"。 | 、"0"を書いてください。                                                | -  |

図 5.21 タイマRD割り込み許可レジスタ0

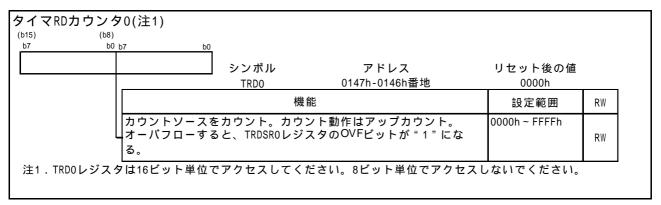

図 5.22 タイマRDカウンタ0

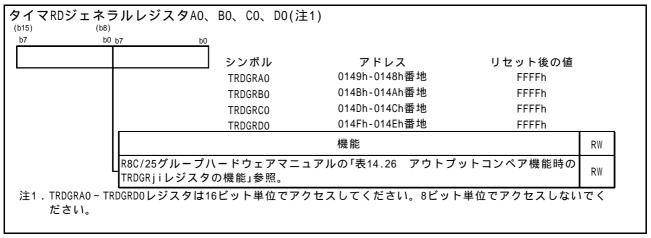

図 5.23 タイマRDジェネラルレジスタA0、B0、C0、D0

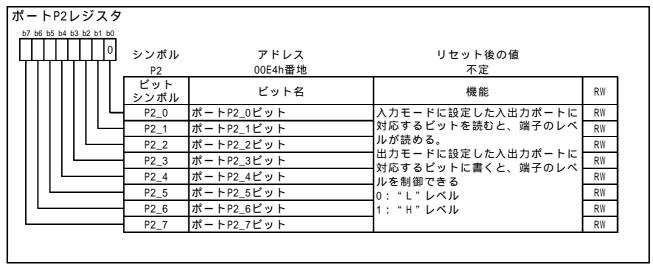

図 5.24 ポートP2 レジスタ

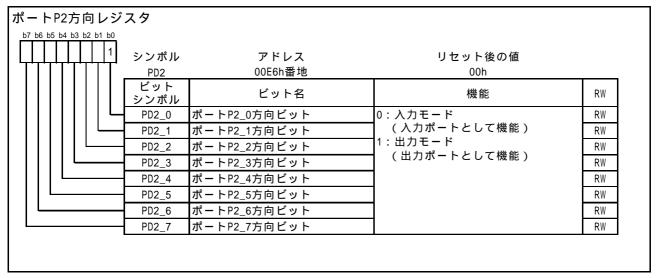

図 5.25 ポートP2 方向レジスタ

図 5.26 ポートP6 レジスタ

図 5.27 ポートP6方向レジスタ

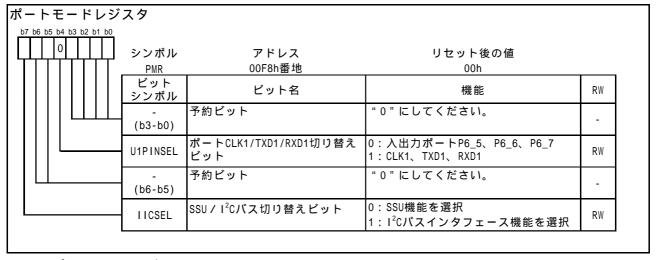

図 5.28 ポートモードレジスタ

## 6. ソフトウェア説明

### 6.1 モジュール説明

表 6.1 に本アプリケーションにおけるモジュール説明を示します。 本アプリケーションでは、unsigned charをu08、unsigned shortをu16と定義します。

### 表 6.1 モジュール説明

| モジュール名:メインルーチン                                                | void main ( void )                      |  |  |  |

|---------------------------------------------------------------|-----------------------------------------|--|--|--|

| 引数:無し                                                         | 戻り値:無し                                  |  |  |  |

| 機能:必要に応じてIGBT処理を行います。ポートP1                                    | 入力処理の結果によりIGBT駆動のTonを選択しま               |  |  |  |

| <u>す。</u>                                                     |                                         |  |  |  |

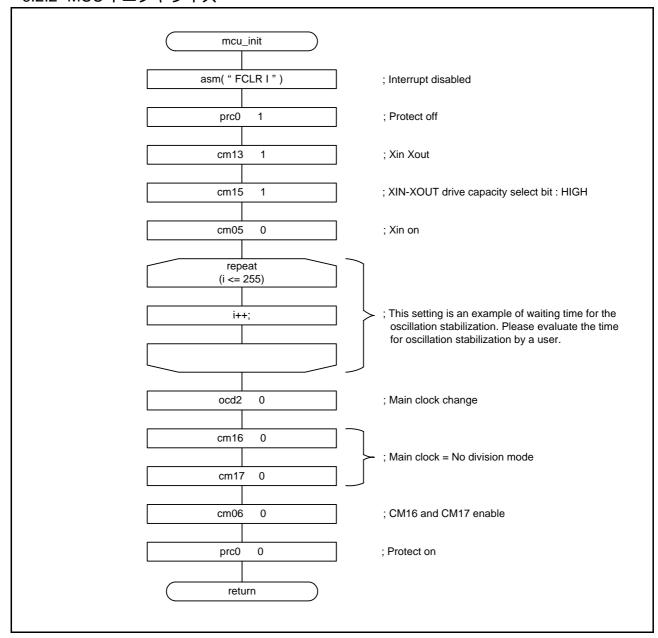

| モジュール名: MCUイニシャライズ                                            | void mcu_init (void)                    |  |  |  |

| 引数:無し                                                         | 戻り値:無し                                  |  |  |  |

| 機能:オンチップオシレータクロックからメインクロ                                      |                                         |  |  |  |

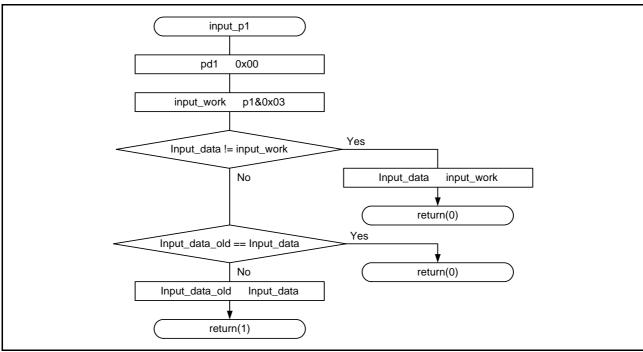

| モジュール名:ポートP1入力処理ルーチン                                          | static u08 input_p1 ( void )            |  |  |  |

| 引数:無し                                                         | 戻り値:入力変化有無                              |  |  |  |

| 機能:ポートP1_1~P1_0を入力します。                                        |                                         |  |  |  |

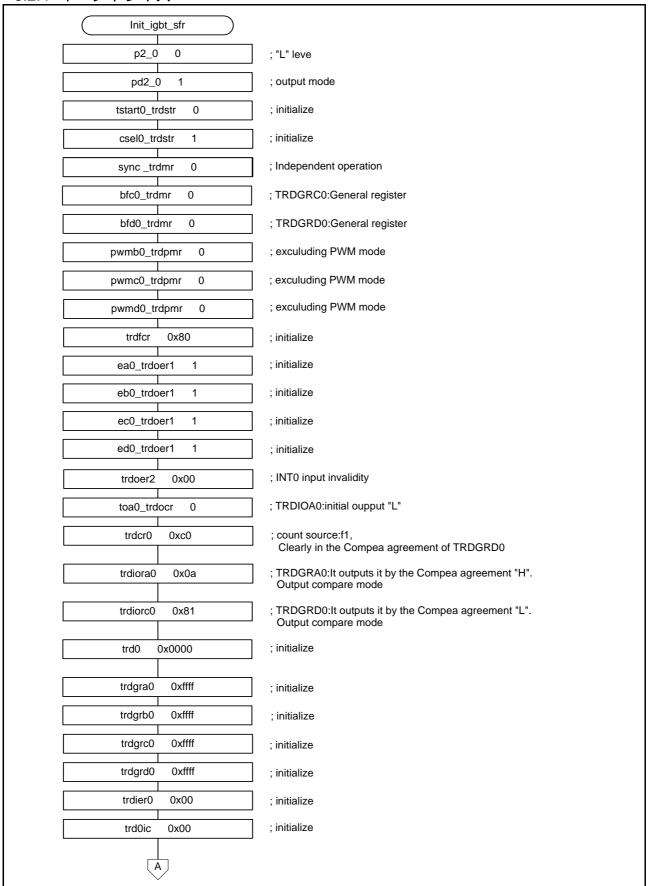

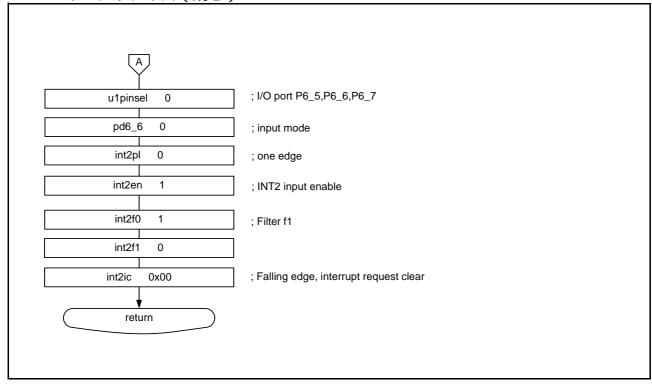

| モジュール名:イニシャライズ                                                | void Init_igbt_sfr ( void )             |  |  |  |

| 引数:無し                                                         | 戻り値:無し                                  |  |  |  |

| 機能:制御に関係するSFRの設定を行います。                                        |                                         |  |  |  |

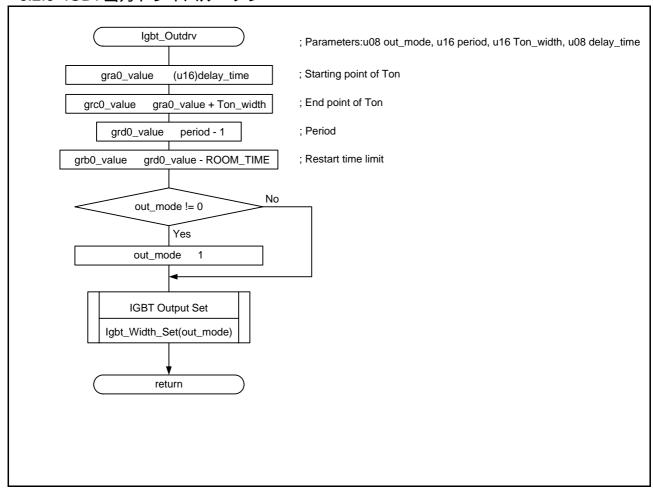

| モジュール名:IGBT出力ドライバルーチン                                         | void Igbt_Outdrv ( u08, u16, u16, u08 ) |  |  |  |

| 引数:出力モード(0:出力停止、0以外:出力開始                                      | 戻り値:無し                                  |  |  |  |

| /変更 )                                                         |                                         |  |  |  |

| :周期                                                           |                                         |  |  |  |

| :Ton幅<br>:遅延時間                                                |                                         |  |  |  |

| 機能:各ジェネラルレジスタに設定する値を計算しま                                      | ।<br>= <del>d</del>                     |  |  |  |

| 出力中は周期を変えないでください。                                             |                                         |  |  |  |

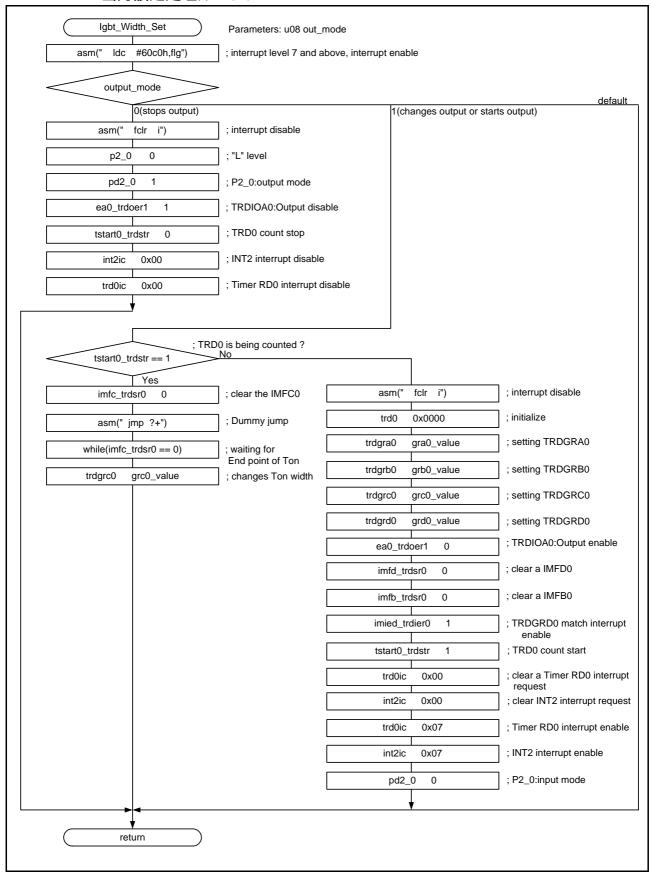

| モジュール名:IGBT出力設定処理ルーチン                                         | void lgbt_Width_Set ( u08 )             |  |  |  |

| 引数:出力モード(0:出力停止、1:出力開始/変                                      | 戻り値:無し                                  |  |  |  |

| 更 )                                                           |                                         |  |  |  |

| 機能:IGBT出力開始、変更または停止の設定処理を                                     |                                         |  |  |  |

|                                                               | しています。(ソフトウェア割り込み番号:#32)                |  |  |  |

| 出力中は周期を変えないでください。                                             | Lucid Faadhaalu ist (usid )             |  |  |  |

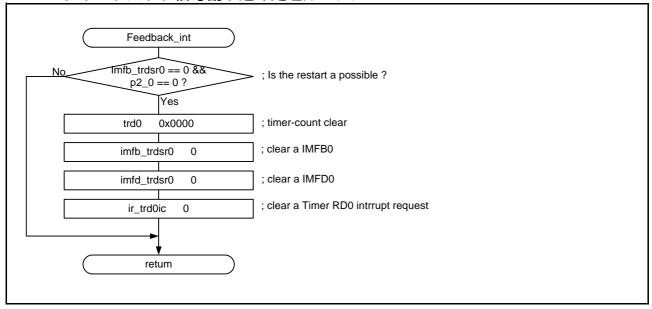

| モジュール名:INT2割り込み                                               | void Feedback_int ( void )              |  |  |  |

| (フィードバック信号割り込み処理ルーチン)<br>引数:無し                                | <br>  戻り値:無し                            |  |  |  |

| 51数:無し<br> 機能:フィードバック信号割り込みです。                                | 広ソ心・無し                                  |  |  |  |

| 機能:フィードハック信号割り込みです。<br>フィードバック信号(共振電圧信号)によりIH制御出力信号を再スタートします。 |                                         |  |  |  |

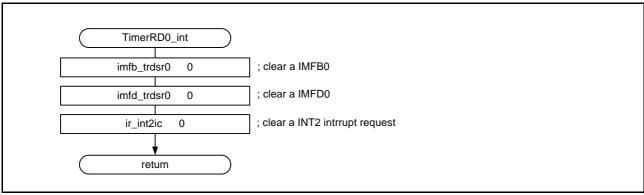

| モジュール名:タイマRDO割り込み処理ルーチン                                       | void TimerRD0_int(void)                 |  |  |  |

| 引数:無し                                                         | 戻り値:無し                                  |  |  |  |

| 機能:IH制御出力の1周期の割り込みです。コンペア                                     |                                         |  |  |  |

| TANDO : MINISTER AND TO TO TO TO                              | 2,7 7 7 20( 20 2 / 7 / 0 0 / 6          |  |  |  |

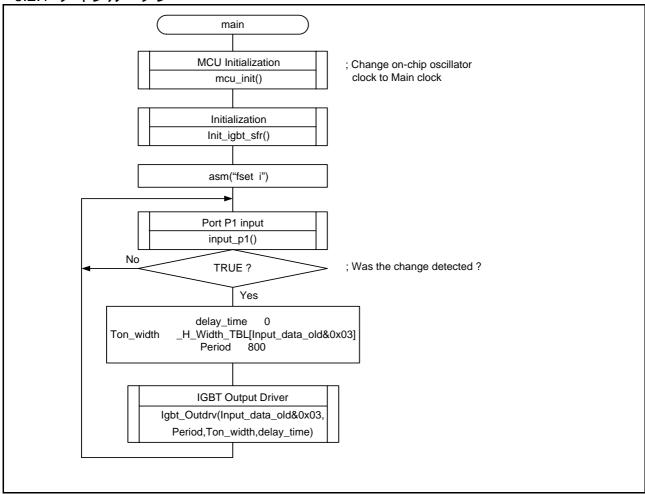

## 6.2 フローチャート

## 6.2.1 メインルーチン

## 6.2.2 MCUイニシャライズ

## 6.2.3 ポートP1入力処理ルーチン

### 6.2.4 イニシャライズ

## 6.2.5 イニシャライズ (続き)

## 6.2.6 IGBT出力ドライバルーチン

### 6.2.7 IGBT出力設定処理ルーチン

## 6.2.8 フィードバック信号割り込み処理ルーチン

## 6.2.9 タイマRDO割り込み処理ルーチン

### 7. 参考プログラム

参考プログラムは、ルネサステクノロジホームページから入手してください。 R8C/Tinyシリーズのトップページの画面左メニュー「アプリケーションノート」をクリックしてください。

### 8. 参考ドキュメント

ハードウェアマニュアル R8C/25グループハードウェアマニュアル (最新版をルネサス テクノロジホームページから入手してください。)

テクニカルニュース / テクニカルアップデート (最新の情報をルネサス テクノロジホームページから入手してください。)

## ホームページとサポート窓口

ルネサス テクノロジホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry csc@renesas.com

| 改訂記録 | R8C/25グループ 100V系IH制御 |

|------|----------------------|

|------|----------------------|

| Rev. | 発行日        | 改訂内容 |      |

|------|------------|------|------|

|      |            | ページ  | ポイント |

| 1.00 | 2007.10.31 | -    | 初版発行 |

#### 🗕 本資料ご利用に際しての留意事項 🖣

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認頂きますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意下さい。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断して下さい。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会下さい。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないで下さい。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行なうもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10. 弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウエアおよびソフトウエア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特にマイコンソフトウエアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願い致します。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故につきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固く お断り致します。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会下さい。

© 2007. Renesas Technology Corp., All rights reserved.