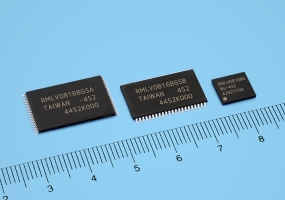

ルネサス エレクトロニクス株式会社(代表取締役会長兼CEO:作田 久男、以下ルネサス)はこのたび、当社SRAMの主力製品であるAdvanced Low Power SRAM(以下Advanced LP SRAM)で、回路線幅に110nm(ナノメートル)の微細プロセスを採用した8M(メガ)ビット品を開発し、「RMLV0816Bシリーズ」「RMLV0808Bシリーズ」の名称で、合計5品種のサンプル出荷を14年12月から順次開始致します。

ソフトエラー(注1)フリー/ラッチアップ(注2))フリーを実現できるAdvanced LP SRAMシリーズにおいて、既に回路線幅110nmの微細プロセスを適用した4Mビット品の量産を13年12月から開始しており、今回新たに8Mビット品をリリース致します。もちろん、150nmプロセスを採用した当社従来品と同等のソフトエラー率を実現した高信頼性製品となっています。

また、25℃時のスタンバイ電流が2μA(マイクロアンペア)と低消費電力を実現しているため、バッテリー等でデータを保持する用途などに適しております。

新製品のサンプル価格は、いずれも1040円/個となっており、15年1月から順次量産を開始して参ります。

当社の低消費電力SRAMは、産業、OA、通信、車載、民生といった様々な分野において幅広くご採用頂いており、世界シェアは2013年に業界第1位を獲得しております(注3)。昨今、ユーザーシステムの高性能化/高機能化に伴い、システム全体の信頼性向上が重要となっています。とりわけ、システムプログラムや課金データなどの重要情報が格納されるSRAMへの高信頼性が求められており、特にアルファ線や宇宙線中性子線によって引き起こされるソフトエラーへの対策が重視されています。

当社Advanced LP SRAMは、メモリセルの記憶ノード(注4)にキャパシタ(注5)を付加しているため、ソフトエラー耐性が極めて高い構造になっております。一般的なソフトエラー対策としては、発生したソフトエラーをSRAMやユーザーシステム内部に組み込んだECC(Error Correcting Code)回路で訂正する方法がありますが、ECCの性能によっては複数ビットのエラーを訂正できないなど、エラー訂正に限界が生じます。そこでAdvanced LPSRAMではソフトエラーの発生そのものを抑制する構造的対策を講じており、現在量産している150nmプロセスAdvanced LP SRAMのシステムソフトエラー評価結果からも、実質ソフトエラーフリーと言える耐性を確認しております。

また、SRAMセルのロードトランジスタ(Pチャネル)をポリシリコンTFT(注6)で形成し、シリコン基板上に形成されたNチャネルMOSトランジスタの上層に積層されるため、下地のシリコン基板上にはNチャネルトランジスタのみで形成されています。これによりメモリ領域内では寄生サイリスタ構造は存在せず、原理的にラッチアップが発生しない構造となっています。

これらのことからAdvanced LP SRAMは、一般的なメモリセル構造であるFull CMOSタイプ(注7)の製品に比べ極めて信頼性の高いSRAMであり、FA機器、計測器、スマートグリッド関連機器や交通システムなどの高い信頼性を必要とする機器の更なる高性能化及び高信頼性化に貢献することができます。

さらに、Advanced LP SRAMはSRAMのポリシリコンTFT積層技術とスタックトキャパシタ技術の融合により、セルサイズの小型化を実現しております。例えば、110nm Advanced LP SRAMのセルサイズは65nmプロセスによるFull CMOSタイプに匹敵します。

ルネサスは今後、新製品(8Mビット製品)の積極的な拡販活動を行うとともに、110nmプロセスにより16Mビットの新製品追加を実施してラインナップの強化を図って参ります。

新製品の主な仕様、及び、リリース時期については別紙をご参照ください。

低消費電力SRAMの製品情報は、https://www.renesas.com/ja/products/memory/low-power-sram.htmlをご覧ください。

以 上

(注1)ソフトエラー:

シリコン基板に外部からアルファ線や中性子線が入射した時、基板中で発生した電荷によりメモリの情報が失われる現象。半導体素子の物理的な故障などの再現 性のあるハードエラーとは異なり、システム側でデータを再書込みすれば元に戻すことができる再現性の無いエラー。一般に、プロセスが微細化されるとソフト エラーの発生率は増加する。

(注2)ラッチアップ:

CMOSトランジスタのウェル、Si基板、P型拡散層、N型拡散層により形成されるNPN、PNP構造(寄生バイポーラトランジスタ)が、電源や入力端子からの過電圧によりオン状態となり、電源と接地の間に大電流が流れる現象。

(注3)当社調べ

(注4)記憶ノード:

メモリセル内部で、情報を"High"又は"Low"の電位として記憶しているフリップフロップの回路節点。

(注5)スタックトキャパシタ:

二電極をポリシリコンや金属で形成したキャパシタ。シリコン基板上のMOSトランジスタ上層に形成され、メモリセルの小面積化に有効である。

(注6)TFT(Thin Film Transistor):

薄膜ポリシリコンで形成したトランジスタ。SRAMのロードトランジスタとしてシリコン基板上のMOSトランジスタ上層に形成され、メモリセルの小面積化に有効である。

(注7)Full CMOSタイプ:

シリコン基板の同一面上にPチャネルMOSトランジスタとNチャネルMOSトランジスタの計6素子を有するSRAMメモリセル構造。面積が大きく、ラッチアップのリスクもある。

* 本リリース中の製品名やサービス名は全てそれぞれの所有者に属する商標または登録商標です。

ニュースリリースに掲載されている情報(製品価格、仕様等を含む)は、発表日現在の情報です。 その後予告なしに変更されることがございますので、あらかじめご承知ください。