-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

Overview

Description

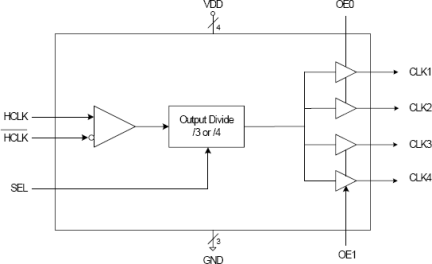

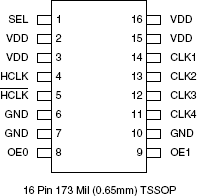

The 558-02 accepts a high-speed LVHSTL input and provides four CMOS low skew outputs from a selectable internal divider (divide by 3, divide by 4). The four outputs are split into two banks of two outputs. Each bank has a separate output enable to tri-state the output buffers. The 558-02 is a member of the ICS Clock BlocksTM family of clock generation, synchronization, and distribution devices.

Features

- 16-pin TSSOP package

- LVHSTL inputs

- Accepts up to 250 MHz input frequency

- Four low skew (<250 ps) outputs

- Selectable internal divider of 3 or 4

- Operating voltage of 3.3 V

Comparison

Applications

Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Application Note | PDF 91 KB | |

| Application Note | PDF 1.99 MB | |

| Overview | PDF 217 KB | |

| Application Note | PDF 322 KB | |

| Application Note | PDF 495 KB | |

| Application Note | PDF 442 KB | |

| Application Note | PDF 153 KB | |

| Application Note | PDF 565 KB | |

| Product Change Notice | PDF 361 KB | |

9 items

|

||