-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

5T9302

circleObsolete2.5V LVDS,1:2 Clock Buffer Terabuffer™

Overview

Description

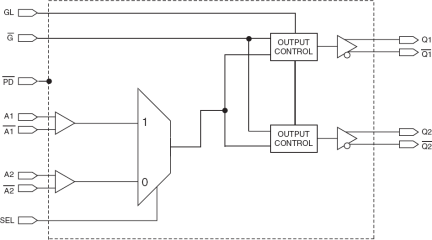

The 5T9302 2.5V differential clock buffer is a user-selectable differential input to two LVDS outputs. The fanout from a differential input to two LVDS outputs reduces loading on the preceding driver and provides an efficient clock distribution network. The 5T9302 can act as a translator from a differential HSTL, eHSTL, LVEPECL (2.5V), LVPECL (3.3V), CML, or LVDS input to LVDS outputs. A single-ended 3.3V / 2.5V LVTTL input can also be used to translate to LVDS outputs. The redundant input capability allows for an asynchronous change-over from a primary clock source to a secondary clock source. Selectable reference inputs are controlled by SEL. The 5T9302 outputs can be asynchronously enabled/disabled. When disabled, the outputs will drive to the value selected by the GL pin. Multiple power and grounds reduce noise.

Features

- Guaranteed low skew: 5ps (typical)

- Very low duty cycle distortion: 20ps (typical)

- High speed propagation delay: 1.35ns (typical)

- Up to 450MHz operation

- Selectable inputs

- Hot insertable and over-voltage tolerant inputs

- 3.3V/2.5V LVTTL, HSTL eHSTL, LVEPECL (2.5V), LVPECL (3.3V), CML or LVDS input interface

- Selectable differential inputs to two LVDS outputs

- Power-down mode

- 2.5V VDD

- 0°C to 70°C ambient operating temperature

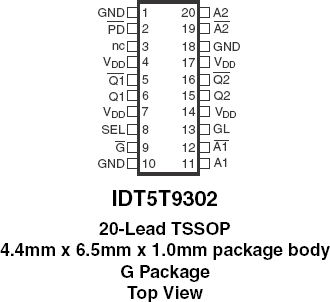

- Available in TSSOP package

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Buy / Sample |

|

|---|---|---|---|---|---|---|

| Part Number | ||||||

| TSSOP | 20 | I | Yes | Tube | ||

| TSSOP | 20 | I | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product