# [Notes] Smart Configurator for RH850

R20TS0806EC0100 Rev.1.00 Feb. 01, 2022

#### Outline

When using Smart Configurator for RH850, note the following points.

- 1. Notes on using T&H path self-diagnosis function of A/D Converter

- 2. Notes on redundant macros and wrong comments in A/D Converter header file

## 1. Notes on using T&H path self-diagnosis function of A/D Converter

## 1.1 Applicable Products

Smart Configurator for RH850 V1.2.0 or later version

## 1.2 Applicable Devices

RH850 family: RH850/U2A group

- > RH850/U2A16 (516-pin product, 292-pin product)

- RH850/U2A8 (292-pin product)

#### 1.3 Details

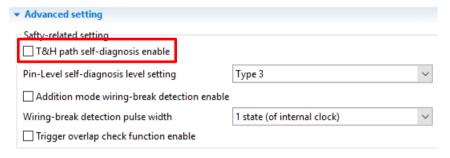

When using T&H path self-diagnosis function of A/D Converter (refer to Figure 1-1) on the following peripherals, the function can't be enabled/disabled correctly even if the T&H path self-diagnosis function is already selected/unselected on GUI. The actual generated code is the opposite of the GUI setting.

RH850/U2A16 (516-pin product, 292-pin product)

ADCJ0, ADCJ1, ADCJ2

> RH850/U2A8 (292-pin product)

ADCJ0, ADCJ1, ADCJ2

Figure 1-1 T&H path self-diagnosis setting

#### 1.4 Workaround

Manually modify the code in the following source file

- Source file: "r\_cg\_ad.h".

- Macro value: \_ADC\_TH\_PATH\_SELF\_DIAGNOSIS\_ENABLE,

\_ADC\_TH\_PATH\_SELF\_DIAGNOSIS\_DISABLE

Note: If code is generated again, the previous state will be restored. Modification is necessary each time after performing code generation.

This is an example of the required modification. Manually change the macro values in "r\_cg\_ad.h". In the following example, the code in red color is wrong code before modification, while the code in blue color is correct code after modification.

#### Before modification:

```

/*

Pin level self-diagnostic control register (ADCJnTDCR)

*/

/* T&H path self-diagnosis enable (THSDE) */

#define _ADC_TH_PATH_SELF_DIAGNOSIS_ENABLE (0x00UL) /* T&H path self-diagnosis is enable */

#define _ADC_TH_PATH_SELF_DIAGNOSIS_DISABLE (0x80UL) /* T&H path self-diagnosis is disabled */

......

```

#### After modification:

```

/*

Pin level self-diagnostic control register (ADCJnTDCR)

*/

/* T&H path self-diagnosis enable (THSDE) */

#define _ADC_TH_PATH_SELF_DIAGNOSIS_ENABLE (0x80UL) /* T&H path self-diagnosis is enable */

#define _ADC_TH_PATH_SELF_DIAGNOSIS_DISABLE (0x00UL) /* T&H path self-diagnosis is disabled */

.....

```

# 1.5 Schedule for Fixing the Problem

This problem will be fixed in next version. (Scheduled to be released in Jul 2022.)

## 2. Notes on redundant macros and wrong comments in A/D Converter header file

## 2.1 Applicable Products

Smart Configurator for RH850 V1.2.0 and later version

#### 2.2 Applicable Devices

RH850 family: RH850/U2A group

- > RH850/U2A16 (516-pin product, 292-pin product)

- > RH850/U2A8 (292-pin product)

#### 2.3 Details

When using A/D Converter on the following peripherals, there are mistakes in header file(r\_cg\_ad.h).

- Redundant macros: \_ADC\_VIRTUAL\_CHANNEL\_END\_INT\_DISABLE,

- \_ADC\_VIRTUAL\_CHANNEL\_END\_INT\_ENABLE

- Wrong comments: comments of \_ADC\_VIRTUAL\_END\_INT\_ENABLE,

- \_ADC\_VIRTUAL\_END\_INT\_ DISABLE

- RH850/U2A16 (516-pin product, 292-pin product)

ADCJ0, ADCJ1, ADCJ2

> RH850/U2A8 (292-pin product)

ADCJ0, ADCJ1, ADCJ2

```

Virtual channel control register (ADCJnVCRi)

#define _ADC_VIRTUAL_CHANNEL_END_INT_DISABLE

#define _ADC_VIRTUAL_CHANNEL_END_INT_ENABLE

(0x0000000UL)

not generated */

Redundant macros

/* generated *,

limit/lower limit table sel

#define ADC LIMIT TABLE SELECT NONE

#define ADC LIMIT TABLE SELECT 0

Upper limit and lower limit are not checked */

Upper limit and lower limit are checked for VCULLMTBRO

(0x10000000UL)

#define _ADC_LIMIT_TABLE_SELECT_I

(0x20000000UL)

/* Upper limit and lower limit are checked for

#define ADC LIMIT TABLE SELECT 2

#define ADC LIMIT TABLE SELECT 3

#define ADC LIMIT TABLE SELECT 4

#define ADC LIMIT TABLE SELECT 5

(0x30000000UL)

/* Upper limit and lower limit are checked for VCULLMTBR2

/\!\!\!* Upper limit and lower limit are checked for VCULLMTBR3

(0x400000000III.)

(0x50000000UL)

Upper limit and lower limit are checked for VCULLMTBR4

/* Upper limit and lower limit are checked for VCULLMTBR5

/* Upper limit and lower limit are checked for VCULLMTBR6

(0x60000000UL)

#define ADC LIMIT TABLE SELECT 6

#define ADC LIMIT_TABLE SELECT 7

/* Wait time table select (WTTS[3:0]) */

(0x70000000UL)

(0x80000000UL) /* Upper limit and lower limit are checked for VCULLMTBR7

#define _ADC_WAIT_TIME_SELECT_NONE

(0x0000000UL) /* Wait time are not checked

(0x01000000UL) /* Wait time are checked for WAITTRO */

#define ADC WAIT TIME TABLE 0

#define ADC WAIT TIME TABLE 1

(0x02000000UL) /* Wait time are checked for WAITTR1 */

#define _ADC_WAIT_TIME_TABLE_2

(0x03000000UL)

/* Wait time are checked for WAITTR2

#define ADC WAIT TIME TABLE 3

#define ADC WAIT TIME TABLE 4

#define ADC WAIT TIME TABLE 5

(0x04000000UL)

/* Wait time are checked for WAITTR3 */

(0x05000000UL) /* Wait time are checked for WAITTR4 */

(0x06000000UL) /* Wait time are checked for WAITTR5 */

#define _ADC_WAIT_TIME_TABLE_6

(0x07000000UL)

/* Wait time are checked for WAITTR6

(0x08000000UL) /* Wait time are checked for WAITTR7 */

ADC WAIT TIME TABLE

#define

/* GTM entry enable (GTMENT)

#define _ADC_GTM_ENTRY_ENABLE

(0x00100000UL) /* GTM entry enable */

(0x00000000UL) /* GTM entry disabled */

ADC GTM ENTRY DISABLE

#define

/* A/D conversion type (CNVCLS[3:0]) */

#define _ADC_NORMAL

(0x0000000UL) /* Normal A/D conversion */

#define _ADC_HOLD_VALUE

(0x00000800UL) /* Hold value A/D conversion */

#define ADC_EXTENDED_SAMPLING

#define ADC_AD_CORE_DIAGNOSIS

#define ADC_ADDITION_MODE

(0 \times 000001000 \text{UL}) /* Normal A/D conversion at extended sampling cycle */

(0x00001800UL) /* ADcore self-diagnosis A/D conversion */

(0x00002000UL) /* Addition mode A/D conversion */

#define _ADC_MPX_NORMAL

(0x00002800UL) /* MPX normal A/D conversion */

#define ADC_MPX_ADDITION_MODE

#define ADC_PIN_LEVEL_DIAGNOSIS

(0x00003000UL) /* MPX addition mode A/D conversion */

(0x00003800UL) /* Pin level self-diagnosis A/D conversion */

#define _ADC_BREAK_MODE1

(0x00004000UL) /* A/D conversion in wiring-break detection mode 1 */

#define

ADC_BREAK_MODE2_PULLDOWN

(0x00004800UL) /* A/D conversion in wiring-break detection mode 2 (physical

#define ADC_BREAK_MODE2_PULLUP

#define ADC_BREAK_MODE1_DIAGNOSIS

(0x00008000UL)

/*\ A/D conversion in wiring-break detection mode 2 (physical

(0x00008800UL) /* Self-diagnosis A/D conversion in wiring-break detection m

#define _ADC_BREAK_MODE2_PULLDOWN_DIAGNOSIS

(0x00009000

Wrong comments: these 2 comments are reversed.

#define ADC BREAK MODE2 PULLUP DIAGNOSIS #define ADC DATA PATH DIAGNOSIS

(0x00009800

(0x0000A0000___

* Virtual channel end interrupt enable (ADIE) */

#define _ADC_VIRTUAL_END_INT_ENABLE

#define _ADC_VIRTUAL_END_INT_DISABLE

(JU08000000x0)

/* INT_ADx is not output at the end of virtual channel */

/st INT ADx is output at the end of virtual channel st,

```

Figure 2-1 mistakes in header file

# 2.4 Workaround

The mistakes do not have effect on A/D Converter operation, please ignore and do not use the redundant macros. For wrong comments, please take care that the meanings are reversed.

# 2.5 Schedule for Fixing the Problem

This problem will be fixed in next version. (Scheduled to be released in Jul 2022.)

# **Revision History**

|      |           | Description |                      |

|------|-----------|-------------|----------------------|

| Rev. | Date      | Page        | Summary              |

| 1.00 | Feb.01.22 | -           | First edition issued |

Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

The past news contents have been based on information at the time of publication. Now changed or invalid information may be included.

The URLs in the Tool News also may be subject to change or become invalid without prior notice.

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

© 2022 Renesas Electronics Corporation. All rights reserved.

TS Colophon 4.3