# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                             | Document<br>No.         | TN-SH7-A0924A/E        | Rev.                                                                                       | 1.00 |     |

|-----------------------|----------------------------------------|-------------------------|------------------------|--------------------------------------------------------------------------------------------|------|-----|

| Title                 | Usage Notes for SH7786 Secondary Cache | Information<br>Category | Technical Notification |                                                                                            |      |     |

| Applicable<br>Product | SH7786 Group                           | Lot No.<br>All Lots     | Reference<br>Document  | SH7786 Group<br>User's Manual: Hardware Rev.1.00<br>November 30, 2010<br>(REJ09B0501-0100) |      | .00 |

## [Summary]

Addition of Usage Notes for "SH7786 Group User's Manual: Hardware Rev.1.00".

## [Priority level]

Importance: "Normal"

Urgency: "Normal"

#### [Web publication]

N/A (for specific users only)

"This is empty adjustment page to compare next Current (from) and Correction (to) on facing page. "

(By using two pages view of PDF readers this enables previously and prospectively view on odd and even pages.)

[Correction]

1. A.5.4 Usage Notes, Page 1979

Current (from):

None

Correction (to):

# A.5.4 Usage Notes

## (1) L2 Cache control

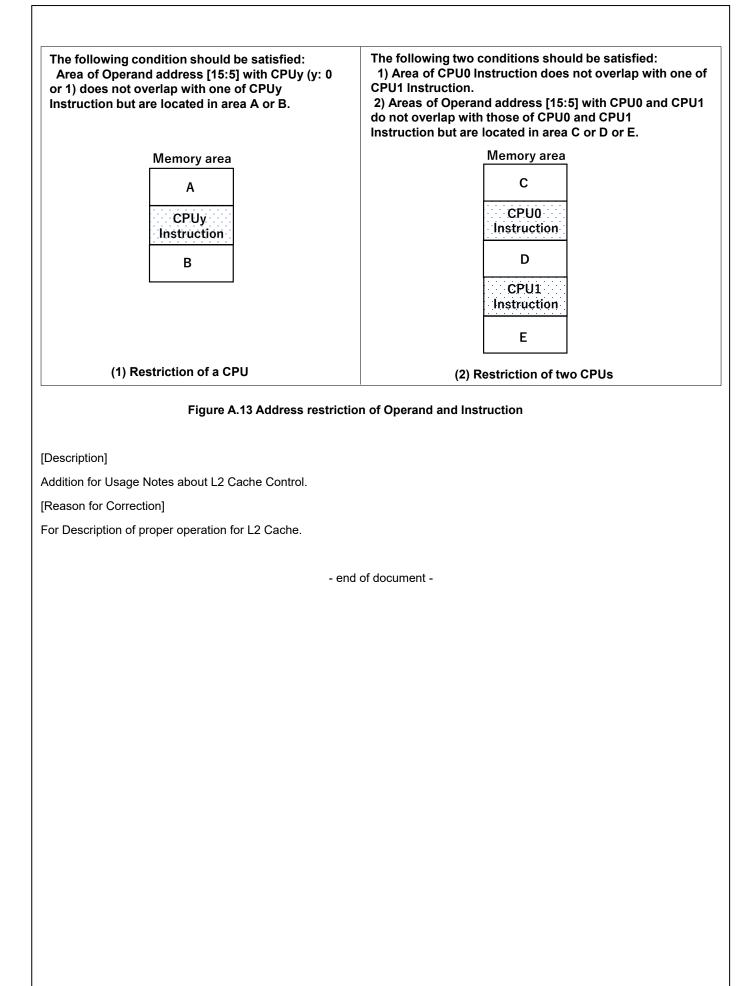

Table A.12 below shows operational conditions of register setting and address restrictions of Operand and Instruction about L2

Cache control. The combination in Table A.12 should be followed so that L2 Cache can operate properly.

| No | Used<br>number of<br>CPU | CPU0 |      | CPU1 |      | CPU0                                               | CPU1           |  |

|----|--------------------------|------|------|------|------|----------------------------------------------------|----------------|--|

|    |                          | L2OE | L2IE | L2OE | L2IE | Address restriction of<br>Operand and Instruction  |                |  |

| 1  | 2                        | 0    | 0    | 0    | 0    | x                                                  | x              |  |

| 2  |                          | 0    | 0    | 0    | 1    | x                                                  | x              |  |

| 3  |                          | 0    | 0    | 1    | 0    | x                                                  | Figure A.13(1) |  |

| 4  |                          | 0    | 0    | 1    | 1    | x                                                  | Figure A.13(1) |  |

| 5  |                          | 0    | 1    | 0    | 0    | x                                                  | x              |  |

| 6  |                          | 0    | 1    | 0    | 1    | Figure A.13(2)<br>Figure A.13(2)<br>Figure A.13(2) |                |  |

| 7  |                          | 0    | 1    | 1    | 0    |                                                    |                |  |

| 8  |                          | 0    | 1    | 1    | 1    |                                                    |                |  |

| 9  |                          | 1    | 0    | 0    | 0    | Figure A.13(1)                                     | х              |  |

| 10 |                          | 1    | 0    | 0    | 1    | Figure A.13(2)                                     |                |  |

| 11 |                          | 1    | 0    | 1    | 0    | x                                                  | x              |  |

| 12 |                          | 1    | 0    | 1    | 1    | Figure A.13(2)                                     |                |  |

| 13 |                          | 1    | 1    | 0    | 0    | Figure A.13(1)                                     | x              |  |

| 14 |                          | 1    | 1    | 0    | 1    | Figure A.13(2)<br>Figure A.13(2)<br>Figure A.13(2) |                |  |

| 15 |                          | 1    | 1    | 1    | 0    |                                                    |                |  |

| 16 |                          | 1    | 1    | 1    | 1    |                                                    |                |  |

| 17 | 1                        | 0    | 0    | -    | -    | x                                                  | -              |  |

| 18 |                          | 0    | 1    | -    | -    | x                                                  | -              |  |

| 19 |                          | 1    | 0    | -    | -    | x                                                  | -              |  |

| 20 |                          | 1    | 1    | -    | -    | Figure A.13(1)                                     | -              |  |

| 21 |                          | -    | -    | 0    | 0    | -                                                  | x              |  |

| 22 |                          | -    | -    | 0    | 1    | -                                                  | x              |  |

| 23 |                          | -    | -    | 1    | 0    | -                                                  | x              |  |

| 24 |                          | -    | -    | 1    | 1    | -                                                  | Figure A.13(1) |  |

Table A.12 Operational conditions of L2 Cache control

x: Don't care

-: Excluded

"This is empty adjustment page to compare next Current (from) and Correction (to) on facing page. "

(By using two pages view of PDF readers this enables previously and prospectively view on odd and even pages.)