Date: Mar. 25, 2016

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                  | Document<br>No.         | TN-SH7-A903A/E         | Rev.                                                       | 1.00 |  |

|-----------------------|----------------------------------------------------------|-------------------------|------------------------|------------------------------------------------------------|------|--|

| Title                 | Usage Notes on SCSPTR of Serial Commun<br>Interface(SCI) | Information<br>Category | Technical Notification |                                                            |      |  |

|                       |                                                          | Lot No.                 |                        |                                                            |      |  |

| Applicable<br>Product | SH7147 Group                                             | All lots                | Reference<br>Document  | SH7147 Group Hardware Manual<br>Rev.3.00 (REJ09B0230-0300) |      |  |

Thank you for your consistent patronage of Renesas semiconductor products.

We would like to inform you of the correction of errors regarding SCSPTR Register of Serial Communication Interface (SCI) in the SH7147 Group Hardware Manuals as follows.

SPB1IO SPB1DT

SPB0IO

SPB0DT

#### • 13.3.8 Serial Port Register (SCSPTR)

Bit:

[Before correction]

| ln     | itial Value:<br>R/W: | 0<br>R/W         | 0 - | 0 -                                                                                                                                                                                                                                                                 | 0 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0<br>R/W                                                                                              | -<br>R/W                                                    | 0<br>R/W                                     | R/W                     |

|--------|----------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|-------------------------|

| Bit    | Bit Name             | Initial<br>value | R/W | Descri                                                                                                                                                                                                                                                              | ption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |                                                             |                                              |                         |

| 7      | EIO                  | 0                | R/W | Error I                                                                                                                                                                                                                                                             | nterrupt Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nly                                                                                                   |                                                             |                                              |                         |

|        |                      |                  |     | set to<br>the CF<br>0: The<br>Whi                                                                                                                                                                                                                                   | 1, the SCI of the science of the sci | es RXI interr<br>does not requ<br>he RIE bit is<br>ables or disa<br>bit is 1, RXI a<br>bit is 1, only | uest an RXI i<br>set to 1.<br>bles RXI and<br>and ERI inter | nterrupt to<br>d ERI interru<br>rupts are se | ots.<br>nt to the INTC. |

| 6 to 4 | -                    | All 0            | -   | Reserved  These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |                                                             |                                              |                         |

| 3      | SPB1IO               | 0                | R/W |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output in Ser                                                                                         |                                                             |                                              | •                       |

|        |                      |                  |     | output<br>port ou<br>bit in S<br>0: Doe                                                                                                                                                                                                                             | the data sput put put pin, se CSMR and so not output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pecified in the                                                                                       | e SPB1DT b<br>and CKE0 bit<br>oT bit value t                | it through the<br>s in SCSCR<br>hrough the S | SCK pin.                |

| 2      | SPB1DT               | Undefined        | R/W | Clock                                                                                                                                                                                                                                                               | Port Data i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | n Serial Port                                                                                         |                                                             |                                              |                         |

|        |                      |                  |     | Specifies the data output through the SCK pin in the serial port. Output should be enabled by the SPB1IO bit (for details, refer to the SPB1IO be description). When output is enabled, the SPB1DT bit value is output through the SCK pin.  0: Low level is output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |                                                             |                                              |                         |

1: High level is output

| 1 | SPB0IO | 0         | R/W | Serial Port Brea          | k Input/Output |               |                                                               |

|---|--------|-----------|-----|---------------------------|----------------|---------------|---------------------------------------------------------------|

|   |        |           |     | Together with th TXD pin. | e SPB0DT bit   | and the TE I  | oit in SCSCR, controls the                                    |

| 0 | SPB0DT | Undefined | R/W | Serial Port Brea          | k Data         |               |                                                               |

|   |        |           |     |                           | e TXD pin fund |               | SCSCR, controls the TXD o have been selected with             |

|   |        |           |     | TE bit setting in         | SPB0IO<br>bit  | SPB0DT<br>bit |                                                               |

|   |        |           |     | SCSCR                     | setting        | setting       | State of TXD pin                                              |

|   |        |           |     | 0                         | 0              | *             | SPB0DT output<br>disabled<br>(initial state)                  |

|   |        |           |     | 0                         | 1              | 0             | Output, low level                                             |

|   |        |           |     | 0                         | 1              | 1             | Output, high level                                            |

|   |        |           |     | 1                         | *              | *             | Output for transmit data in accord with the serial core logic |

Date: Mar. 25, 2016

| er correct | ion]        |                                             |     |                                                                                                                                                                                                                                |                                                                 |                                                                    |                          |                                      |                                                             |  |

|------------|-------------|---------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|--------------------------------------|-------------------------------------------------------------|--|

|            | Bit:        | 7                                           | 6   | 5                                                                                                                                                                                                                              | 4                                                               | 3                                                                  | 2                        | 1                                    | 0                                                           |  |

|            |             | EIO                                         | -   | -                                                                                                                                                                                                                              | -                                                               | SPB1IO                                                             | SPB1DT                   | -                                    | SPB0DT                                                      |  |

| lni        | tial Value: | 0                                           | 0   | 0                                                                                                                                                                                                                              | 0                                                               | 0                                                                  | -                        | 0                                    | 1                                                           |  |

|            | RW:         | R/W                                         | -   | -                                                                                                                                                                                                                              | -                                                               | R/W                                                                | W                        | -                                    | W                                                           |  |

| Bit        | Bit Name    | Initial<br>value                            | R/W | Descrip                                                                                                                                                                                                                        | otion                                                           |                                                                    |                          |                                      |                                                             |  |

| 7          | EIO         | 0                                           | R/W | Error Ir                                                                                                                                                                                                                       | nterrupt O                                                      | nly                                                                |                          |                                      |                                                             |  |

|            |             |                                             |     | set to 1<br>the CP<br>0: The<br>While                                                                                                                                                                                          | I, the SCI<br>U even if<br>RIE bit er<br>e the RIE<br>e the RIE | does not req<br>the RIE bit is<br>ables or disa<br>bit is 1, RXI a | bles RXI and             | terrupt to<br>ERI interroupts are se | upts.<br>ent to the INTC.                                   |  |

| 6 to 4     | -           | All 0                                       | _   | Reserv                                                                                                                                                                                                                         | red                                                             |                                                                    |                          |                                      |                                                             |  |

|            |             |                                             |     | These                                                                                                                                                                                                                          | bits are al                                                     | ways read as                                                       | 0. The write             | value shou                           | ıld always be 0.                                            |  |

| 3          | SPB1IO      | 0 R/W Clock Port Input/Output in Serial Por |     |                                                                                                                                                                                                                                |                                                                 |                                                                    |                          |                                      |                                                             |  |

|            |             |                                             |     | output<br>port ou<br>bit in S<br>0: Does                                                                                                                                                                                       | the data s<br>tput pin, s<br>CSMR an<br>s not outp              | pecified in the the C/A d the CKE1 aut the SPB11                   |                          | through the in SCSCF rough the       | SCK pin.                                                    |  |

| 2          | SPB1DT      | Undefined                                   | W   | Clock F                                                                                                                                                                                                                        | Port Data                                                       | in Serial Port                                                     |                          |                                      |                                                             |  |

|            |             |                                             |     | should<br>descrip<br>through<br>0: Lov                                                                                                                                                                                         | be enable                                                       | ed by the SPI<br>en output is e<br>pin.<br>output                  | B1IO bit (for de         | etails, refe                         | serial port. Output<br>r to the SPB1IO b<br>value is output |  |

| 1          | -           | 0                                           | -   | Reserv                                                                                                                                                                                                                         | red                                                             |                                                                    |                          |                                      |                                                             |  |

| 0          | SPB0DT      | 1                                           | W   | Serial F                                                                                                                                                                                                                       | Port Break                                                      | · Data                                                             |                          |                                      |                                                             |  |

|            |             |                                             |     | Together with the TE bit in SCSCR, controls the TXD pin. Note that th TXD pin function needs to have been selected with the pin function controller (PFC). This bit is a write-only bit and always read as an undefined value. |                                                                 |                                                                    |                          |                                      |                                                             |  |

|            |             |                                             |     | TE                                                                                                                                                                                                                             | bit                                                             | SPB0DT                                                             |                          |                                      |                                                             |  |

|            |             |                                             |     |                                                                                                                                                                                                                                | ting in                                                         | bit                                                                | 04-1-15                  | S i                                  |                                                             |  |

|            |             |                                             |     | SC:                                                                                                                                                                                                                            | SCR                                                             | setting<br>0                                                       | State of TXI Output, low |                                      |                                                             |  |

|            |             |                                             |     | 0                                                                                                                                                                                                                              |                                                                 | 1                                                                  | Output, low              |                                      | ial value)                                                  |  |

|            |             |                                             |     | 1                                                                                                                                                                                                                              |                                                                 | *                                                                  | Output for tr            |                                      |                                                             |  |

|            |             |                                             |     |                                                                                                                                                                                                                                |                                                                 |                                                                    |                          |                                      |                                                             |  |

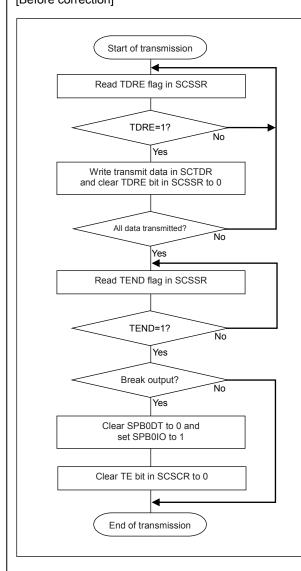

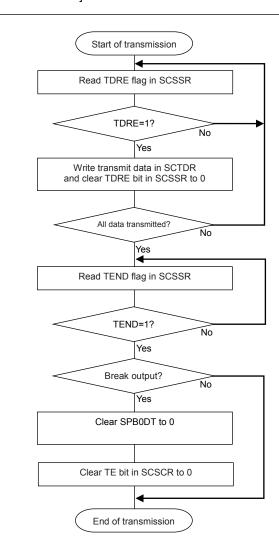

Figure 13.4 Sample Flowchart for Transmitting Serial Data [Before correction]

- [1] SCI status check and transmit data write:

- Read SCSSR and check that the TDRE flag is set to 1, then write transmit data to SCTDR, and clear the TDRE flag to 0.

- [2] Serial transmission continuation procedure:

To continue serial transmission, read 1 from the TDRE flag to confirm that writing is possible, then write data to SCTDR, and then clear the TDRE flag to 0.

Checking and clearing of the TDRE flag is automatic when the DTC is activated by a transmit data empty interrupt (TXI) request, and data is written to SCTDR.

[3] Break output at the end of serial transmission:

To output a break in serial transmission, clear the SPB0DT bit to 0 and set the SPB0IO bit to 1 in SCSPTR, then clear the TE bit in SCSCR to 0.

#### [After correction]

- [1] SCI status check and transmit data write:

- Read SCSSR and check that the TDRE flag is set to 1, then write transmit data to SCTDR, and clear the TDRE flag to 0.

- [2] Serial transmission continuation procedure:

To continue serial transmission, read 1 from the TDRE flag to confirm that writing is possible, then write data to SCTDR, and then clear the TDRE flag to 0.

Checking and clearing of the TDRE flag is automatic when the DTC is activated by a transmit data empty interrupt (TXI) request, and data is written to SCTDR.

[3] Break output at the end of serial transmission:

To output a break in serial transmission, clear the SPB0DT bit to 0, then clear the TE bit in SCSCR to 0.

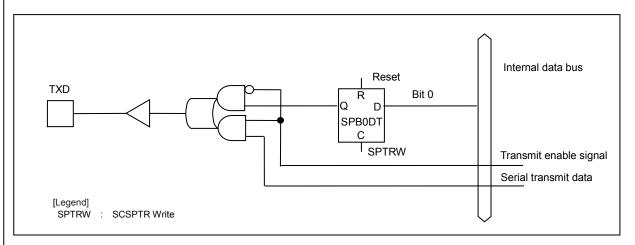

Figure 13.20 SPBIO Bit, SPBDT Bit, and TXD Pin [Before correction]

## Reset Bit 1 R D SPBIO Internal data bus SPTRW Reset TXD Bit 0 **SPBDT** SPTRW Transmit enable signal Serial transmit data [Legend] SPTRW : SCSPTR Write

Figure 13.20 SPBIO Bit, SPBDT Bit and TXD Pin

### [After correction]

Figure 13.20 SPB0DT Bit and TXD Pin

Date: Mar. 25, 2016

13.7.4 Sending a Break Signal

[Before correction]

The I/O condition and level of the TXD pin are determined by the SPB0IO and SPB0DT bits in the serial port register (SCSPTR).

This feature can be used to send a break signal.

Until TE bit is set to 1 (enabling transmission) after initializing, TXD pin does not work.

During the period, mark status is performed by SPB0DT bit. Therefore, the SPB0IO and SPB0DT bits should be set to 1 (high level output).

To send a break signal during serial transmission, clear the SPB0DT bit to 0 (low level), then clear the TE bit to 0 (halting transmission).

When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, and 0 is output from the TXD pin.

[After correction]

The output level of the TXD pin are determined by the SPB0DT bit in the serial port register (SCSPTR).

This feature can be used to send a break signal.

Until TE bit is set to 1 (enabling transmission) after initializing, TXD pin does not work.

During the period, mark status is performed by SPB0DT bit. Therefore, the SPB0DT bit should be set to 1 (high level).

To send a break signal during serial transmission, clear the SPB0DT bit to 0 (low level), then clear the TE bit to 0 (halting transmission).

When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, and the level specified by the SPB0DT bit is output from the TXD pin.

-End of document.-