# **Microcomputer Technical Information**

CP(K), O

|                                                | Document No.   | SBG-DT-03-0194-E 1/2        |

|------------------------------------------------|----------------|-----------------------------|

|                                                | Date issued    | July 18, 2003               |

| μPD789467 Subseries                            | Issued by      | Microcomputer Group         |

|                                                |                | 2nd Solutions Division      |

| Usage Restrictions                             |                | Solutions Operations Unit   |

|                                                |                | NEC Electronics Corporation |

| Related documents                              | Notification   | √ Usage restriction         |

| μPD789467 Subseries Preliminary User's Manual: | classification | Upgrade                     |

| U15552EJ1V0UD00                                |                | √ Document modification     |

|                                                |                | Other notification          |

# 1. Affected products

$\mu$ PD789462, 789464, 789466, 789467  $\mu$ PD78F9468

### 2. Details of modification and added restriction

### (1) Error on starting 8-bit timer

The description in **6.5** Notes on Using 8-Bit Timers 30 and 40 (1) Error on starting timer in the user's manual (U15552EJ1V0UD00) has been corrected as follows.

### (Incorrect)

An error of up to 1 clock is included in the time between the timer being started and a match signal is being generated.

## (Correct)

An error of up to 1.5 clocks is included in the time between the timer being started and a match signal is being generated.

See attachment 2 for details.

### 3. Correction

Regard the restriction added in this document as a usage restriction. Modification will be reflected in the next revision of the user's manual.

### 4. List of restrictions

The restriction history and detailed information is described in attachment 1.

| SBG-DT-03-0194-E | 2/2 |

|------------------|-----|

|------------------|-----|

# 5. Document revision history

# $\mu$ PD789467 Subseries Usage Restrictions

| Document Number  | Date Issued   | Description    |

|------------------|---------------|----------------|

| SBG-DT-03-0194-E | July 18, 2003 | Newly created. |

# List of Usage Restrictions in $\mu$ PD789467 Subseries

# 1. Product History

### <Mask ROM version>

|   | Description |                              | 1    | μPD789462, 789464, 789466, 789467 |

|---|-------------|------------------------------|------|-----------------------------------|

|   |             |                              | Rank | All Ranks                         |

| ĺ | 1           | 1 Restriction on 8-bit timer |      | Δ                                 |

### <Flash memory version>

| Description |                              |      | μPD78F9468 |

|-------------|------------------------------|------|------------|

|             |                              | Rank | All Ranks  |

| 1           | 1 Restriction on 8-bit timer |      | Δ          |

- **Notes 1.** The rank is indicated by the fifth character from the left in the lot number marked on the package.

- 2. The meaning of each symbol is as follows.

- -: Restriction does not apply

- √: Restriction already corrected

- ×: Restriction applies (correction is planned)

- Δ: Restriction applies (correction is not planned)

## 2. Details of Usage Restrictions

No.1: A restriction added this time. Refer to attachment 2 for details.

#### No.1 Restriction on 8-bit timer

### (1) Error upon timer start

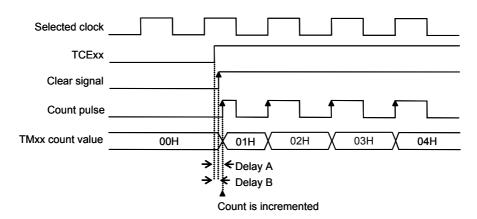

When the 8-bit timer/event counter is used, an error of up to 1.5 clocks is generated after the timer has been started until a match signal is generated. This is because a rising edge is detected when the timer is started while the selected clock is high, which results in the count value getting incremented.

#### [Details of restriction]

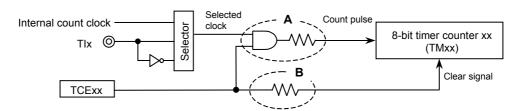

The basic timer configuration applicable to this restriction is shown in the figure below.

- The selected clock and the count operation flag (TCExx) are ANDed, and the result is supplied to the counter

- The TMxx counter value is cleared when the count operation flag (TCExx) is set

### **Basic Timer Configuration**

If a count pulse is delayed for the clear signal ("delay A > delay B") as the result of setting the count operation flag (TCExx) while the selected clock is high, the TMxx count value is incremented. An error of up to 1.5 clocks is generated.

Case when an error of up to 1.5 clocks is generated

**Remark** See Basic Timer Configuration above for details of the selected clock, TCE, clear signal, and count pulse.