# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

|                            |                            |             |                 |                            |                         | -                                              | -                                                              | •           | •    |

|----------------------------|----------------------------|-------------|-----------------|----------------------------|-------------------------|------------------------------------------------|----------------------------------------------------------------|-------------|------|

| Product<br>Category        | MPU/MCU                    | MPU/MCU     |                 |                            |                         |                                                | TN-SH7-A792A/E                                                 | Rev.        | 1.00 |

| Title                      | SH7730 Hardware            | revision up |                 |                            | Information<br>Category |                                                |                                                                |             |      |

|                            |                            |             |                 | Lot                        | No.                     |                                                |                                                                |             |      |

| Applicable<br>Product      |                            |             |                 |                            |                         | Reference<br>Document                          | SH7730 Group Hardw<br>(REJ09B0359)                             | are Manu    | ial  |

| SH7730 Hard                | ware Manual is rev         | ised from   | Rev.2.00. to F  | Rev.3.00                   |                         |                                                |                                                                |             |      |

| Please refer t             | to main revisions ar       | nd additior | ns in Rev. 3.00 | ) as show                  | n in tł                 | ne following.                                  |                                                                |             |      |

| ltom                       |                            | Daga        | Davisian (S     | aa Manu                    |                         |                                                |                                                                |             |      |

| Item                       | res of This LSI            | Page<br>4   | Revision (S     |                            | artor                   | Details)                                       |                                                                |             |      |

|                            | Features of This           | 4           |                 |                            | _                       |                                                |                                                                |             |      |

| LSI                        |                            |             | Iter<br>Bus     | n<br>s state               | Featu<br>• SD           |                                                |                                                                |             |      |

|                            |                            |             | cor             | troller (BSC)              |                         | •                                              | nory devices or up to one 1-Gbit me                            | mory device |      |

|                            |                            |             |                 |                            |                         | can be connected<br>Data bus width: 16 bits of | or 32 bits                                                     |             |      |

|                            |                            |             |                 |                            |                         |                                                | r self-refresh functions<br>r bank active mode can be selected |             |      |

|                            |                            |             |                 |                            |                         | Auto-precharge mode of                         | bank active mode can be selected                               |             |      |

|                            |                            | 6           | Table amen      | ded                        |                         |                                                |                                                                |             |      |

|                            |                            |             | Iter            | n<br>ck pulse              | Featu                   |                                                | estable from enternal input (EVTAL)                            | and entetal |      |

|                            |                            |             |                 | ick puise<br>nerator (CPG) |                         | ock mode: Input clock sel<br>sonator           | ectable from external input (EXTAL)                            | and crystal |      |

|                            |                            |             |                 |                            |                         | tput clock: Bus clock (B¢                      |                                                                |             |      |

|                            |                            |             |                 |                            |                         | enerates four types of sys<br>CPU clock (I     |                                                                |             |      |

|                            |                            |             |                 |                            |                         | SH (SuperHyway) clock<br>Bus clock (B          | (Sφ): Maximum 133.4 MHz                                        |             |      |

|                            |                            |             |                 |                            |                         | Peripheral clock (Pø): Maximu                  |                                                                |             |      |

|                            |                            |             |                 |                            |                         | pports power-down mod<br>Sleep mode            | e                                                              |             |      |

|                            |                            |             |                 |                            |                         | Software standby mode                          |                                                                |             |      |

|                            |                            |             |                 |                            |                         | Module standby mode                            |                                                                |             |      |

| 7.8.2 Note<br>Unbuffered V | es on the<br>Vrite Setting | 204         | Newly adde      | d                          |                         |                                                |                                                                |             |      |

| 8.1 Featu                  | res                        | 209,        | Figure title a  | mended                     |                         |                                                |                                                                |             |      |

| Figure 8.1<br>Operand Ca   | Configuration of           | 210         | -               |                            |                         |                                                |                                                                |             |      |

| Figure 8.2                 | Configuration of           |             |                 |                            |                         |                                                |                                                                |             |      |

| Instruction C              |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

|                            |                            |             |                 |                            |                         |                                                |                                                                |             |      |

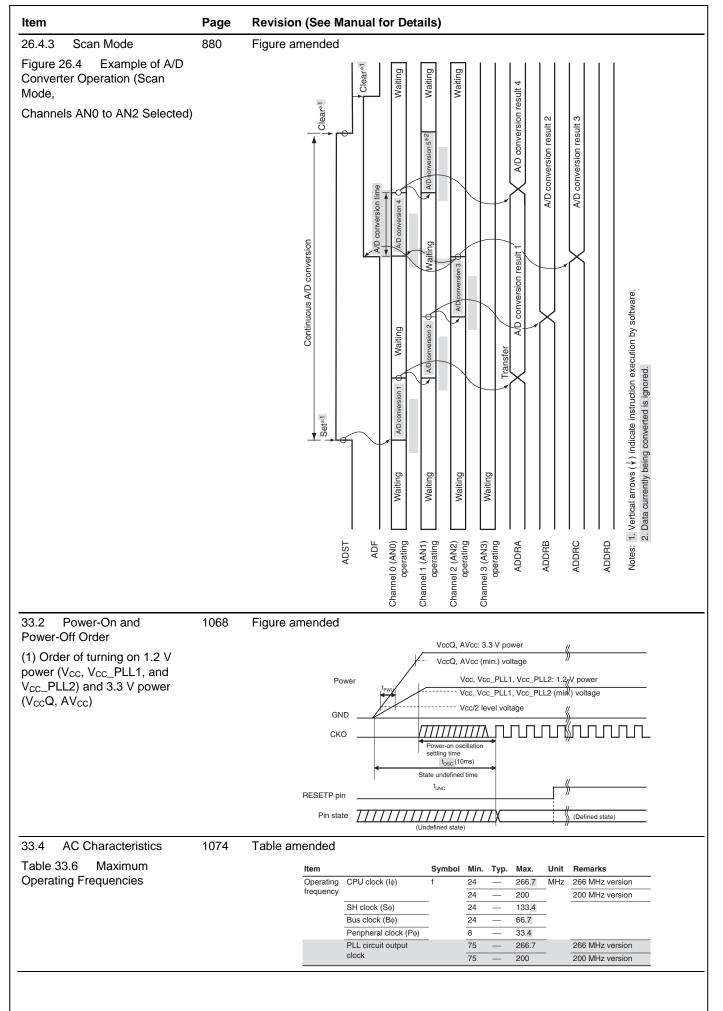

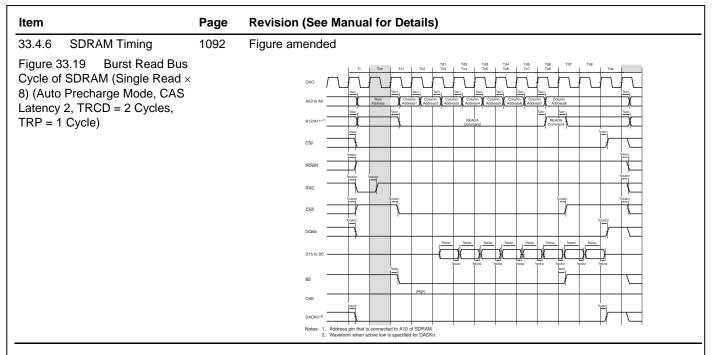

| Item                                         | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.3.1 Read Operation                         | 219  | Description amended                                                                                                                                                                                                                                                                                                                    |

|                                              |      | 4. Cache miss (no write-back)                                                                                                                                                                                                                                                                                                          |

|                                              |      | Data is read into the cache line on the way, which is selected to replace, from the physical address space corresponding to the virtual address. When reading data, the read data is returned to the CPU at the point in time when that data arrives in the cache.                                                                     |

|                                              |      |                                                                                                                                                                                                                                                                                                                                        |

|                                              |      | <ol> <li>Cache miss (with write-back)</li> <li>The tag and data field of the cache line on the way which is selected to replace are</li> </ol>                                                                                                                                                                                         |

|                                              |      | saved in the write-back buffer. Then data is read into the cache line on the way which is selected to replace are which is selected to replace from the physical address space corresponding to the virtual address. When reading data, the read data is returned to the CPU at the point in time when that data arrives in the cache. |

| 8.6.1 IC Address Array                       | 230  | Figure title amended                                                                                                                                                                                                                                                                                                                   |

| Figure 8.5 Memory-Mapped<br>IC Address Array |      |                                                                                                                                                                                                                                                                                                                                        |

| 8.6.2 IC Data Array                          | 231  | Figure title amended                                                                                                                                                                                                                                                                                                                   |

| Figure 8.6 Memory-Mapped<br>IC Data Array    |      |                                                                                                                                                                                                                                                                                                                                        |

| 8.6.3 OC Address Array                       | 233  | Figure title amended                                                                                                                                                                                                                                                                                                                   |

| Figure 8.7 Memory-Mapped<br>OC Address Array |      |                                                                                                                                                                                                                                                                                                                                        |

| 8.6.4 OC Data Array                          | 234  | Figure title amended                                                                                                                                                                                                                                                                                                                   |

| Figure 8.8 Memory-Mapped<br>OC Data Array    |      |                                                                                                                                                                                                                                                                                                                                        |

| 10.1 Features                                | 246  | Figure amended                                                                                                                                                                                                                                                                                                                         |

| Figure 10.1 Block Diagram of INTC            |      | ICR0     INTPRIOD       ICR1     INTREQ00       INTREQ00       INTRSK00       INTRSK00       INTRSK00       INTRSKCLR00       INTMSKCLR00       INTMSKCLR00                                                                                                                                                                            |

| 10.3.1 Interrupt Control                     | 251  | Description amended                                                                                                                                                                                                                                                                                                                    |

| Register 0 (ICR0)                            |      | ICR0 sets the input signal detection mode for the external interrupt input pin NMI, IRQ, IRL, and PINT, and indicates the input signal level at the NMI pin.                                                                                                                                                                           |

|                                              |      |                                                                                                                                                                                                                                                                                                                                        |

| 10.3.5 Interrupt Request | <b>Page</b> 257 | Revision (See Manual for Details)         Table amended |                         |           |            |                                                                                                                                                |  |  |

|--------------------------|-----------------|---------------------------------------------------------|-------------------------|-----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register 00 (INTREQ00)   |                 |                                                         |                         | Initial   |            |                                                                                                                                                |  |  |

|                          |                 | Bit                                                     | Bit Name                | Value     | R/W        | Description                                                                                                                                    |  |  |

|                          |                 | 7                                                       | IRQ0                    | 0         | R/W        | Edge detection (IRQnS in ICR1 set to B'00 or B'01)                                                                                             |  |  |

|                          |                 | 6<br>5                                                  | IRQ1                    | 0         | R/W        | Flag indicating detection of IRQn interrupt     When reading                                                                                   |  |  |

|                          |                 | 5                                                       | IRQ2<br>IRQ3            | 0         | R/W<br>R/W | 0: No interrupt request detected                                                                                                               |  |  |

|                          |                 | 3                                                       | IRQ4                    | 0         | R/W        | 1: Interrupt request detected                                                                                                                  |  |  |

|                          |                 | 2                                                       | IRQ5                    | 0         | R/W        | When writing                                                                                                                                   |  |  |

|                          |                 | 1                                                       | IRQ6                    | 0         | R/W        | 0: The bit is cleared to 0 only if it was previously<br>read as 1.                                                                             |  |  |

|                          |                 | 0                                                       | IRQ7                    | 0         | R/W        | 1: Writing 1 is ignored. Write 1 to the bits other than<br>the bit to be cleared.                                                              |  |  |

|                          |                 |                                                         |                         |           |            | Note: Write 1 to all bits you do not wish to clear to 0.                                                                                       |  |  |

|                          |                 |                                                         |                         |           |            | Level detection (IRQnS in ICR1 set to B'10 or B'11)<br>[LSH in ICR0 set to 1]                                                                  |  |  |

|                          |                 |                                                         |                         |           |            | Indicates whether or not a valid interrupt request is<br>being input to the IRQn pin.                                                          |  |  |

|                          |                 |                                                         |                         |           |            | When writing                                                                                                                                   |  |  |

|                          |                 |                                                         |                         |           |            | 0: No interrupt request being input                                                                                                            |  |  |

|                          |                 |                                                         |                         |           |            | <ol> <li>Interrupt request being input</li> <li>Writing to these bits is ignored.</li> </ol>                                                   |  |  |

|                          |                 |                                                         |                         |           |            | [LSH in ICR0 cleared to 0]                                                                                                                     |  |  |

|                          |                 |                                                         |                         |           |            | Flag indicating detection of IRQn interrupt                                                                                                    |  |  |

|                          |                 |                                                         |                         |           |            | When reading                                                                                                                                   |  |  |

|                          |                 |                                                         |                         |           |            | 0: No interrupt request detected                                                                                                               |  |  |

|                          |                 |                                                         |                         |           |            | 1: Interrupt request detected     Writing to these bits is ignored.                                                                            |  |  |

| 10.3.5 Interrupt Request | 258             | Description a                                           | dded                    |           |            |                                                                                                                                                |  |  |

| Register 00 (INTREQ00)   |                 | The methods                                             | of clearing             | g the bi  | ts in tł   | nis register are as follows.                                                                                                                   |  |  |

|                          |                 | 1. Edge det                                             | ection                  |           |            |                                                                                                                                                |  |  |

|                          |                 |                                                         | -                       |           |            | red by writing 0 to the corresponding bit after<br>1 to the bits you do not wish to clear to 0.                                                |  |  |

|                          |                 | 2. Level det                                            | ection (LSI             | H in ICF  | R0 set     | to 1)                                                                                                                                          |  |  |

|                          |                 |                                                         | and the int             |           |            | to 0 automatically when the IRQ pin state<br>at is negated. It is not necessary to clear the bit                                               |  |  |

|                          |                 | 3. Level det                                            | ection (LSI             | H in ICF  | R0 cle     | ared to 0)                                                                                                                                     |  |  |

|                          |                 |                                                         |                         |           |            | and the interrupt request is negated, write 1 to ISK00 register.                                                                               |  |  |

| 10.4.1 NMI Interrupt     | 266             | Description a                                           | mended                  |           |            |                                                                                                                                                |  |  |

|                          |                 | or falling edg                                          | e detectior             | n. After  | the N      | e NMIE bit in ICR0 is used to select either risin<br>MIE bit in ICR0 is modified, NMI interrupts are<br>us clock cycles.                       |  |  |

|                          |                 | SR) is set to                                           | 15 automa<br>upt has no | tically v | when a     | set to 1, the SR interrupt mask level (IMASK in<br>an NMI interrupt is accepted. The reception of<br>ASK in SR when the INTMU bit in CPUOPM ha |  |  |

| 10.4.2 IRQ Interrupts                          | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                | 267  | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                |      | IRQ interrupts are input on pins IRQ7 to IRQ0. Edge-sensing or level-sensing can be selected by setting the IRQnS bits ( $n = 0$ to 7) in ICR1. When level-sensing is selected, operation differs according to the setting of the LSH bit in ICR0. The initial value of LSH in ICR0 is 0, but it is recommended that it be set to 1 before using the INTC.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                                |      | 1. LSH in ICR0 set to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                                |      | Interrupt requests are not held internally by the INTC. Maintain the state of IRQ pin until the interrupt is accepted by the CPU and interrupt handling sta                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                |      | 2. LSH in ICR0 cleared to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                |      | When the INTC detects an interrupt request from the state of the IRQ pin, it holds the interrupt request in the INTREQ00 register. The value is held in INTREQ00 even if the interrupt request is negated at the IRQ pin before the interrupt is accepted by the CPU. After the request is negated at the IRQ pin, the value of INTREQ00 is cleared either when the CPU accepts an interrupt (which need not be an IRQ interrupt) or when the corresponding bit in the INTMSK00 register is set to 1. Clear the INTREQ00 flag before enabling interrupts by clearing the BL bit or executing the RTE instruction. |  |  |  |  |  |  |  |

| 11.1 Features                                  | 282  | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                |      | 6. PCMCIA interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                |      | <ul> <li>Supports IC memory cards and I/O card interfaces defined in the JEIDA<br/>specifications Ver. 4.2 (PCMCIA2.1).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Figure 11.1 Block Diagram of 283               | 283  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                |      | BACK<br>BREQ<br>WAIT<br>WAIT<br>WAIT<br>Bus<br>mastership<br>controller<br>Wait<br>controller<br>Wait<br>controller<br>RBWTCNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 11.1 Features                                  |      | Legend added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Figure 11.1 Block Diagram of<br>BSC            |      | [Legend]<br>RBWTCNT: Reset bus wait counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 11.4 Register Descriptions                     | 292  | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                                                |      | Name         Abbreviation         R/W         Address         Access Size           SDRAM mode register         SDMR3         W         H'FEC1 5xxx         —                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Table 11.7 Register<br>Configuration           |      | Reset bus wait counter RBWTCNT — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Configuration<br>Table 11.8 Register States in | 293  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Configuration                                  | 293  | Reset bus wait counter RBWTCNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Item                                               | Page | Revision (See       | Manual     | for De           | tails)             |                                                                                                                                                                                                          |

|----------------------------------------------------|------|---------------------|------------|------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.2 CSn Space Bus<br>Control Register (CSnBCR)  | 298  | Table amende        | d          | Initial          |                    |                                                                                                                                                                                                          |

|                                                    |      | Bit                 | Bit Name   | Value            | R/W                | Description                                                                                                                                                                                              |

|                                                    |      | 30 to 28            | 3 IWW[2:0] | 011              | R/W                | Idle Cycles between Write-Read Cycles and Write-Write<br>Cycles                                                                                                                                          |

|                                                    |      |                     |            |                  |                    | These bits specify the number of idle cycles to be<br>inserted after the access to a memory that is connected                                                                                            |

|                                                    |      |                     |            |                  |                    | to the space. The target access cycles are the write-<br>read cycle and write-write cycle.                                                                                                               |

|                                                    |      |                     |            |                  |                    | 000: Setting prohibited                                                                                                                                                                                  |

|                                                    |      |                     |            |                  |                    | 001: 1 idle cycle inserted<br>010: 2 idle cycles inserted                                                                                                                                                |

|                                                    |      |                     |            |                  |                    | 011: 4 idle cycles inserted                                                                                                                                                                              |

|                                                    |      |                     |            |                  |                    | 100: 6 idle cycles inserted<br>101: 8 idle cycles inserted                                                                                                                                               |

|                                                    |      |                     |            |                  |                    | 110: 10 idle cycles inserted<br>111: 12 idle cycles inserted                                                                                                                                             |

| 11.4.3 CSn Space Wait<br>Control Register (CSnWCR) | 306  | Table amende        | d          |                  |                    |                                                                                                                                                                                                          |

|                                                    |      | Bit                 | Bit Name   | Initial<br>Value | R/W                | Description                                                                                                                                                                                              |

| (1) Normal Space and<br>Byte-Selection SRAM        |      | 23, 22              | BW[1:0]    | 00               | R/W                | Number of Burst Wait Cycles                                                                                                                                                                              |

| -                                                  |      |                     |            |                  |                    | Specify the number of wait cycles to be inserted to the second and subsequent access cycles in a burst                                                                                                   |

| <ul> <li>CS2WCR, CS3WCR</li> </ul>                 |      |                     |            |                  |                    | access.<br>Valid for byte-selection SRAM with page mode                                                                                                                                                  |

|                                                    |      |                     |            |                  |                    | specified (PMD bit = 1).<br>00: 0 cycle                                                                                                                                                                  |

|                                                    |      |                     |            |                  |                    | 01: 1 cycle                                                                                                                                                                                              |

|                                                    |      |                     |            |                  |                    | 10: 2 cycles<br>11: 3 cycles                                                                                                                                                                             |

|                                                    |      |                     |            |                  |                    | Note: Bit position is different from that of burst ROM (asynchronous).                                                                                                                                   |

| 11.4.4 Reset Bus Wait<br>Counter (RBWTCNT)         | 326  | Newly added         |            |                  |                    |                                                                                                                                                                                                          |

| 11.4.5 SDRAM Control                               | 327  | Figure amende       | ed         |                  |                    |                                                                                                                                                                                                          |

| Register (SDCR)                                    |      | В                   | lit: 31 30 | 29 28            | 27 26              | 25 24 23 22 21 20 19 18 17 16                                                                                                                                                                            |

|                                                    |      | Initial valu        | e: 0 0     |                  | 0 0                |                                                                                                                                                                                                          |

|                                                    |      | R/V                 |            | RR               | RR                 |                                                                                                                                                                                                          |

|                                                    |      | В                   | lit: 15 14 | 13 12            | 11 10<br>RFSH RMOR | 9         8         7         6         5         4         3         2         1         0           DE         PDOWN         BACTV         —         —         A3ROW[1:0]         —         A3COL[1:0] |

|                                                    |      | Initial valu<br>R/V |            | 0 0<br>R R       | 0 0<br>R/W R/V     |                                                                                                                                                                                                          |

|                                                    | 328  | Table amende        | d          |                  |                    |                                                                                                                                                                                                          |

|                                                    |      |                     |            | Initial          |                    |                                                                                                                                                                                                          |

|                                                    |      | Bit<br>15 to 12     | Bit Name   | All 0            | R/W                | Description<br>Reserved                                                                                                                                                                                  |

|                                                    |      |                     |            |                  |                    | These bits are always read as 0. The write value should always be 0.                                                                                                                                     |

|                                                    |      | 11                  | RFSH       | 0                | R/W                | Refresh Control                                                                                                                                                                                          |

|                                                    |      |                     |            |                  |                    | Specifies whether or not the refresh operation of the<br>SDRAM is performed.                                                                                                                             |

|                                                    |      |                     |            |                  |                    | 0: No refresh                                                                                                                                                                                            |

| 11.4.6 Refresh Timer                               | 330  | Table amende        | 4          |                  |                    | 1: Refresh                                                                                                                                                                                               |

| Control/Status Register                            | 550  | Table amender       | u          | Initial          |                    |                                                                                                                                                                                                          |

| (RTCSR)                                            |      | Bit                 | Bit Name   |                  | R/W                | Description                                                                                                                                                                                              |

|                                                    |      | 31 to 8             | _          | All 0            | R                  | Reserved<br>These bits are always read as 0. The write value should<br>always be H'A55A00.                                                                                                               |

| 11.4.7 Refresh Timer Counter                       | 332  | Table amende        |            |                  |                    |                                                                                                                                                                                                          |

| (RTCNT)                                            | 502  |                     | ~          | Initial          |                    |                                                                                                                                                                                                          |

|                                                    |      | Bit                 | Bit Name   | Value            | R/W                | Description                                                                                                                                                                                              |

|                                                    |      | 31 to 8             | _          | All 0            | R                  | Reserved<br>These bits are always read as 0. The write value should<br>always be H'A55A00.                                                                                                               |

| 11.4.8 Refresh Time Constant                       | 333  | Table amende        | <br>d      |                  |                    |                                                                                                                                                                                                          |

| Register (RTCOR)                                   |      |                     | -          | ا م افا ما       |                    |                                                                                                                                                                                                          |

|                                                    |      | Bit                 | Bit Name   |                  | R/W                | Description                                                                                                                                                                                              |

|                                                    |      | 31 to 8             | _          | All 0            | R                  | Reserved<br>These bits are always read as 0. The write value should                                                                                                                                      |

|                                                    |      |                     |            |                  |                    | always be H'A55A00.                                                                                                                                                                                      |

| Item                                                       | Page | Revisior                                                                                                                                                               | n (See                                                | Manual                                                  | for Det                                   | ails)                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 11.5.5 SDRAM Interface                                     |      | Deleted                                                                                                                                                                |                                                       |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| (12) Low-Power SDRAM                                       |      |                                                                                                                                                                        |                                                       |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 11.5.6 Burst ROM (Clock                                    | 385  | Note add                                                                                                                                                               | led                                                   |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Asynchronous) Interface                                    |      | Note: When using the CS0 space as burst ROM, set CS0BCR and CS0WCI using a program in a space other than CS0 (on-chip RAM, for example before accessing the burst ROM. |                                                       |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 11.5.8 PCMCIA Interface                                    | 392  | Descripti                                                                                                                                                              | on am                                                 | ended                                                   |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                            |      | PCMCIA<br>space ca                                                                                                                                                     | interfa<br>in be u<br>pecifica                        | ice can b<br>sed for th<br>ations ver                   | e spec<br>ne IC m<br>sion 4.              | ified ir<br>iemor<br>2 (PC            | elected using the MAP bit in CMNCR, the<br>n areas 5 and 6. Areas 5 and 6 in the physical<br>y card and I/O card interface defined in the<br>MCIA2.1 ) by specifying the TYPE[3:0] bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 11.6 Usage Notes                                           | 403  | Description amended                                                                                                                                                    |                                                       |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| (1) Reset                                                  |      | access.<br>counter (<br>maintains<br>counted<br>generate<br>not clear                                                                                                  | Fo ens<br>RBWT<br>s the 0<br>up syn<br>d until<br>ed. | ure this n<br>CNT). Th<br>state du<br>chronous<br>RBWTC | ninimu<br>ne cour<br>ring the<br>sly toge | n time<br>nter is<br>e rese<br>ther v | minimum time from reset release to the first<br>e, the bus state controller supports a 7-bit<br>cleared to 0 by a power-on reset and it<br>t period. After power-on reset, RBWTCNT is<br>vith CKO and an external access will not be<br>d up to H'007F. At manual reset, RBWTCNT is                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 12.3.7 DMA Channel Control<br>Registers (CHCR_0 to CHCR_5) | 418  | Table an                                                                                                                                                               | nended                                                | 1                                                       |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                            |      |                                                                                                                                                                        | Bit                                                   | Bit Name                                                | Initial<br>Value                          | R/W                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                            |      |                                                                                                                                                                        | 23                                                    | DO                                                      | 0                                         | R/W                                   | DMA Overrun<br>Selects whether detection takes place at overrun 0 or<br>overrun 1 when DREQ level detection is used. This bit<br>is valid only in CHCR_0 and CHCR_1.<br>0: Detects DREQ by overrun 0<br>1: Detects DREQ by overrun 1                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                            | 420  | Table amended                                                                                                                                                          |                                                       |                                                         |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                            |      |                                                                                                                                                                        | Bit<br>18                                             | Bit Name<br>HIE                                         | Initial<br>Value<br>O                     | <b>R/W</b><br>R/W                     | Description<br>Half End Interrupt Enable<br>Specifies whether an interrupt request is generated to<br>the CPU when the read cycle of the transfer that the<br>number of transfers is decreased to half of the TCR<br>value set before the transfer has ended. If the HIE bit is<br>set to 1, an interrupt request is generated to the CPU<br>when the HE bit is set. To confirm that the half of the<br>transfer has ended, execute a dummy read of the<br>destination space after issuing the SYNCO instruction.<br>Clear this bit to 0 while reload mode is set. This bit is<br>valid in CHCR_0 to CHCR_3.<br>0: Half end interrupt disabled<br>1: Half end interrupt enabled |  |  |

| 12.3.7 DMA Channel Control                                 | 423  | Table an                                                                                                                                                               | nended                                                | 1                                                       |                                           |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Registers (CHCR_0 to CHCR_5)                               |      |                                                                                                                                                                        | Bit                                                   | Bit Name                                                | Initial<br>Value                          | R/W                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |