# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU&MCU                                   | Document<br>No.                          | TN-SH7-A641A/E        | Rev.                                                                                                      | 1.00                   |  |  |

|-----------------------|-------------------------------------------|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|------------------------|--|--|

| Title                 | SH7720 hardware manual revised to Rev.3.0 | 7720 hardware manual revised to Rev.3.00 |                       |                                                                                                           | Technical Notification |  |  |

| Applicable<br>Product |                                           | Lot No.                                  |                       | SH7720 Hardware Manual                                                                                    |                        |  |  |

|                       | SH3-DSP SH7700 Series<br>SH7720 Group     | All                                      | Reference<br>Document | (REJ09B0033-0200 Rev.2.00)<br>SH7720 Group, SH7721 Group<br>Hardware Manual<br>(REJ09B0033-0300 Rev.3.00) |                        |  |  |

SH7720 Hardware Manual is revised from Rev.2.00 to Rev.3.00. SH7720 and SH7320 Group Hardware Manuals are merged into manual Rev.3.00, to which the SH7721 Group is newly added. All the pins in the SD host interface (SDHI) are added. Please refer to main revisions and additions in Rev.3.00 as shown in the following.

| Item                    | Page | Revision (See Manual for Details)                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------------|------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| All                     |      | SH7720 and SH7320 Group Hardware Manuals are merged into this manual, to which the SH7721 Group newly added. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| All                     |      | The pins in the SD host interface (SDHI) are added.                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Introduction            | viii | Added                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Abbreviations           |      | DES                                                                                                          | Data Encryption Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                         |      | RSA                                                                                                          | Rivest Shamir Adleman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                         |      | SSL                                                                                                          | Secure Socket Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                         |      | SDHI                                                                                                         | SD Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Section 1 Overview      | 5    | Deleted                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Table 1.1 SH7720/SH7721 |      | Item                                                                                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Features                |      | Serial<br>I/O with<br>FIFO<br>(SIOF0,<br>SIOF1)                                                              | <ul> <li>Internal 64-byte transmit/receive FIFO</li> <li>Supports 8-/16-/16-bit stereo sound input/output</li> <li>Sampling rate clock input selectable from P         <ul> <li>and external pin</li> <li>Internal prescaler for P             </li> <li>SPI mode                 <ul> <li>Providec continuous full duplex-communication with SPI slave-device in fixed master mode.</li> <li>Transmit/receive data length of fixed 8 bits</li> <li>With interrupt request and DMAC request</li></ul></li></ul></li></ul> |  |  |  |  |

| Item                                       | Page | Revision (See Manual for Details)                                                                   |  |  |  |  |  |

|--------------------------------------------|------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Table 1.1 SH7720/SH7721                    | 6, 7 | Amended                                                                                             |  |  |  |  |  |

| Features                                   |      | Item Features                                                                                       |  |  |  |  |  |

|                                            |      | PC card • Complies with the PCMCIA Rev.2.1/JEIDA<br>controller Version 4.2                          |  |  |  |  |  |

|                                            |      | (PCC) Supports the IC memory card interface and I/O card interface                                  |  |  |  |  |  |

|                                            |      | A/D • 10 bits ± 4 LSB, four channels                                                                |  |  |  |  |  |

|                                            |      | converter • Conversion time: 15 μs                                                                  |  |  |  |  |  |

|                                            |      | (ADC) Input range: 0 to AV <sub>cc</sub> (max. 3.6 V)                                               |  |  |  |  |  |

|                                            |      | SD host Added<br>interface<br>(SDHI)                                                                |  |  |  |  |  |

|                                            |      | Note: Only<br>for models<br>with the<br>SDHI                                                        |  |  |  |  |  |

|                                            |      | SSL • RSA encryption                                                                                |  |  |  |  |  |

|                                            |      | accelerator • Supported operations: addition, subtraction,<br>(SSL) multiplication, power operation |  |  |  |  |  |

|                                            |      | Note: DES and Triple-DES encryption/decryption<br>SH7720<br>group only                              |  |  |  |  |  |

| Table 1.2 Product Lineup<br>(SH7720 Group) | 8, 9 | Replaced and table numbers assigned                                                                 |  |  |  |  |  |

| Table 1.3 Product Lineup<br>(SH7721 Group) |      |                                                                                                     |  |  |  |  |  |

| 1.2 Block Diagram                          | 10   | SDHI and its related pins added; bridges and clocks                                                 |  |  |  |  |  |

| Figure 1.1 Block Diagram                   |      | deleted.                                                                                            |  |  |  |  |  |

| Item                                                      | Page | Revision (See Manual for Details) |                               |                          |                                                                               |  |  |  |  |  |

|-----------------------------------------------------------|------|-----------------------------------|-------------------------------|--------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| 1.3 Pin Assignments                                       | 11   | Amended                           |                               |                          |                                                                               |  |  |  |  |  |

| 1.3.1 Pin Assignments                                     |      | $K17 \rightarrow SCIF$            |                               |                          |                                                                               |  |  |  |  |  |

| Figure 1.2 Pin Assignments<br>(PLBG0256GA-A (BP-256H/HV)) |      | $L17 \rightarrow SCIF$            |                               |                          |                                                                               |  |  |  |  |  |

| Figure 1.3 Pin Assignments                                | 12   | Amended                           |                               |                          |                                                                               |  |  |  |  |  |

| (PLBG0256KA-A (BP-256C/CV))                               |      | L20→SCIF0                         | _TxD/IrTX/P                   | TT2                      |                                                                               |  |  |  |  |  |

|                                                           |      | L21→SCIF0                         | _RxD/IrRX/F                   | PTT1                     |                                                                               |  |  |  |  |  |

|                                                           |      | $K1 \rightarrow VssQ1$            |                               |                          |                                                                               |  |  |  |  |  |

|                                                           |      | L1→VccQ1                          |                               |                          |                                                                               |  |  |  |  |  |

|                                                           |      | U5→D5                             |                               |                          |                                                                               |  |  |  |  |  |

| Table 1.4 List of Pin Assignments                         | 24   | Amended                           |                               |                          |                                                                               |  |  |  |  |  |

|                                                           |      | Pin No.<br>(PLBG0256<br>GA-A)     | Pin No.<br>(PLBG0256<br>KA-A) | Pin<br>Name              | Function                                                                      |  |  |  |  |  |

|                                                           |      | U16                               | V15                           | DACK0/<br>PINT1/<br>PTM4 | DMA transfer request<br>reception/ port<br>interrupt/<br>general-purpose port |  |  |  |  |  |

|                                                           |      | Y12                               | Y11                           | CS0                      | Chip select                                                                   |  |  |  |  |  |

|                                                           |      | Y13                               | Y12                           | RD                       | Read strobe                                                                   |  |  |  |  |  |

|                                                           |      | Y14                               | Y13                           | VssQ1                    | I/O power supply (0 V                                                         |  |  |  |  |  |

|                                                           |      | Y18                               | AA17                          | DACK1/<br>PTM5           | DMA transfer request<br>reception/<br>general-purpose port                    |  |  |  |  |  |

| 1.3.2 Pin Functions                           | 26, | Amended                                         |                                   |                         |                                                                                                         |

|-----------------------------------------------|-----|-------------------------------------------------|-----------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|

| Table 1.5 SH7720/SH7721 Pin                   | 29, | Classifica-                                     |                                   |                         |                                                                                                         |

| Functions                                     | 32  | tion                                            | Symbol                            | Name                    | Function                                                                                                |

|                                               |     | Clock                                           | XTAL                              | Crystal                 | For connection to a crystal resonator.                                                                  |

|                                               |     |                                                 | СКІО                              | System clock            | Used as a pin to input external clock or output clock.                                                  |

|                                               |     | Direct memory<br>access<br>controller<br>(DMAC) | DREQ0,<br>DREQ1                   | DMA-transfer<br>request | Input pins for external requests<br>for DMA transfer                                                    |

|                                               |     |                                                 | DACK0,                            | DMA transfer            | Indicates the acceptance of                                                                             |

|                                               |     |                                                 | DACK1                             | request<br>reception    | DMA transfer requests to<br>external devices.                                                           |

|                                               |     | Serial I/O with<br>FIFO (SIOF)                  | SIOF0_SYN<br>C,<br>SIOF1_SYN<br>C | SIOF frame<br>sync      | SIOF frame synchronization signals                                                                      |

|                                               |     |                                                 | SIOF0_TxD,<br>SIOF1_TxD           | SIOF<br>transmit data   | SIOF transmit data pin                                                                                  |

|                                               |     |                                                 | SIOF0_RxD,<br>SIOF1_RxD           | SIOF receive<br>data    | SIOF receive data pin                                                                                   |

|                                               |     | A/D converter<br>(ADC)                          | AN3 to AN0                        |                         | Analog input pin                                                                                        |

|                                               |     |                                                 | AVcc                              |                         | Power supply pin for the A/D o<br>D/A converter. When the A/D<br>or D/A converter is not in use,        |

|                                               |     |                                                 |                                   |                         | connect this pin to input/output power supply (VccQ).                                                   |

|                                               |     |                                                 | AVss                              |                         | Ground pin for the A/D or D/A<br>converter. Connect this pin to<br>input/output power supply<br>(VssQ). |

| 1.3.2 Pin Functions                           | 35  | Notes adde                                      | d                                 |                         |                                                                                                         |

|                                               |     |                                                 |                                   |                         |                                                                                                         |

|                                               |     | 6. SDHI ass<br>including the                    |                                   | ns support              | only for the models                                                                                     |

| Section 2 CPU                                 | 37  | Deleted                                         |                                   |                         |                                                                                                         |

| 2.1 Processing States and<br>Processing Modes |     | LSI on-chip                                     | modules,                          |                         | tents of a part of the<br><del>e bue state controllor</del>                                             |

| 2.1.1 Processing States                       |     | <del>(BSC), </del> are i                        | retained.                         |                         |                                                                                                         |

| (1) Reset State                               |     |                                                 |                                   |                         |                                                                                                         |

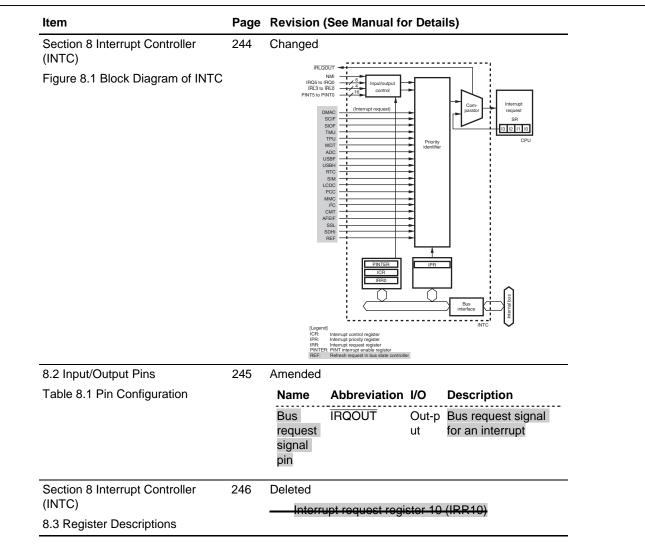

| Item                                         | Page | Revision                                                   | (See Manual f                                             | or Details)                                                                        |                                   |  |  |  |  |

|----------------------------------------------|------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| 8.3.1 Interrupt Priority Registers A         |      | Amended                                                    |                                                           |                                                                                    |                                   |  |  |  |  |

| to J (IPRA to IPRJ)                          |      | Register                                                   | Bits 15 to 12                                             | Bits 7 to 4                                                                        | Bits 3 to 0                       |  |  |  |  |

| Table 8.2 Interrupt Sources and IPRA to IPRJ |      | IPRD                                                       | Reserved*                                                 | IRQ5                                                                               | IRQ4                              |  |  |  |  |

|                                              |      | IPRG                                                       | SCIF0                                                     | Reserved*                                                                          | Reserved*                         |  |  |  |  |

|                                              |      | IPRJ                                                       | Reserved*                                                 | SDHI                                                                               | AFEIF                             |  |  |  |  |

|                                              |      | Note: *                                                    | should always b<br>bits are effective                     | ys read as 0. The<br>e 0. The SSL an<br>e only for the mod<br>l bits apply if they | d SDHI -related dels that include |  |  |  |  |

| 8.3.4 Interrupt Request Register 0           | 252  | Changed                                                    |                                                           |                                                                                    |                                   |  |  |  |  |

| (IRR0)                                       |      |                                                            | n 8-bit register t<br>from the TMU a                      |                                                                                    |                                   |  |  |  |  |

|                                              |      |                                                            | Initial                                                   |                                                                                    |                                   |  |  |  |  |

|                                              |      |                                                            | Name Value                                                | R/W Descript                                                                       |                                   |  |  |  |  |

|                                              |      | 7 —                                                        | 0                                                         | R Reserved                                                                         |                                   |  |  |  |  |

|                                              |      |                                                            |                                                           |                                                                                    | always read as ite value should   |  |  |  |  |

|                                              |      |                                                            |                                                           | always be                                                                          | e 0.                              |  |  |  |  |

| 8.3.5 Interrupt Request Register 1           | 253  | Deleted                                                    |                                                           |                                                                                    |                                   |  |  |  |  |

| (IRR1)                                       | 200  | IRR1 is an 8-bit register that indicates whether interrupt |                                                           |                                                                                    |                                   |  |  |  |  |

|                                              |      | requests from the DMAC <del>and LCDC</del> are generated.  |                                                           |                                                                                    |                                   |  |  |  |  |

| 8.3.6 Interrupt Request Register 2           | 254  | Changed                                                    |                                                           |                                                                                    | -                                 |  |  |  |  |

| (IRR2)                                       |      | IRR2 is a                                                  | n 8-bit register t                                        | hat indicates w                                                                    | hether interrup                   |  |  |  |  |

|                                              |      | register is                                                | from the SSL ar<br>initialized to H<br>eset, but is not i | 00 by a power-                                                                     | on reset or                       |  |  |  |  |

|                                              |      | Note: On                                                   | the models not                                            | having the SSI                                                                     | L, the                            |  |  |  |  |

|                                              |      | SSL-relat<br>always be                                     | ed bits are rese<br>e 0.                                  | rved. The write                                                                    | value should                      |  |  |  |  |

|                                              |      | Added                                                      |                                                           |                                                                                    |                                   |  |  |  |  |

|                                              |      | Bit Bit                                                    | Name Descripti                                            | on                                                                                 |                                   |  |  |  |  |

|                                              |      | 4 SSI                                                      |                                                           | rrupt Request                                                                      |                                   |  |  |  |  |

|                                              |      |                                                            |                                                           |                                                                                    |                                   |  |  |  |  |

|                                              |      |                                                            | Note:                                                     |                                                                                    | s not having the                  |  |  |  |  |

|                                              |      |                                                            |                                                           | bit is reserved an                                                                 |                                   |  |  |  |  |

| Item                                          | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 8.3.12 Interrupt Request Register             | 261  | Chan                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ged                                                      |                                                                                                                                                                                                                                                                  |  |  |  |  |

| 8 (IRR8)                                      |      | reque<br>gene<br>powe<br>stand                                                                                                                                                                                                                                                                                                                                                                                                                                          | ests from<br>rated. Th<br>r-on rese<br>by mode<br>On the | bit register that indicates whether interrupt<br>the SDHI, MMC, and AFEIF are<br>his register is initialized to H'00 by a<br>et or manual reset, but is not initialized in<br>e.<br>models not having the SDHI, the<br>elated bits are reserved. The write value |  |  |  |  |

|                                               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | should                                                   | always be 0.                                                                                                                                                                                                                                                     |  |  |  |  |

|                                               |      | Chan                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ged and                                                  | a note added.                                                                                                                                                                                                                                                    |  |  |  |  |

|                                               |      | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>Name                                              | Description                                                                                                                                                                                                                                                      |  |  |  |  |

|                                               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SDIR                                                     | SDI Interrupt Request                                                                                                                                                                                                                                            |  |  |  |  |

|                                               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | Indicates whether the SDI (SDHI) interrupt request is generated.                                                                                                                                                                                                 |  |  |  |  |

|                                               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 0: SDI interrupt request is not<br>generated                                                                                                                                                                                                                     |  |  |  |  |

|                                               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | 1: SDI interrupt request is generated                                                                                                                                                                                                                            |  |  |  |  |

|                                               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | Note: On the models not having the SDHI, this bit is reserved and always read as 0. The write value should always be 0.                                                                                                                                          |  |  |  |  |

|                                               | 202  | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a d a al                                                 |                                                                                                                                                                                                                                                                  |  |  |  |  |

| 8.3.13 Interrupt Request Register<br>9 (IRR9) | 262  | Amended<br>IRR9 is an 8-bit register that indicates whether interrup<br>requests from the PCC, USBH, USBF, and CMT are<br>generated. This register is initialized to H'00 by a<br>power-on reset or manual reset, but is not initialized in<br>standby mode.                                                                                                                                                                                                            |                                                          |                                                                                                                                                                                                                                                                  |  |  |  |  |

| 8.4.3 IRL interrupts                          | 267  | Delet                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ed                                                       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                               |      | IRL interrupts are included with noise canceller function<br>and detected when the sampled levels of each<br>peripheral module clock keep same value for 2 cycles.<br>This prevents sampling error level in IRL pin changing.<br>In standby mode, noise canceller is handled by the<br>RTC clock because the peripheral module clocks are<br>halted. Therefore, when RTC is not used, recovering to<br>standby by IRL interrupts cannot be executed in<br>ctandby mode. |                                                          |                                                                                                                                                                                                                                                                  |  |  |  |  |

| Item                                                           | Page | Revis                                                                                                                                                                                        | sion (Se   | e Man               | ual for D            | Details)                |                               |                     |  |

|----------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|----------------------|-------------------------|-------------------------------|---------------------|--|

| 8.4.4 PINT Interrupts                                          | 268  | Adde                                                                                                                                                                                         | b          |                     |                      |                         |                               |                     |  |

|                                                                |      | While an RTC clock is supplied, recovery from a<br>standby state on a PINT interrupt is possible if the<br>interrupt level is higher than that set in the I3 to I0 bi<br>of the SR register. |            |                     |                      |                         |                               |                     |  |

| 8.4.6 Interrupt Exception Handling and Priority                | 270  | Amm                                                                                                                                                                                          | ended      |                     | Interrupt            |                         | Priority                      |                     |  |

| Table 8.3 Interrupt Exception<br>Handling Sources and Priority |      | Interr                                                                                                                                                                                       | upt Source | Interru<br>pt Code  | Priority<br>(Initial | IPR<br>(Bit<br>Numbers) | within IPR<br>Setting<br>Unit | Default<br>Priority |  |

| (IRQ Mode)                                                     |      |                                                                                                                                                                                              | USBHI      |                     | 0 to 15 (0)          | IPRJ<br>(11 to 8)       | _                             |                     |  |

|                                                                |      | DMA<br>C (2)                                                                                                                                                                                 | DEI4       | H'B80* <sup>3</sup> | 0 to 15 (0)          | IPRF<br>(11 to 8)       | High                          |                     |  |

|                                                                |      |                                                                                                                                                                                              | DEI5       | H'BA0* <sup>3</sup> |                      |                         | Low                           |                     |  |

|                                                                |      | TMU                                                                                                                                                                                          | TMU_SUNI   | H'6C0               | 0 to 15 (0)          | IPRD<br>(11 to 8)       | _                             |                     |  |

|                                                                |      |                                                                                                                                                                                              | _          |                     |                      | _                       | _                             |                     |  |

| Item                                                                         | Page | Revis | Revision (See Manual for Details) |                     |                                          |                      |                                        |              |  |

|------------------------------------------------------------------------------|------|-------|-----------------------------------|---------------------|------------------------------------------|----------------------|----------------------------------------|--------------|--|

| Table 8.4 Interrupt Exception<br>Handling Sources and Priority<br>(IRL Mode) | 272  | Chan  | ged                               | Interrupt<br>Code   | Interrupt<br>Priority<br>(Initial Value) | IPR<br>(Bit Numbers) | Priority<br>within IPR<br>Setting Unit | Defa<br>Prio |  |

|                                                                              |      | NMI   |                                   |                     |                                          |                      |                                        |              |  |

|                                                                              |      | H-UDI |                                   |                     |                                          |                      |                                        |              |  |

|                                                                              |      | IRL   | IRL3 to<br>RL0=B'0000             | H'200* <sup>3</sup> | 15                                       | -                    | -                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0001            | H'220* <sup>3</sup> | 14                                       | —                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0010            | H'240* <sup>3</sup> | 13                                       | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0011            | H'260* <sup>3</sup> | 12                                       | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0100            | H'280* <sup>3</sup> | 11                                       | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0101            | H'2A0* <sup>3</sup> | 10                                       | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0110            | H'2C0* <sup>3</sup> | 9                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'0111            | H'2E0* <sup>3</sup> | 8                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1000            | H'300* <sup>3</sup> | 7                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1001            | H'320* <sup>3</sup> | 6                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1010            | H'340* <sup>3</sup> | 5                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1011            | H'360* <sup>3</sup> | 4                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1100            | H'380* <sup>3</sup> | 3                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1101            | H'3A0* <sup>3</sup> | 2                                        | _                    | _                                      |              |  |

|                                                                              |      |       | IRL3 to<br>IRL0=B'1110            | H'3C0* <sup>3</sup> | 1                                        |                      | _                                      |              |  |

|                                                                              |      | тми   | TMU_SUNI                          | H'6C0               | 0 to 15 (0)                              | IPRD<br>(11 to 8)    | _                                      |              |  |

|                                                                              |      | _     | _                                 | -                   | -                                        | -                    | -                                      |              |  |

| Item                           | Page | Revision                                                                                                   | (See Ma | or Details)     |                                                                        |  |  |  |  |

|--------------------------------|------|------------------------------------------------------------------------------------------------------------|---------|-----------------|------------------------------------------------------------------------|--|--|--|--|

| Section 9 Bus State Controller | 283, | Amended                                                                                                    |         |                 |                                                                        |  |  |  |  |

| (BSC)                          | 284  | Name                                                                                                       | I/O     | Funct           | tion                                                                   |  |  |  |  |

| 9.2 Input/Output Pins          |      | RD/WR                                                                                                      | 0       | Read/           | /write signal                                                          |  |  |  |  |

| Table 9.1 Pin Configuration    |      |                                                                                                            |         |                 | ects to $\overline{WE}$ pins when $M$ or byte-selection SRAM is ected. |  |  |  |  |

|                                |      | RD                                                                                                         | 0       |                 | strobe (read data output<br>e signal)                                  |  |  |  |  |

|                                |      |                                                                                                            |         | memo            | be signal to indicate the<br>bry read cycle when the<br>CIA is used.   |  |  |  |  |

|                                |      | WAIT                                                                                                       | I       |                 | nal wait input (sampled at the edge of CKIO)                           |  |  |  |  |

|                                |      | REFOUT                                                                                                     | 0       | Bus m<br>refres | nastership request signal for<br>hing                                  |  |  |  |  |

|                                |      |                                                                                                            |         |                 |                                                                        |  |  |  |  |

| 9.3.2 Shadow Area              | 285  | Changed                                                                                                    |         |                 |                                                                        |  |  |  |  |

|                                |      | The BSC decodes A28 to A25 of the physical address<br>and generates chip select signals that correspond to |         |                 |                                                                        |  |  |  |  |

|                                |      | •                                                                                                          |         | •               | A, and 6B.                                                             |  |  |  |  |

| 9.4.1 Common Control Register  | 291  | Amended                                                                                                    |         |                 |                                                                        |  |  |  |  |

| (CMNCR)                        |      | Bit                                                                                                        | Initial |                 |                                                                        |  |  |  |  |

|                                |      | Bit Nam                                                                                                    | e Value | R/W             | Description                                                            |  |  |  |  |

|                                |      | 31 to —                                                                                                    | All 0   | R               | Reserved                                                               |  |  |  |  |

|                                |      | 16                                                                                                         |         |                 | These bits are always read as 0. The write value should always be 0.   |  |  |  |  |

|                                |      | 15                                                                                                         | 0       | R               | Reserved                                                               |  |  |  |  |

|                                |      |                                                                                                            |         |                 | This bit is always read as 0. The write value should always be 0.      |  |  |  |  |

| Item                             | Page | e Revision (See Manual for Details) |          |                                            |  |  |  |

|----------------------------------|------|-------------------------------------|----------|--------------------------------------------|--|--|--|

| 9.4.2 CSn Space Bus Control      | 294  | Changed                             |          |                                            |  |  |  |

| Register (CSnBCR)                |      | Bit                                 | Bit Name | Description                                |  |  |  |

|                                  |      | 30                                  | IWW2     | Idle Cycles between Write-Read Cycles      |  |  |  |

|                                  |      | 29                                  | IWW1     | and Write-Write Cycles                     |  |  |  |

|                                  |      | 28                                  | IWW0     |                                            |  |  |  |

|                                  |      |                                     |          | 000: No idle cycle                         |  |  |  |

|                                  |      |                                     |          | ·<br>·<br>· · · · · ·                      |  |  |  |

| 9.4.3 CSn Space Wait Control     |      | Adde                                | d        |                                            |  |  |  |

| Register (CSnWCR)                |      | Bit                                 | R/W      | Description                                |  |  |  |

| (1) Normal Space, Byte-Selection |      |                                     | R/W      |                                            |  |  |  |

| SRAM                             |      | 9                                   | R/W      | Specify the number of wait cycles that are |  |  |  |

| CSOWCR, CS6BWCR                  |      | 8                                   | R/W      | necessary for read or write access.        |  |  |  |

| CS2WCR, CS3WCR                   |      | .7                                  | R/W      |                                            |  |  |  |

| CS4WCR                           |      |                                     |          |                                            |  |  |  |

| CS5AWCR                          |      |                                     |          |                                            |  |  |  |

| CS5BWCR                          |      |                                     |          |                                            |  |  |  |

| CS6AWCR                          |      |                                     |          |                                            |  |  |  |

| CS4WCR                           |      | Adde                                | d        |                                            |  |  |  |

| CS5AWCR                          |      | Bit                                 | Bit Name | Description                                |  |  |  |

| CS5BWCR                          |      | 18                                  | R/W      |                                            |  |  |  |

|                                  |      | 17                                  | R/W      | Specify the number of cycles that are      |  |  |  |

|                                  |      | 16                                  | R/W      | necessary for write access.                |  |  |  |

|                                  |      |                                     |          | 000: The same cycles as WR3 to WR0         |  |  |  |

|                                  |      |                                     |          | setting (read or write access wait)        |  |  |  |

| ltem                                                                                 | Page | e Revision (See Manual for Details) |                       |                |                                                                                                                       |  |  |  |  |

|--------------------------------------------------------------------------------------|------|-------------------------------------|-----------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 9.4.4 SDRAM Control Register                                                         | 326  | Amer                                | Amended               |                |                                                                                                                       |  |  |  |  |

| (SDCR)                                                                               |      |                                     | Bit                   | 1              |                                                                                                                       |  |  |  |  |

|                                                                                      |      | Bit                                 | Name                  | R/W            | Description                                                                                                           |  |  |  |  |

|                                                                                      |      | 12                                  |                       | R              | Reserved                                                                                                              |  |  |  |  |

|                                                                                      |      |                                     |                       |                | This bit is always read as 0. The                                                                                     |  |  |  |  |

|                                                                                      |      |                                     |                       | -              | write value should always be 0.                                                                                       |  |  |  |  |

|                                                                                      |      | 11                                  | RFSH                  | R/W            | Refresh Control                                                                                                       |  |  |  |  |

|                                                                                      |      |                                     |                       |                | Specifies whether or not the refresh                                                                                  |  |  |  |  |

|                                                                                      |      |                                     |                       |                | operation of the SDRAM is                                                                                             |  |  |  |  |

|                                                                                      |      |                                     |                       |                | performed.                                                                                                            |  |  |  |  |

|                                                                                      |      |                                     |                       |                | 0: No refresh                                                                                                         |  |  |  |  |

|                                                                                      |      |                                     |                       | <u>.</u>       | 1: Refresh                                                                                                            |  |  |  |  |

| 9.5.5 SDRAM Interface                                                                |      | Delet                               | ed                    |                |                                                                                                                       |  |  |  |  |

| (10) Low-Frequency Mode                                                              |      |                                     |                       |                |                                                                                                                       |  |  |  |  |

| 9.5.7 Byte-Selection SRAM<br>Interface                                               | 390  | Changed                             |                       |                |                                                                                                                       |  |  |  |  |

| Figure 9.34 Wait Timing for<br>Byte-Selection SRAM (BAS = 1)<br>(Software Wait Only) |      |                                     |                       |                |                                                                                                                       |  |  |  |  |

| Figure 9.36 Example of                                                               | 391  | Chan                                | ged                   |                |                                                                                                                       |  |  |  |  |

| Connection with 16-Bit                                                               |      |                                     |                       |                | 64Kx16bit<br>SRAM                                                                                                     |  |  |  |  |

| Data-Width Byte-Selection SRAM                                                       |      |                                     |                       |                | SHAM<br>A15<br>CS<br>OE<br>U015<br>IIO0<br>UB<br>LB                                                                   |  |  |  |  |

| 9.5.8 PCMCIA Interface                                                               | 395  | Chan                                | ged                   |                |                                                                                                                       |  |  |  |  |

| (1) Basic Timing for Memory Card<br>Interface                                        |      | mem<br>betwe                        | ory card<br>een the c | nterfa<br>ommo | e memory space are used as an IC<br>ce, the REG signal that switches<br>n memory and attribute memory<br>an I/O port. |  |  |  |  |

|                                                                                        | Page | age Revision (See Manual for Details)                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |        |  |  |

|----------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--|--|