# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                |          | Document<br>No.         | TN-RZ*-A055A/E                                                             | Rev. | 1.00    |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|----------|-------------------------|----------------------------------------------------------------------------|------|---------|

| Title                 | RZ/T1 Group User's Manual: Hardware<br>Corrections and adding notification for the Ethernet<br>MAC and Ethernet Switch |          | Information<br>Category | Technical Notification                                                     |      |         |

|                       |                                                                                                                        | Lot No.  |                         | RZ/T1 Group User's Manual: Hardware<br>Rev1.40<br>R01UH0483EJ0140 Rev.1.40 |      |         |

| Applicable<br>Product | RZ/T1 Group                                                                                                            | All lots | Reference<br>Document   |                                                                            |      | ardware |

There are corrections and adding notifications for the Ethernet MAC and Ethernet Switch in User's manual.

Please use the Ethernet MAC and Ethernet Switch with the contents as shown below.

#### [Correction of User's manual]

### - Ethernet MAC

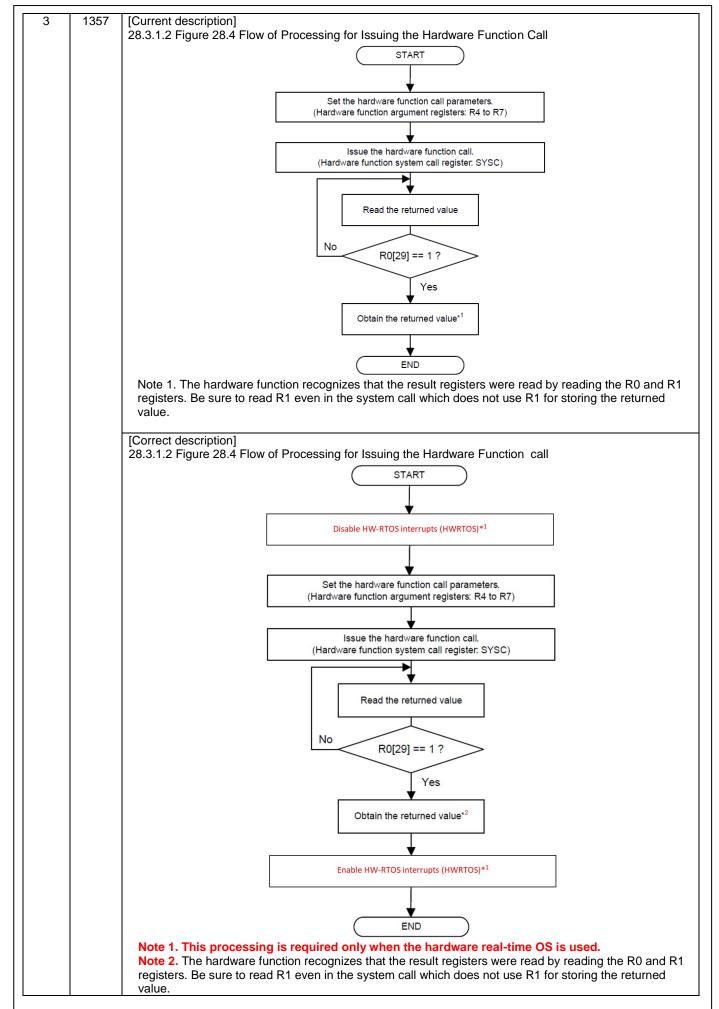

| No. | Page | Current description                                                                                                                                                                                                                                                                                    | Correct description                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | 1329 | 28.2.2.1 MIIM Register (GMAC_MIIM)<br>Note: The contents of the GMAC_MIIM register are valid<br>for the management interface that is set by the MAC<br>select register (MACSEL). In other conditions, writing to<br>the register is impossible and any values read from the<br>register are undefined. | 28.2.2.1 MIIM Register (GMAC_MIIM)<br>Note: The contents of the GMAC_MIIM register are valid<br>only when the EthernetMAC or the Ethernet Switch<br>Port is selected by the MAC select register (MACSEL)<br>In other conditions, writing to the register is impossible<br>and any values read from the register are undefined.                                    |  |  |

| 2   | 1334 | [Current description]<br><u>28.2.2.5 RX MODE Register (GMAC_RXMODE)</u><br>b29 SFRXFIFO Store & Forward For RX FI<br>[Correct description]                                                                                                                                                             | FO 1: Store & Forward mode R/W<br>The receive DMA controller does<br>not start operation until data up to<br>the end of the frame is written to RX<br>FIFO.<br>0: Cut Through mode                                                                                                                                                                                |  |  |

|     |      | 28.2.2.5 RX MODE Register (GMAC_RXMODE)<br>b29 SFRXFIFO Store & Forward For RX FI                                                                                                                                                                                                                      | FO 1: Store & Forward mode R/W<br>The reception DMA controller<br>starts to operate after data up to<br>the end of the frame is written to<br>the RX FIFO buffer.<br>0: Cut Through mode<br>The reception DMA controller<br>starts to operate after data is<br>written to the RX FIFO buffer.<br>The number of data words is<br>specified in the RRTTH[2:0] bits. |  |  |

## RENESAS TECHNICAL UPDATE TN-RZ\*-A055A/E

| 4 | 1358 | 28.3.1.3 Buffer Allocator<br>(1) Functional Overview<br>To use the buffer RAM, secure the required area<br>(hereafter "buffer") beforehand, and then issue the<br>hardware function calls provided for the buffer allocator.<br>The CPU attempting to write to an area which has not<br>been secured is ignored, but an exception is generated in<br>the case of access by the DMAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28.3.1.3 Buffer Allocator<br>(1) Functional Overview<br>To use the buffer RAM, secure the required area<br>(hereafter "buffer") beforehand, and then issue the<br>hardware function calls provided for the buffer allocator.<br>When writing to an area which has not been secured,<br>access by the CPU or MAC DMA controller generates<br>an interrupt, and access to such area by the buffer<br>RAM DMA controller generates an interrupt or returns<br>an exception to the return value register R0<br>depending on the type of hardware function calls.                                                                                                                                                                                                                                                                     |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | 1361 | [Current description]           28.3.1.3 (2) (e)           Table 28.7         HWFNC_LongBuffer_Get           R1         [31:0] First logical         [31:27] 00001b           address of the buffer         [26] 1           [25:18] LLID         [17:0] 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |      | [Correct description]           28.3.1.3 (2) (e)           Table 28.7 HWFNC_LongBuffer_Get           R1         [31:0] First logical address of the buffer           [26:24] 100b           [23:18] LLID           [17:0] 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6 | 1362 | [Current description]<br>28.3.1.3 (2) (e)<br>Table 28.8 HWFNC_ShortBuffer_Get<br>R1 [31:0] First logical<br>address of the buffer [26] 0<br>[25:18] SBID<br>[17:0] 0<br>[Correct description]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |      | 28.3.1.3 (2) (e)         Table 28.8 HWFNC_ShortBuffer_Get         R1       [31:0] First logical         address of the buffer       [26:25] 00b         [24:18] SBID         [17:0] 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7 | 1368 | <ul> <li>28.3.1.4 (2) (b) Usage</li> <li>[Example of reading and releasing a buffer] <ul> <li>(1) Read the BUFID register.</li> </ul> </li> <li>(2) Shift the bits [27:16] read from BUFID 16 bits to the right to obtain the number of received words.</li> <li>(3) The bits [15:0] read from the BUFID are bits [26:11] of the address where the acquired buffer starts. The individual bits of the address where the acquired buffer starts. The individual bits of the address where the acquired as follows.</li> <li>[31:27]: 00001b</li> <li>[26:19]: Equivalent to the bits [15:8] in the BUFID ([26] of the start address is always 1; [25:19] are LLID[6:0])</li> <li>[18:11]: Equivalent to the bits [7:0] in the BUFID (always 0)</li> <li>[10: 0]: Always 0</li> <li>(4) After using the buffer, specify the start address as an argument and issue the buffer release function call to release the buffer.</li> </ul> | <ul> <li>28.3.1.4 (2) (b) Usage<br/>[Example of reading and releasing a buffer]</li> <li>(1) Read the BUFID register.</li> <li>(2) Shift the bits [27:16] read from BUFID 16 bits to<br/>the right to obtain the number of received<br/>words.</li> <li>(3) The bits [15:0] read from the BUFID are bits<br/>[26:11] of the address where the acquired<br/>buffer starts. The individual bits of the address<br/>where the acquired buffer starts are<br/>configured as follows.</li> <li>[31:27]: 00001b</li> <li>[26:18]: Equivalent to the bits [15:7] in the BUFID</li> <li>[17:11]: Equivalent to the bits [6:0] in the BUFID</li> <li>[10: 0]: Always 0</li> <li>(4) After using the buffer, specify the start address<br/>as an argument and issue the buffer release<br/>function call to release the buffer.</li> </ul> |

| 8  | 1369 | <ul> <li>28.3.1.4 (2) (c) List of hardware function calls</li> <li>If an argument of a hardware function call is invalid, an invalid system call error code is returned in the return value register, R0.</li> <li>Access to an access-prohibited area (an area other than the buffer RAM, etc.) while the hardware function call is running leads to the return of an exception code in the return value register R0.</li> <li>28.3.1.4 (2) (c) List of hardware function calls if an argument of a hardware function call is invalid, an invalid system call error code is returned in the return value register, R0.</li> <li>If an error occurs while the hardware function call is running, an interrupt is generated.</li> </ul> |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | 1374 | <ul> <li>28.3.1.4 (3) (d) List of hardware function calls</li> <li>If an argument of a hardware function call is invalid, an invalid system call error code is returned in the return value register, R0.</li> <li>28.3.1.4 (3) (d) List of hardware function calls</li> <li>If an argument of a hardware function call is invalid, an invalid system call error code is returned in the return value register, R0.</li> <li>If an error occurs while the hardware function call is running, an interrupt is generated.</li> </ul>                                                                                                                                                                                                     |

| 10 | 1374 | [Current description]         28.3.1.4 (3) (d)         Table 28.16       HWFNC_MACDMA_TX_Errstat         R0       [1:0] Result       [0]: Memory Access Violation         [1]: Memory Access Timeout       [1]: Memory Access Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |      | [Correct description]         28.3.1.4 (3) (d)         Table 28.16       HWFNC_MACDMA_TX_Errstat         [0]:       0: Success         1: Memory Access Violation         • Access to the buffer that is not acquired         • The number of transfer bytes is not correct         • The start address of the descriptor is not on a 64-bit boundary.         [1]:         0: Success                                                                                                                                                                                                                                                                                                                                                 |

|    |      | 1: Memory Access Timeout         • The start address of a transmission descriptor turns to be an end value (FFFF FFFFh)         • Releasing the buffer automatically is failed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11 | 1376 | [Current description]         28.3.1.5 (2) (c)         Table 28.17       HWFNC_Direct_Memory_Transfer         Argument registers         R4       [31:0] Address where the<br>destination area for<br>transfer starts       Specifies the address where the source area for transfer<br>starts.         R5       [31:0] Address where the<br>source area for transfer<br>starts       Specifies the address where the destination area for transfer<br>starts.                                                                                                                                                                                                                                                                         |

|    |      | [Correct description]         28.3.1.5 (2) (c)         Table 28.17 HWFNC_Direct_Memory_Transfer         Argument registers         R4       [31:0] Address where the source area for transfer starts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |      | R5       [31:0] Address where the destination area for transfer destination area for transfer starts.         Specifies the address where the destination area for transfer starts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# RENESAS TECHNICAL UPDATE TN-RZ\*-A055A/E

| 12 | 1378 | [Current description]                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|------|-----------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | 28.3.2                                                    |                |                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |      | Table 28.19 Interrupts                                    | related to Ope | erations for Transmission                                                                                                                                                                                                                                                                                                                                                                               |

|    |      | Interrupt Name                                            | Symbol         | Conditions for Asserting and De-asserting Interrupts                                                                                                                                                                                                                                                                                                                                                    |

|    |      | MACDMA<br>transmission error<br>interrupt                 | ETHDTIE        | This interrupt is generated when the address field of a descriptor<br>is outside the range of the buffer, the number of bytes for transfer<br>is invalid, or a descriptor is not set to start on a 64-bit boundary.<br>Modify the settings of the transmission descriptor for<br>retransmission.<br>Since this interrupt is generated as a pulse, de-asserting the<br>interrupt source is not required. |

|    |      | [Correct description]<br>28.3.2<br>Table 28.19 Interrupts | related to Ope | erations for Transmission                                                                                                                                                                                                                                                                                                                                                                               |

|    |      | Interrupt Name                                            | Symbol         | Conditions for Asserting and De-asserting Interrupts                                                                                                                                                                                                                                                                                                                                                    |

|    |      | MACDMA                                                    | ETHDTIE        | This interrupt is generated when an error occurs while the                                                                                                                                                                                                                                                                                                                                              |

|    |      | transmission error                                        |                | transmission MAC DMA is operating. There are several error                                                                                                                                                                                                                                                                                                                                              |

|    |      | interrupt                                                 |                | sources and HWFNC_MACDMA_TX_Errstat is used to obtain                                                                                                                                                                                                                                                                                                                                                   |

|    |      |                                                           |                | the error source.                                                                                                                                                                                                                                                                                                                                                                                       |

|    |      |                                                           |                | Modify the settings of the transmission descriptor for<br>retransmission.                                                                                                                                                                                                                                                                                                                               |

|    |      |                                                           |                | Since this interrupt is generated as a pulse, de-asserting the<br>interrupt source is not required.                                                                                                                                                                                                                                                                                                     |

|    |      |                                                           |                |                                                                                                                                                                                                                                                                                                                                                                                                         |

## RENESAS TECHNICAL UPDATE TN-RZ\*-A055A/E

| lo. | Page | Contents              |                     |                      |            |                                     |     |

|-----|------|-----------------------|---------------------|----------------------|------------|-------------------------------------|-----|

| 1   | 1417 | [Current description] |                     |                      |            |                                     |     |

|     |      | 29.2.2.5              |                     | ocking Register (INF |            |                                     |     |

|     |      | b16                   | POLEARNDIS          | Port 0 Address       | Learning   | Sets the address learning of port 0 | R/W |

|     |      |                       |                     | Setting              |            | 0: Invalid                          |     |

|     |      | _                     |                     |                      |            | 1: Valid                            |     |

|     |      | b17                   | P1LEARNDIS          | Port 1 Address       | Learning   | Sets the address learning of port 1 | R/W |

|     |      |                       |                     | Setting              |            | 0: Invalid                          |     |

|     |      |                       |                     |                      |            | 1: Valid                            |     |

|     |      | b18                   | P2LEARNDIS          | Internal Interface   | Address    | Sets the address learning of the    | R/W |

|     |      |                       |                     | Learning Setting     |            | internal interface port (port 2)    |     |

|     |      |                       |                     |                      |            | 0: Invalid                          |     |

|     |      |                       |                     |                      |            | 1: Valid                            |     |

|     |      |                       | t description]      |                      |            |                                     |     |

|     |      |                       | 5 Input Learning Bl | ocking Register (INF | PUT_LEAR   | N_BLOCK)                            |     |

|     |      | b16                   | POLEARNDIS          | Port 0 Address       | Learning   |                                     | R/W |

|     |      |                       |                     | Setting              |            | 0: Valid                            |     |

|     |      |                       |                     |                      |            | 1: Invalid                          |     |

|     |      | b17                   | P1LEARNDIS          | Port 1 Address       | Learning   | Sets the address learning of port 1 | R/W |

|     |      |                       |                     | Setting              |            | 0: Valid                            |     |

|     |      |                       |                     |                      |            | 1: Invalid                          |     |

|     |      | b18                   | P2LEARNDIS          | Internal Interface   | Address    | Sets the address learning of the    | R/W |

|     |      |                       |                     | Learning Setting     |            | internal interface port (port 2)    |     |

|     |      |                       |                     |                      |            | 0: Valid                            |     |

|     |      |                       |                     |                      |            | 1: Invalid                          |     |

| 2   | 1448 | [Current              | t description]      |                      |            |                                     |     |

|     |      |                       | 3 Port Timestamp C  | Control/Status Regis | ter (PORTi | n_CTRL) (n = 0, 1)                  |     |

|     |      | b0                    | TSVALID Ti          | mestamp Status       |            | the status of stored timestamp. R/W |     |

|     |      |                       |                     |                      |            | tamp is valid.                      |     |

|     |      |                       |                     |                      |            | tamp is invalid.                    |     |

|     |      |                       |                     |                      |            | o the register (with any value)     |     |

|     |      |                       |                     |                      | clears the | e bit.                              |     |

|     |      | [Correct              | t description]      |                      |            |                                     |     |

|     |      | 29.2.5.3              | 3 Port Timestamp C  | Control/Status Regis |            |                                     |     |

|     |      | b0                    | TSVALID Ti          | mestamp Status       |            | the status of stored timestamp. R/W |     |

|     |      |                       |                     |                      |            | tamp is <b>invalid.</b>             |     |

|     |      |                       |                     |                      |            | tamp is valid.                      |     |

|     |      |                       |                     |                      |            | o the register (with any value)     |     |

|     | 1    |                       |                     |                      | clears the | e bit.                              |     |