# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                        | Document<br>No.         | TN-RZ*-A0101A/E        | Rev.                                                                  | 1.00 |  |  |  |

|-----------------------|------------------------------------------------|-------------------------|------------------------|-----------------------------------------------------------------------|------|--|--|--|

| Title                 | RZ/G1H, G1M, G1N and G1E Document Cor<br>VSP1  | Information<br>Category | Technical Notification |                                                                       |      |  |  |  |

| Applicable<br>Product | RZ/G Series,                                   | Lot No.                 |                        |                                                                       |      |  |  |  |

|                       | RZ/G1H,<br>RZ/G1M,<br>RZ/G1N,<br>RZ/G1E        | All lots                | Reference<br>Document  | RZ/G Series, User's Manual: Hardware<br>Rev.1.00<br>(R01UH0543EJ0100) |      |  |  |  |

| This technica         | I update describes document correction of RZ   | /G Series pr            | oduct.                 |                                                                       |      |  |  |  |

| [Summary]             |                                                |                         |                        |                                                                       |      |  |  |  |

| Document co           | prrection for RZ/G Series, User's Manual: Hard | ware Rev.1.             | 00.                    |                                                                       |      |  |  |  |

| [Priority level       | ]                                              |                         |                        |                                                                       |      |  |  |  |

| Importance: "         | 'Normal"                                       |                         |                        |                                                                       |      |  |  |  |

| Urgency: "No          |                                                |                         |                        |                                                                       |      |  |  |  |

| [Products]            |                                                |                         |                        |                                                                       |      |  |  |  |

| RZ/G1H                |                                                |                         |                        |                                                                       |      |  |  |  |

| RZ/G1M                |                                                |                         |                        |                                                                       |      |  |  |  |

| RZ/G1N                |                                                |                         |                        |                                                                       |      |  |  |  |

| RZ/G1E                |                                                |                         |                        |                                                                       |      |  |  |  |

| [Section num          | ber and title]                                 |                         |                        |                                                                       |      |  |  |  |

| Section 28. VSP1      |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

|                       |                                                |                         |                        |                                                                       |      |  |  |  |

"This is empty adjustment page to compare next Current (from) and Correction (to) on facing page. "

(By using two pages view of PDF readers this enables previously and prospectively view on odd and even pages.)

[Correction]

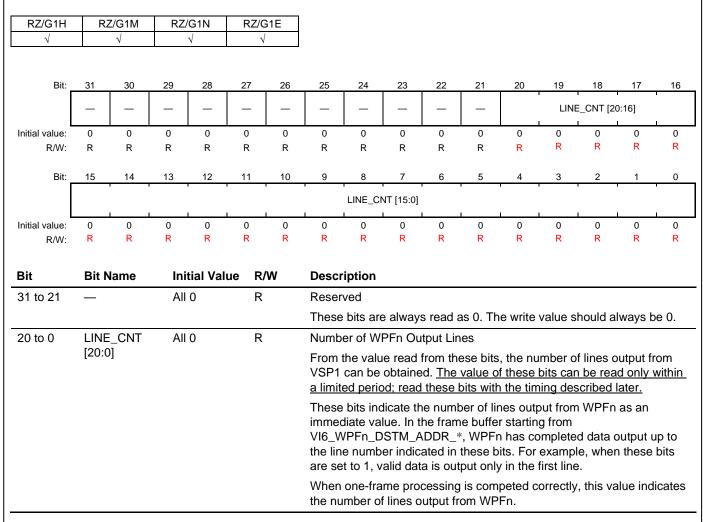

1. Section 28. VSP1, Page 28-54, Section 28.2.5.9 WPFn Output Line Count Register (VI6\_WPFn\_LINE\_CNT: n = 0, 1, 2, 3).

Current (from):

#### 28.2.5.9 WPFn Output Line Count Register (VI6\_WPFn\_LINE\_CNT: n = 0, 1, 2, 3)

Note: See Table 28.15 for details on which RZ/G series products have which registers.

| RZ/G1H                       | R     | Z/G1M | RZ                          | /G1N     | RZ/C  | G1E                                                                                                                                               |                                                                      |         |           |     |     |     |      |          |       |     |

|------------------------------|-------|-------|-----------------------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------|-----------|-----|-----|-----|------|----------|-------|-----|

| √                            |       |       |                             |          |       | 1                                                                                                                                                 |                                                                      |         |           |     |     |     |      |          |       |     |

|                              | 24    | 20    | 00                          | 00       | 07    | 00                                                                                                                                                | 05                                                                   | 0.4     | 00        | 00  | 04  | 00  | 10   | 40       | 47    | 40  |

| Bit:                         | 31    | 30    | 29                          | 28       | 27    | 26                                                                                                                                                | 25                                                                   | 24      | 23        | 22  | 21  | 20  | 19   | 18       | 17    | 16  |

|                              | —     | —     | —                           | -        | -     | —                                                                                                                                                 | —                                                                    | —       | —         | —   | —   |     | LINE | E_CNT [2 | 0:16] | Т   |

| Initial value:               | 0     | 0     | 0                           | 0        | 0     | 0                                                                                                                                                 | 0                                                                    | 0       | 0         | 0   | 0   | 0   | 0    | 0        | 0     | 0   |

| R/W:                         | R     | R     | R                           | R        | R     | R                                                                                                                                                 | R                                                                    | R       | R         | R   | R   | R/W | R/W  | R/W      | R/W   | R/W |

| Bit:                         | 15    | 14    | 13                          | 12       | 11    | 10                                                                                                                                                | 9                                                                    | 8       | 7         | 6   | 5   | 4   | 3    | 2        | 1     | 0   |

|                              |       |       |                             |          |       |                                                                                                                                                   |                                                                      | LINE_CI | NT [15:0] |     |     |     |      |          |       |     |

| Initial value:               | 0     | 0     | 0                           | 0        | 0     | 0                                                                                                                                                 | 0                                                                    | 0       | 0         | 0   | 0   | 0   | 0    | 0        | 0     | 0   |

| R/W:                         | R/W   | R/W   | R/W                         | R/W      | R/W   | R/W                                                                                                                                               | R/W                                                                  | R/W     | R/W       | R/W | R/W | R/W | R/W  | R/W      | R/W   | R/W |

| Bit                          | Bit N | Name  | Ini                         | tial Val | ue R/ | w                                                                                                                                                 | Description                                                          |         |           |     |     |     |      |          |       |     |

| 31 to 21                     |       |       | All                         | 0        | R     |                                                                                                                                                   | Reserved                                                             |         |           |     |     |     |      |          |       |     |

|                              |       |       |                             |          |       |                                                                                                                                                   | These bits are always read as 0. The write value should always be 0. |         |           |     |     |     |      |          |       |     |

| 20 to 0 LINE_CNT All 0 R Num |       | Numb  | Number of WPFn Output Lines |          |       |                                                                                                                                                   |                                                                      |         |           |     |     |     |      |          |       |     |

| [20:0]                       |       |       |                             |          |       | From the value read from these bits, the number of lines output from VSP1 can be obtained. <u>The value of these bits can be read only within</u> |                                                                      |         |           |     |     |     |      |          |       |     |

| the number of lines output from WPFn.                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             |

| The LINE_CNT value is valid only for the period between a frame end interrupt (section 28.2.5.6) and next frame startup     |

| (section 28.2.5.1) or the period between a display list frame end interrupt (section 28.2.5.6) and next frame startup. This |

| register value read outside these periods cannot be used.                                                                   |

a limited period; read these bits with the timing described later. These bits indicate the number of lines output from WPFn as an

VI6\_WPFn\_DSTM\_ADDR\_\*, WPFn has completed data output up to the line number indicated in these bits. For example, when these bits

When one-frame processing is competed correctly, this value indicates

immediate value. In the frame buffer starting from

are set to 1, valid data is output only in the first line.

The LINE\_CNT value depends on the flipping mode (VI6\_WPFn\_OUTFMT.FLP) as shown in Figure 28.15. This correspondence is shown in Table 28.16.

### Table 28.16 VSP1 Output Line Count According to VI6\_WPFn\_OUTFMT.FLP Setting

| VI6_WPFn_OUTFMT.FLP Setting | Corresponding Case Shown in Figure 28.15 |

|-----------------------------|------------------------------------------|

| 0                           | case 1                                   |

| 1                           | case 2                                   |

|                             |                                          |

Correction (to):

# 28.2.5.9 WPFn Output Line Count Register (VI6\_WPFn\_LINE\_CNT: n = 0, 1, 2, 3)

Note: See Table 28.15 for details on which RZ/G series products have which registers.

The LINE\_CNT value is valid only for the period between a frame end interrupt (section 28.2.5.6) and next frame startup (section 28.2.5.1) or the period between a display list frame end interrupt (section 28.2.5.6) and next frame startup. This register value read outside these periods cannot be used.

The LINE\_CNT value depends on the flipping mode (VI6\_WPFn\_OUTFMT.FLP) as shown in Figure 28.15. This correspondence is shown in Table 28.16.

## Table 28.16 VSP1 Output Line Count According to VI6\_WPFn\_OUTFMT.FLP Setting

| VI6_WPFn_OUTFMT.FLP Setting | Corresponding Case Shown in Figure 28.15 |  |  |  |  |  |

|-----------------------------|------------------------------------------|--|--|--|--|--|

| 0                           | case 1                                   |  |  |  |  |  |

| 1                           | case 2                                   |  |  |  |  |  |

|                             |                                          |  |  |  |  |  |

[Description]

Clerical error in Register bit assign table.

[Reason for Correction]

Correction of errors for Register bit assign table.

-----

- End of Document -