## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Aug.03.2005

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan RenesasTechnology Corp.

| Product<br>Category   | MPU&MCU                                                                                               |          | Document<br>No.         | TN-MC*-A014A/E                                                                         | Rev. | 1.00 |

|-----------------------|-------------------------------------------------------------------------------------------------------|----------|-------------------------|----------------------------------------------------------------------------------------|------|------|

| Title                 | Restrictions on dead time of the motor management timer (MMT) in the SH7065 Series and H8S/2612 Group |          | Information<br>Category | Technical Notification                                                                 |      |      |

| Applicable<br>Product | SH7065 Series and H8S/2612 Group                                                                      | Lot No.  |                         | SH7065 Hardware Manual                                                                 |      |      |

|                       |                                                                                                       | All lots | Reference<br>Document   | (ADE-602-166C Rev. 4.0)<br>SH2612 Gruop Hardware Manual<br>(REJ09B0211-0500 Rev. 5.00) |      |      |

|                       |                                                                                                       | All lots |                         |                                                                                        |      |      |

Thank you for your consistent patronage of Renesas semiconductor products.

We would like to inform you of the following restrictions on the dead time of the motor management timer (MMT) in the SH7065 Series and H8S/2612 Group.

#### 1. Phenomenon

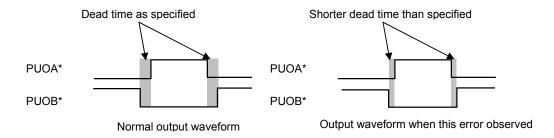

A PWM waveform output may have a shorter dead time (non-overlap time) than the time specified by the timer dead time register (MMT\_TDDR) or may have no dead time (a dead time of 0).

Note: \* The same error is observed for the PVOA and PVOB pins or the PWOA and PWOB pins.

#### 2. Conditions

This error occurs when the counter is restarted (setting the CST bit in TCNR to 1) after the counter is stopped by clearing the CST bit in TCNR to 0 while the MMT repeats count up and count down.

### Date: Aug.03.2005

3. Measures to Handle Error

The following two measures can be used to handle this error.

3.1 Measure A

The CST bit should not be cleared to 0 when the counter is restarted by setting the CST bit to 1. If the CST bit needs to be cleared, the CST bit should not be set to 1 after clearing.

3.2 Measure B

To set the CST bit again after clearing, follow the following procedure.

- Specify the PWM output pin as a general input port by the pin function controller (PFC) for the SH7065 Series and the MMT pin control register (MMTPC) for the H8S/2612 Group.

- 2. Write H'0000 to free-operation addresses of all buffer registers (TBRU, TBRV, and TBRW).

- 3. After the specified dead time has elapsed, write H'00 to TCNR to clear the CST bit to 0.

- 4. Set the CST bit to 1 to restart the counter.