Date: Sep. 24, 2021

# RENESAS TECHNICAL UPDATE

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                  |         | Document<br>No.         | TN-RA*-A0033A/E                                                                                                                                 | Rev.                | 1.00 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|

| Title                 | RA2A1 Group, RA2L1 Group, RA2E1 Group, RA4M1<br>Group, RA4W1 Group, addition of SPI Data Control<br>Register (SPDCR) bit |         | Information<br>Category | Technical Notification                                                                                                                          |                     |      |

|                       |                                                                                                                          | Lot No. |                         | RA2A1 Group User's Manual<br>Hardware Rev.1.00                                                                                                  |                     |      |

| Applicable<br>Product | RA2A1 Group<br>RA2L1 Group<br>RA2E1 Group<br>RA4M1 Group<br>RA4W1 Group                                                  | All     | Reference<br>Document   | RA2L1 Group User's Hardware Rev.1.10 RA2E1 Group User's Hardware Rev.1.10 RA4M1 Group User Hardware Rev.1.00 RA4W1 Group User Hardware Rev.1.00 | s Manua<br>'s Manua | al   |

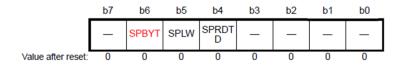

The SPBYT bit of SPI Data Control Register (SPDCR) is added.

[before] example: RA2A1

# SPI Data Control Register (SPDCR)

Address(es): SPI0.SPDCR 4007 200Bh, SPI1.SPDCR 4007 210Bh

| Bit Symbol |        | Bit name                                         | Description                                                                                                                                            |  |

|------------|--------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| b3 to b0   | _      | Reserved                                         | These bits are read as 0. The write value should be 0.                                                                                                 |  |

| b4         | SPRDTD | SPI Receive/Transmit Data<br>Select              | Read SPDR/SPDR_HA values from the receive buffer     Read SPDR/SPDR_HA values from the transmit buffer     (but only if the transmit buffer is empty). |  |

| b5         | SPLW   | SPI Word Access/Halfword<br>Access Specification | Set SPDR_HA to valid for halfword access     Set SPDR to valid for word access.                                                                        |  |

| b7, b6     | _      | Reserved                                         | These bits are read as 0. The write value should be 0.                                                                                                 |  |

## SPRDTD bit (SPI Receive/Transmit Data Select)

The SPRDTD bit selects whether the SPDR/SPDR\_HA register reads values from the receive buffer or from the transmit buffer. If reading is from the transmit buffer, the last value written to the SPDR/SPDR\_HA register is read. Reading the transmit buffer must be done after generation of the transmit buffer empty interrupt (SPSR.SPTEF is 1).

For details, see section 30.2.5, SPI Data Register (SPDR/SPDR\_HA).

#### SPLW bit (SPI Word Access/Halfword Access Specification)

The SPLW bit specifies the access width for the SPDR register. Access to SPDR\_HA in halfwords is valid when the SPLW bit is 0 and access to the SPDR register in words is valid when the SPLW bit is 1. In addition, when the SPLW bit is 0, set the SPI data length setting bits, SPCMD0.SPB[3:0], from 8 to 16 bits. Do not perform any operations when a data length of 20, 24, or 32 bits is specified.

#### [after]

## SPI Data Control Register (SPDCR)

Address(es): SPI0.SPDCR 4007 200Bh, SPI1.SPDCR 4007 210Bh

| Bit      | Symbol | Bit name                                         | Description                                                                                                                               | R/W |

|----------|--------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b3 to b0 | _      | Reserved                                         | These bits are read as 0. The write value should be 0.                                                                                    |     |

| b4       | SPRDTD | SPI Receive/Transmit Data<br>Select              | Read SPDR/SPDR_HA values from receive buffer     Read SPDR/SPDR_HA values from transmit buffer, but only if the transmit buffer is empty. |     |

| b5       | SPLW   | SPI Word Access/Halfword<br>Access Specification | Set SPDR_HA to valid for halfword access     Set SPDR to valid for word access.                                                           |     |

| b6       | SPBYT  | SPI Byte Access Specification                    | 0: SPDR is accessed in halfword or word (SPLW is valid) 1: SPDR is accessed in byte (SPLW is invalid).                                    |     |

| b7       | _      | Reserved                                         | This bit is read as 0. The write value should be 0.                                                                                       | R/W |

## SPRDTD bit (SPI Receive/Transmit Data Select)

The SPRDTD bit selects whether the SPDR/SPDR\_HA register reads values from the receive buffer or from the transmit buffer. If reading is from the transmit buffer, the last value written to the SPDR/SPDR\_HA register is read. Reading the transmit buffer must be done after generation of the transmit buffer empty interrupt (SPSR.SPTEF is 1).

For details, see section of SPI Data Register (SPDR/SPDR HA).

#### SPLW bit (SPI Word Access/Halfword Access Specification)

The SPLW bit specifies the access width for the SPDR register. Access to SPDR\_HA in halfwords is valid when the SPLW bit is 0 and access to the SPDR register in words is valid when the SPLW bit is 1. In addition, when the SPLW bit is 0, set the SPI data length setting bits, SPCMD0.SPB[3:0], from 8 to 16 bits. Do not perform any operations when a data length of 20, 24, or 32 bits is specified.

# **SPBYT bit (SPI Byte Access Specification)**

This bit is used to set the data width of access to the SPI Data Register (SPDR). When SPBYT = 0, use word or half word access to SPDR. When SPBYT = 1 (in that case, SPLW is invalid), use byte access to SPDR. When SPBYT = 1, set the SPI data length bits (SPB[3:0]) in the SPI Command Register n (SPCMDn) to 8 bits. If SPB[3:0] are set to 9 to 16, 20, 24, or 32 bit, subsequent operation is not guaranteed.