**Customer Notification**

# **µPD78F9212 Subseries**

**8-Bit Single-Chip Microcontrollers**

**Operating Precautions**

μPD78F9210 μPD78F9211 μPD78F9212

Document No. U18767EE1V0IF00 Date Published May 2007

© NEC Electronics (Europe) GmbH

### DISCLAIMER

The related documents in this customer notification may include preliminary versions. However, preliminary versions may not have been marked as such.

The information in this customer notification is current as of its date of publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC PRODUCT(S). Not all PRODUCT(S) and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

No part of this customer notification may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this customer notification. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC PRODUCT(S) listed in this customer notification or any other liability arising from the use of such PRODUCT(S).

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this customer notification are provided for illustrative purposes of PRODUCT(S) operation and/or application examples only. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

While wherever feasible, NEC endeavors to enhance the quality, reliability and safe operation of PRODUCT(S) the customer agree and acknowledge that the possibility of defects and/or erroneous thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects and/or errors in PRODUCT(S) the customer must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

The customer agrees to indemnify NEC against and hold NEC harmless from any and all consequences of any and all claims, suits, actions or demands asserted against NEC made by a third party for damages caused by one or more of the items listed in the enclosed table of content of this customer notification for PRODUCT(S) supplied after the date of publication.

#### Applicable Law:

The law of the Federal Republic of Germany applies to all information provided by NEC to the Customer under this Operating Precaution document without the possibility of recourse to the Conflicts Law or the law of 5th July 1989 relating to the UN Convention on Contracts for the International Sale of Goods (the Vienna CISG agreement).

Düsseldorf is the court of jurisdiction for all legal disputes arising directly or indirectly from this information. NEC is also entitled to make a claim against the Customer at his general court of jurisdiction.

If the supplied goods/information are subject to German, European and/or North American export controls, the Customer shall comply with the relevant export control regulations in the event that the goods are exported and/or re-exported. If deliveries are exported without payment of duty at the request of the Customer, the Customer accepts liability for any subsequent customs administration claims with respect to NEC.

**Notes:** (1) "**NEC**" as used in this statement means NEC Corporation and also includes its direct or indirect owned or controlled subsidiaries.

(2) "**PRODUCT(S)**" means 'NEC semiconductor products' (*NEC semiconductor products* means any semiconductor product developed or manufactured by or for NEC) and/or 'TOOLS' (*TOOLS* means 'hardware and/or software development tools' for NEC semiconductor products' developed, manufactured and supplied by 'NEC' and/or 'hardware and/or software development tools' supplied by NEC but developed and/or manufactured by independent 3<sup>rd</sup> Party vendors worldwide as their own product or on contract from NEC)

## **Table of Contents**

| (A) | Table of Operating Precautions       | 4 |

|-----|--------------------------------------|---|

| (B) | Description of Operating Precautions | 5 |

| (C) | Valid Specification                  | 7 |

| (D) | Revision History                     | 8 |

µPD78F9212 Subseries

## (A) Table of Operating Precautions

|     |                                                        |           | µPD78F921x         |         |

|-----|--------------------------------------------------------|-----------|--------------------|---------|

| No. | Outline                                                | Rev. Note | V1.2               |         |

|     |                                                        | Rank      | K <sup>Note1</sup> | E Note2 |

| 1   | Restriction for STOP mode<br>(Technical Limitation)    | x         | 1                  |         |

| 2   | Restriction on using flash self-<br>(Direction of use) | x         | X                  |         |

| 3   |                                                        |           |                    |         |

✓: Not applicable

X: applicable

Note: - The version is indicated by the in the lot number, marked on each product.

Pls refer to the below marking on each package

Older device versions are not part of this customer notification anymore because it is expected that they are not used anymore.

- **Note1**: Products with rank K are produced before week 20, 2005 (519 or earlier in the last line of the marking).

- **Note2**: Products with rank E are produced from week 20, 2005 onwards (520 or later in the last line of the marking).

## Marking for non A grade products

M: ROM Size (0:1K; 1:2K; 2:4k) ###: Code Number (if preprogrammed) or Flash Grade N: last digit of Year Code WW: week Code

| μP | D78F921x           |         |

|----|--------------------|---------|

|    | Revision /<br>Rank | Marking |

|    | V 1.2 Rank         | Y1M     |

|    | "K"                | ###     |

|    |                    | 519     |

|    | Rank "E"           | Y1M     |

|    |                    | ###     |

|    |                    | 520     |

Marking for A grade products

X: ROM Size (0:1K; 1:2K; 2:4k) N: last digit of Year Code WW: week Code

yyy: in house code

## (B) Description of Operating Precautions

| o. 1 | Restriction for STOP mode<br>(Technical Limitation)                                                                                                                                                |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|      | Details                                                                                                                                                                                            |  |  |  |  |

|      | When CPU execute STOP instruction with IE flag = 0 (DI instruction executed) and IF flag = 1                                                                                                       |  |  |  |  |

|      | that is not masked, STOP mode will not be released.                                                                                                                                                |  |  |  |  |

|      | Then any other interrupts are occurred, STOP mode is not released, either.                                                                                                                         |  |  |  |  |

|      |                                                                                                                                                                                                    |  |  |  |  |

|      | Case 1 : When CPU execute STOP instruction with IE flag = 0 and IF flag = 1, MK flag = 0.                                                                                                          |  |  |  |  |

|      | DI ; Interrupt is disabled                                                                                                                                                                         |  |  |  |  |

|      | SET1 PIF0 ; Set interrupt request flag(INTP0)                                                                                                                                                      |  |  |  |  |

|      | CLR1 PMK0 ; Clear interrupt mask flag(INTP0)                                                                                                                                                       |  |  |  |  |

|      | SET1 P2.0 ; Set Port20 to "1"<br>STOP ; Changing STOP mode                                                                                                                                         |  |  |  |  |

|      | STOP ; Changing STOP mode<br>CLR1 P2.0 ; Clear Port20(Will not be executed)                                                                                                                        |  |  |  |  |

|      |                                                                                                                                                                                                    |  |  |  |  |

|      | When interrupt enabled and standby release signal is occurred, and CPU execute interrupt request pending instruction right before STOP instruction executing, then STOP mode will not be released. |  |  |  |  |

|      | Case2 : When CPU execute STOP instruction with IE flag = 1 and IF flag = 1, MK flag = 0.                                                                                                           |  |  |  |  |

|      | El ; Interrupt is enabled                                                                                                                                                                          |  |  |  |  |

|      | SET1 P2.0 ; Set Port20 to "1"                                                                                                                                                                      |  |  |  |  |

|      | SET1 PIF0 ; Set interrupt request flag(INTP0)                                                                                                                                                      |  |  |  |  |

|      | CLR1 PMK0 ; Executing interrupt request pending instruction                                                                                                                                        |  |  |  |  |

|      | STOP ; Changing STOP mode                                                                                                                                                                          |  |  |  |  |

|      | CLR1 P2.0 ; Clear Port20(Never executed)                                                                                                                                                           |  |  |  |  |

|      | Note : interrupt request pending instruction                                                                                                                                                       |  |  |  |  |

|      | Write access instruction for interrupt request flag register 0 (IF0)                                                                                                                               |  |  |  |  |

|      | Write access instruction for interrupt mask flag register 0 (MK0)                                                                                                                                  |  |  |  |  |

|      | <u>Workaround</u><br>Execute El instruction before STOP instruction execution. Then do not execute Interrupt request                                                                               |  |  |  |  |

|      | pending instruction right before STOP execution.                                                                                                                                                   |  |  |  |  |

|      | Case3 : Executing EI instruction right before STOP instruction.                                                                                                                                    |  |  |  |  |

|      | DI ; Interrupt disabled                                                                                                                                                                            |  |  |  |  |

|      | SET1 PIF0 ; Set interrupt request flag(INTP0)                                                                                                                                                      |  |  |  |  |

|      | CLR1 PMK0 ; Clear interrupt mask flag(INTP0)                                                                                                                                                       |  |  |  |  |

|      | SET1 P2.0 ; Set Port20 to "1".                                                                                                                                                                     |  |  |  |  |

|      | El ; Interrupt enabled                                                                                                                                                                             |  |  |  |  |

|      | STOP ; Changing STOP mode                                                                                                                                                                          |  |  |  |  |

|      | CLR1 P2.0 ; Clear Port20(will execute)                                                                                                                                                             |  |  |  |  |

|      | Note:                                                                                                                                                                                              |  |  |  |  |

|      | If interrupt is occurred before executing STOP instruction, it's necessary to generate interrupt for                                                                                               |  |  |  |  |

|      | releasing from STOP mode because interrupt request flag is cleared before executing STOP                                                                                                           |  |  |  |  |

|      | instruction.                                                                                                                                                                                       |  |  |  |  |

|      |                                                                                                                                                                                                    |  |  |  |  |

| No. 2 | Restriction on us<br>(Direction of use)                                                                                                                                                                                                                                                                                                                          |             | self-pro | grammin    | g           |         |               |            |               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|------------|-------------|---------|---------------|------------|---------------|

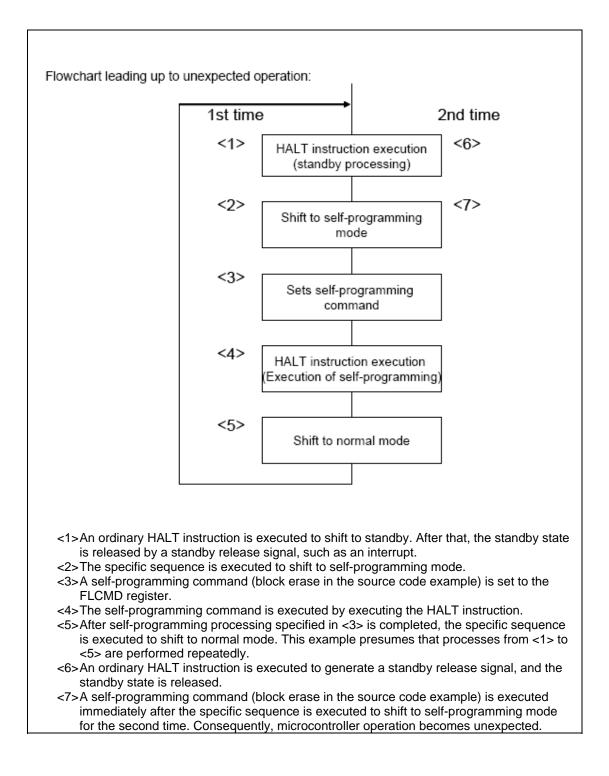

|       | <u>Details</u><br>If the standby function performed by the HALT instruction and flash self-programming are used together using the procedure shown below, the subsequent operation becomes unexpected.                                                                                                                                                           |             |          |            |             |         |               |            |               |

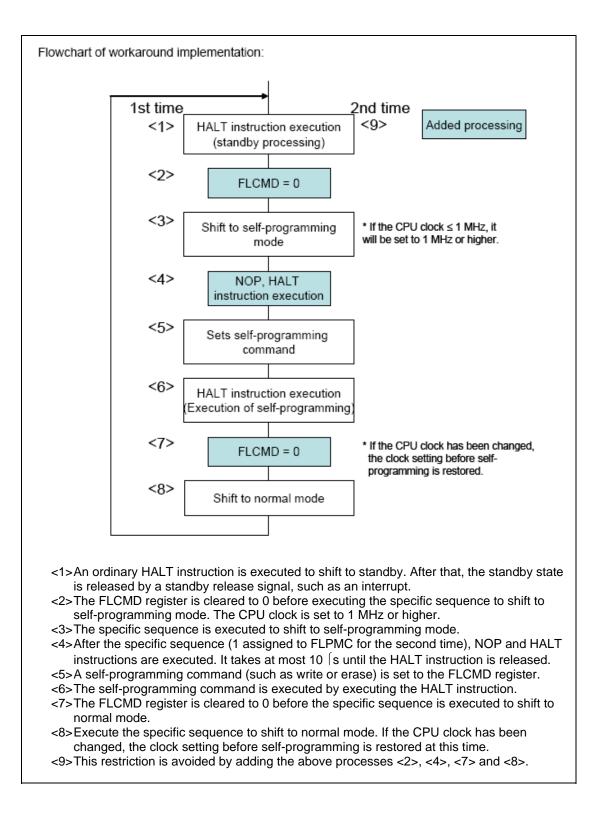

|       | <u>Workaround</u><br>When using flash self-programming, clear the FLCMD register to 0 immediately before shifting to<br>normal mode or self-programming mode. In addition, execute NOP and HALT instructions after<br>specific sequence processing to shift to self-programming mode.                                                                            |             |          |            |             |         |               |            |               |

|       | <u>Detailed explana</u>                                                                                                                                                                                                                                                                                                                                          | <u>tion</u> |          |            |             |         |               |            |               |

|       | The following two                                                                                                                                                                                                                                                                                                                                                | o modes a   | are avai | lable in t | hese produc | cts.    |               |            |               |

|       |                                                                                                                                                                                                                                                                                                                                                                  |             |          |            |             | ed. Ope | ration enters | s into a s | standby state |

|       | <ul> <li>Self-programming mode:<br/>The state in which self-programming commands are executable. After setting<br/>commands,addresses and write data and executing the HALT instruction, self-<br/>programming is executed. The specific sequence described in this document is referring<br/>to the register manipulation to switch these two modes.</li> </ul> |             |          |            | self-       |         |               |            |               |

|       | Process Leading up to Unexpected Operation                                                                                                                                                                                                                                                                                                                       |             |          |            |             |         |               |            |               |

|       |                                                                                                                                                                                                                                                                                                                                                                  | execution   |          | setting    | execution   | SELF    | execution     | SELF       | operation     |

|       | HALT                                                                                                                                                                                                                                                                                                                                                             |             |          |            |             |         |               |            |               |

|       | HALT                                                                                                                                                                                                                                                                                                                                                             | <1>         |          |            | <3>         |         | <5>           |            |               |

|       | execution flag                                                                                                                                                                                                                                                                                                                                                   |             |          |            |             |         |               |            |               |

|       | FLSPM                                                                                                                                                                                                                                                                                                                                                            |             | <2>      |            |             |         | <4>           |            |               |

|       | SELF execution<br>status                                                                                                                                                                                                                                                                                                                                         |             |          |            |             |         |               | <6>        |               |

|       | FLCMD<br>register value                                                                                                                                                                                                                                                                                                                                          | 00H         |          |            |             | Апу со  | mmand value   |            |               |

|       |                                                                                                                                                                                                                                                                                                                                                                  |             |          |            |             |         |               |            |               |

- <1>An ordinary HALT instruction is executed and the internal HALT execution flag is set. Self-programming is executed by setting the FLSPM bit while the HALT execution flag is set.

- <2>The specific sequence is executed and the operation then enters into self-programming mode. At this time, the FLSPM bit changes to indicate that self-programming is now executable. However, self-programming commands are not executed at this time, because the FLCMD register has been initialized to 00H.

- <3>Once a command value is set to the FLCMD register and the HALT instruction is executed, the self-programming command is executed. The HALT execution flag is cleared just as the self-programming command is executed.

- <4>Execution of the self-programming command is completed, the specific sequence is executed again, and operation enters into normal mode.

- <5>The HALT instruction is executed again, operation enters into standby, and the HALT execution flag is set.

- <6>After the standby state is released, the specific sequence is executed to shift to self-programming mode. If the command value set to the FLCMD register has not been initialized at this time, the command still set to the FLCMD register is reexecuted when the FLSPM bit is set. Self-programming is subsequently executed during CPU operation and the CPU fetches an incorrect instruction from the flash memory, resulting in an unexpected operation.

**Remark** The same situation occurs when flash self-programming is executed before <1>.

#### Workaround:

When using flash self-programming, clear the FLCMD register to 0 immediately before shifting to normal mode or self-programming mode; this prevents execution of illegal commands immediately after the mode is shifted. In addition, execute NOP and HALT instructions after specific sequence processing to shift to self-programming mode; this controls the execution timing between the CPU and the flash memory control block.

The flowcharts and source code examples for the operation restriction and its workaround implementation are described on the following pages.

| Examp     | Example source code causing unexpected operation (assembly language):                             |                                        |                                                                                                                 |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAINLOOP: |                                                                                                   |                                        |                                                                                                                 |  |  |  |  |

|           | ; Executes HALT to shift to standby state - <1> and <6> in flowchart<br>HALT                      |                                        |                                                                                                                 |  |  |  |  |

|           | ; Saves the interrupt mask setting before executing self-programming.<br>DI ; Disables interrupts |                                        |                                                                                                                 |  |  |  |  |

|           | MOV<br>XCH                                                                                        | A,MK0<br>A.X                           | ; Saves interrupt mask setting                                                                                  |  |  |  |  |

|           | MOV<br>PUSH                                                                                       | A,MK1                                  | ; Saves only MK0 in KU1+ and KY1+                                                                               |  |  |  |  |

|           | MOV<br>MOV                                                                                        | MK0,#0FFH<br>MK1,#0FFH                 |                                                                                                                 |  |  |  |  |

| ModeO     |                                                                                                   | tes the specific se                    | quence to shift to self-programming mode - <2> and <7> in flowchart                                             |  |  |  |  |

| Wouldo    | MOV                                                                                               |                                        | ; Controls PFCMD register                                                                                       |  |  |  |  |

|           | MOV<br>MOV                                                                                        | FLPMC,#01H<br>FLPMC,#0FEH              | ; Controls FLPMC register (set value)<br>; Controls FLPMC register (inverted set value)                         |  |  |  |  |

|           | MOV                                                                                               | FLPMC,#01H                             | ; Sets self-programming mode<br>rated by an external resonator or external input clock insert a 16 us wait.     |  |  |  |  |

|           |                                                                                                   | 5 5                                    |                                                                                                                 |  |  |  |  |

|           | <mark>; Opera</mark><br>BT                                                                        | tion becomes unex<br>PFS.0,\$ModeOn    | kpected when entered into self-programming mode for the second time. Loop ; Confirms completion of mode shift   |  |  |  |  |

|           |                                                                                                   |                                        |                                                                                                                 |  |  |  |  |

|           | ; Perfor<br>MOV                                                                                   | ms command setti<br>A, #0FH            | ngs - <3> in flowchart                                                                                          |  |  |  |  |

|           | MOV                                                                                               | FLAPH,A                                | ; Sets number of block to be erased                                                                             |  |  |  |  |

|           | MOV<br>MOV                                                                                        | FLAPHC,A<br>FLCMD,#03H                 | ; Sets compare number for block to be erased (value set to FLAPH)<br>; Sets flash control command (block erase) |  |  |  |  |

|           | MOV                                                                                               | PFS,#00H                               | ; Clears flash status register                                                                                  |  |  |  |  |

|           | MOV                                                                                               | WDTE,#0ACH                             | ; Clears and starts WDT                                                                                         |  |  |  |  |

|           | ,                                                                                                 | tes erase comman<br>Executes self-prog | nd - <4> in flowchart<br>gramming                                                                               |  |  |  |  |

| ModeO     |                                                                                                   | tes the specific se                    | quence to shift to normal mode - <5> in flowchart                                                               |  |  |  |  |

|           | MOV                                                                                               | PFS,#00H                               |                                                                                                                 |  |  |  |  |

|           | MOV<br>MOV                                                                                        | PFCMD,#0A5H<br>FLPMC,#00H              | ; Controls PFCMD register<br>; Controls FLPMC register (set value)                                              |  |  |  |  |

|           | MOV                                                                                               | FLPMC,#0FFH                            | ; Controls FLPMC register (inverted set value)                                                                  |  |  |  |  |

|           | MOV<br>BT                                                                                         | FLPMC,#00H<br>PFS.0,\$ModeOff          | ; Sets normal mode<br>Loop : Confirms completion of mode shift                                                  |  |  |  |  |

|           | POP                                                                                               | AX                                     | ; Restores interrupt mask setting                                                                               |  |  |  |  |

|           | MOV                                                                                               | MK1,X                                  |                                                                                                                 |  |  |  |  |

|           | XCH<br>MOV                                                                                        | A,X<br>MK0,A                           |                                                                                                                 |  |  |  |  |

|           | BR                                                                                                | MAINLOOP                               |                                                                                                                 |  |  |  |  |

|           |                                                                                                   |                                        |                                                                                                                 |  |  |  |  |

```

Example source code causing unexpected operation (C language):

while(1){

/* Executes HALT to shift to standby state - <1> and <6> in flowchart */

HALT();

/* Saves interrupt mask settings */

DI():

// Disables interrupts

ch_mask_bak0 = MK0;

// Saves only MK0 in KU1+ and KY1+

ch_mask_bak1 = MK1;

// ch_mask_bak0/1 are variables for saving

/* Shifts to self-programming mode - <2> and <7> in flowchart */

do{

PFS = 0;

// Clears flash status register

PFCMD = 0xA5:

// Controls PFCMD register

FLPMC = 0x01;

// Controls FLPMC register (set value)

FLPMC = 0xFE;

// Controls FLPMC register (inverted set value)

FLPMC = 0x01;

// Sets self-programming mode

/* When using a clock generated by an external resonator or external input clock,

insert a 16 s wait.*/

Operation becomes unexpected when entered into self-programming mo

or the second time. */

while(PFS.0 == 1);

// Confirms completion of mode shift

/* Performs command settings - <3> in flowchart */

FLAPH = FLAPHC = 0x0F;

// Specifies block to be erased

FLCMD = 0x03:

// Specifies erase command

PFS = 0x00;

// Clears flash status register

WDTE = 0xAC;

// Clears WDT counter

/* Executes erase command - <4> in flowchart */

// Executes erase command

HALT();

/* Shifts to normal mode - <5> in flowchart */

do{

PFS = 0:

// Clears flash status register

PFCMD = 0xA5:

// Controls PFCMD register

FLPMC = 0x00;

// Controls FLPMC register (set value)

// Controls FLPMC register (inverted set value)

FLPMC = 0xFF;

FLPMC = 0x00;

// Sets normal mode

while(PFS.0 == 1);

// Confirms completion of mode shift

/* Restores interrupt mask settings */

MK0 = ch_mask_bak0;

MK1 = ch_mask_bak1;

}

```

| Examp   | ble of source code to which workaround is implemented (assembly language):                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

| MAINLC  | DOP:                                                                                                                        |

|         | ; Executes HALT to shift to standby state - <1> and <9> in flowchart HALT                                                   |

|         | ; Saves the interrupt mask setting before executing self-programming.<br>DI ; Disables interrupts                           |

|         | MOV A,MK0 ; Saves interrupt mask setting<br>XCH A.X                                                                         |

|         | MOV A,MK1 ; Saves only MK0 in KU1+ and KY1+<br>PUSH AX                                                                      |

|         | MOV MK0, #0FFH<br>MOV MK1, #0FFH                                                                                            |

|         | ; Initializes FLCMD register - <2> in flowchart<br>MOV FLCMD, #00H                                                          |

|         | ; If CPU clock $\delta$ 1 MHz, sets CPU clock to 1 MHz or higher.                                                           |

| ModeOr  | ; Executes the specific sequence to shift to self-programming mode - <3> in flowchart                                       |

| incucer | MOV PFCMD,#0A5H ; Controls PFCMD register<br>MOV FLPMC,#01H ; Controls FLPMC register (set value)                           |

|         | MOV FLPMC,#0FEH ; Controls FLPMC register (inverted set value)                                                              |

|         | MOV FLPMC,#01H ; Sets self-programming mode<br>BT PFS.0,\$ModeOnLoop ; Confirms completion of mode shift                    |

|         | : Executes NOP and HALT instructions - <4> in flowchart<br>NOP<br>HALT                                                      |

|         | When using a clock generated by an external resonator or external input clock, insert an 8us wait.                          |

|         | ; Performs command settings - <5> in flowchart<br>MOV A, #0FH                                                               |

|         | MOV FLAPH,A; Sets number of block to be erasedMOV FLAPHC,A; Sets compare number for block to be erased (value set to FLAPH) |

|         | MOV FLCMD,#03H ; Sets flash control command (block erase)<br>MOV PFS,#00H ; Clears flash status register                    |

|         | MOV WDTE,#0ACH ; Clears and starts WDT<br>; Executes erase command - <6> in flowchart                                       |

|         | HALT ; Executes self-programming                                                                                            |

|         | ; Initializes FLCMD register - <7> in flowchart<br>MOV FLCMD, #00H                                                          |

|         | . If the CPU clock has been changed, the setting before self-programming is restored.                                       |

| ModeOf  | ; Executes the specific sequence to shift to normal mode - <8> in flowchart<br>fLoop:<br>MOV PFS.#00H                       |

|         | MOV FC/MD,#0A5H ; Controls PFCMD register<br>MOV FLPMC,#00H ; Controls FLPMC register (set value)                           |

|         | MOV FLPMC,#0FFH ; Controls FLPMC register (inverted set value)<br>MOV FLPMC,#00H ; Sets normal mode                         |

|         | BT PFS.0,\$ModeOffLoop ; Confirms completion of mode shift                                                                  |

|         | POP AX ; Restores interrupt mask setting<br>MOV MK1,X                                                                       |

|         | XCH A,X                                                                                                                     |

|         | MOV MK0,A<br>BR MAINLOOP                                                                                                    |

| Example of source code to which workaround is implemented (C language):                                                                                                                                                                       |   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| while(1){<br>/* Executes HALT to shift to standby state - <1> and <9> in flowchart */<br>HALT();                                                                                                                                              |   |  |  |  |  |

| /* Saves interrupt mask settings */<br>DI(); // Disables interrupts<br>ch_mask_bak0 = MK0; // Saves only MK0 in KU1+ and KY1+<br>ch_mask_bak1 = MK1; // ch_mask_bak0/1 are variables for saving                                               |   |  |  |  |  |

| /* Initializes FLCMD register - <2> in flowchart */<br>FLCMD = 0;<br>/* If CPU clock δ 1 MHz, sets CPU clock to 1 MHz or higher */                                                                                                            |   |  |  |  |  |

| /* Enters into self-programming mode - <3> in flowchart */<br>do{<br>PFS = 0; // Clears flash status register<br>PFCMD = 0xA5; // Controls PFCMD register<br>FLPMC = 0x01; // Controls FLPMC register (set value)                             |   |  |  |  |  |

| FLPMC = 0xFE; // Controls FLPMC register (inverted set value)<br>FLPMC = 0x01; // Sets self-programming mode<br>}while(PFS.0 == 1); // Confirms completion of mode shift                                                                      |   |  |  |  |  |

| /* Executes NOP and HALT instructions - <4> in flowchart */<br>NOP():<br>HALT();<br>/* When using a clock generated by an ext. resonator or external input clock, insert an 8us wait.*/                                                       | / |  |  |  |  |

| /* Performs command settings - <5> in flowchart */<br>FLAPH = FLAPHC = 0x0F; // Specifies block to be erased<br>FLCMD = 0x03; // Specifies erase command<br>PFS = 0x00; // Clears flash status register<br>WDTE = 0xAC; // Clears WDT counter |   |  |  |  |  |

| /* Executes erase command - <6> in flowchart */<br>HALT(); // Executes erase command                                                                                                                                                          |   |  |  |  |  |

| /* Initializes FLCMD register - <7> in flowchart */<br>FLCMD = 0;                                                                                                                                                                             |   |  |  |  |  |

| <pre>/* If the CPU clock has been changed, the setting before self-programming is restored. */ /* Shifts to normal mode - &lt;8&gt; in flowchart */ do{</pre>                                                                                 |   |  |  |  |  |

| <pre>}while(PFS.0 == 1); // Confirms completion of mode shift /* Restores interrupt mask settings */ MK0 = ch_mask_bak0; MK1 = ch_mask_bak1; }</pre>                                                                                          |   |  |  |  |  |

# (C) Valid Specification

| ltem | Date published    | Document No. | Document Title |  |

|------|-------------------|--------------|----------------|--|

| 1    | Dez 2006 or later | U16994       | User's Manual  |  |

|      |                   |              |                |  |

|      |                   |              |                |  |

|      |                   |              |                |  |

# (D) Revision History

| ltem | Date published   | Document No.      | Comment                                                                                 |

|------|------------------|-------------------|-----------------------------------------------------------------------------------------|

| 1    | January 17, 2005 | TPS-LE-OP-F9212-1 | 1 <sup>st</sup> Release                                                                 |

| 2    | March 23, 2005   | TPS-LE-OP-F9212-2 | 2 <sup>nd</sup> Release, addition of item 5                                             |

| 3    | March 24, 2006   | TPS-LE-OP-F9212-3 | 3 <sup>rd</sup> Release, addition of Rank "E"                                           |

| 4    | May, 2007        | U18767EE1V0IF00   | 4 <sup>th</sup> Release, addition of restriction 2, removal of old versions, new doc no |