Date: Jun. 2, 2010

## RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                    |          | Document<br>No.         | TN-SH7-A770A/E                                    | Rev. | 1.00 |

|-----------------------|------------------------------------------------------------|----------|-------------------------|---------------------------------------------------|------|------|

| Title                 | Notes on Usage of the Watchdog Timer in SH7216<br>Products |          | Information<br>Category | Technical Notification                            |      |      |

| Applicable<br>Product | SH7216 Group<br>SH7214 Group                               | Lot No.  |                         | SH7216 Group Hardware Manual<br>(REJ09B0543-0101) |      |      |

|                       |                                                            | All lots | Reference<br>Document   |                                                   |      |      |

The watchdog timer in the applicable products indicated above fails under certain conditions. This update describes the details of the failure, notes on usage to avoid the failure, and countermeasures.

## 1. Details of the Failure

- 1.1 If the following conditions 1 to 4 are all satisfied in the on-chip watchdog timer of a SH7216 product, the CPU may crash instead of execution branching to power-on reset processing.

- 1. Watchdog timer mode is selected (WT/IT = 1).

- 2. The power-on reset is selected as the internal reset on an overflow of WTCNT (RSTS = 0).

- 3. On-chip ROM enabled mode (MCU extension mode 2, single chip mode) is selected.

- 4. The frequency of the Iφ clock for use by the CPU is greater than 100 MHz.

Note that the signal from the WDTOVF pin will be output normally regardless of the above conditions.

- 1.2 When at least one of the following conditions is satisfied, the CPU operates normally instead of crashing as described above.

- 1. The interval timer mode is in use (WT/IT = 0).

- 2. The manual reset is selected as the internal reset on an overflow of WTCNT (RSTS = 1) in watchdog timer mode

- 3. An on-chip ROM disabled mode (MCU extension mode 0 or 1) is selected.

- 4. The frequency of the  $I\phi$  clock for use by the CPU is 100 MHz or less.

## 2. Countermeasure for the Failure

[Temporary Countermeasure]

Please implement the following countermeasure for the failure in software.

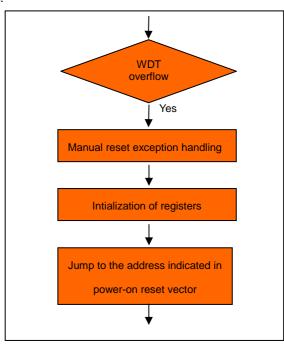

Figure 1 shows the procedure of the countermeasure.

Select the manual reset as the type of reset in response to an overflow of the watchdog timer.

$\downarrow$

After an overflow occurs, initialize the registers of modules that are in use from within the exception handler for the manual reset. The following is an example of processing for initialization.

- 1. Change settings for all pins to the initial values as input port pins.

- For peripheral modules (MTU2, etc.) which are initialized by being placed on module standby, place them on module standby and then release them.

- For peripheral functions which are not initialized by being placed on module standby, initialize them as possible (set them to the same values as after a power-on reset).

$\downarrow$

Make execution jump to the address indicated by the power-on reset vector.

Figure 1 Countermeasure by Software

[Permanent Countermeasure]

We are planning a revision to eliminate the failure by September of 2010.