## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU&MCU                                              | Document<br>No. | TN-SH7-A543A/E          | Rev.                                                  | 1.0 |  |

|-----------------------|------------------------------------------------------|-----------------|-------------------------|-------------------------------------------------------|-----|--|

| Title                 | Limitation for use of SH7710 internal Ethernet DMAC. |                 | Information<br>Category | Technical Notification                                |     |  |

| Applicable<br>Product | HD6417710<br>HD6417712<br>R4J7710ABG                 | Lot No.         |                         |                                                       |     |  |

|                       |                                                      | ALL             | Reference<br>Document   | SH7710 Hardware manual<br>REJ09B0079-0100Z<br>Rev.1.0 |     |  |

There is a limitation for use of Ethernet Direct Memory Access Controller (E-DMAC) in SH7710, and the countermeasures are shown below.

[Phenomenon]

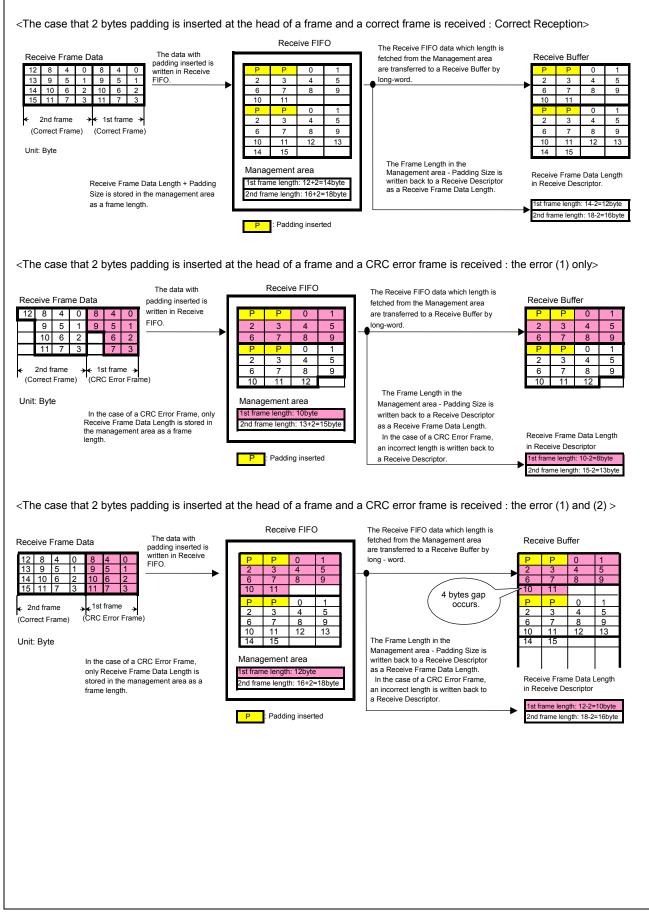

When a CRC error occurs in the case the receiving data padding insertion function is set enabled,

the E-DMAC writes back an incorrect receive frame length, which is the inserted padding bytes short of the correct length, to a Receive Descriptor.

The error (1) above is also the cause that the last 4 bytes data of the CRC error frame may not be transferred from Receive FIFO to Receive Buffer after CRC error frame reception.

In this case the remained last 4 bytes data is transferred to Receive Buffer as the first 4 bytes of the following receive frame. Therefore, the receive frame data after the CRC error frame are stored in Receive Buffer with 4 bytes gap. Whether this 4 bytes gap occurs or not depends on the padding size and the byte number of remainder when dividing a receive frame data length by 4 as a table below.

|              |        | The byte number of remainder when dividing a receive frame data length by 4 |          |          |        |  |  |

|--------------|--------|-----------------------------------------------------------------------------|----------|----------|--------|--|--|

|              |        | 0 byte                                                                      | 1 byte   | 2 byte   | 3 byte |  |  |

| Padding size | 0 byte | 0                                                                           | 0        | 0        | 0      |  |  |

|              | 1 byte | ×                                                                           | $\Delta$ | Δ        | Δ      |  |  |

|              | 2 byte | ×                                                                           | Δ        | $\Delta$ | ×      |  |  |

|              | 3 byte | ×                                                                           | Δ        | ×        | ×      |  |  |

o :Correct Reception

$\Delta$  :The error (1) above only occurs.

$\times$  :The both error (1) and (2) occur.

The examples in each case are shown below.

[Countermeasures]

Please take either of the following countermeasures when you use SH7710 E-DMAC.

Please do not use the padding insertion function of E-DMAC.

When a CRC error occurs in the case the receiving data padding insertion function is set enabled, please execute a Software

Reset by taking the following procedure to recover your system.

a) Check EtherC/E-DMAC Status Register (EESR) bit 0(CERF) = 1 to confirm a Receive Frame CRC Error.

b) Execute a Software Reset by setting E-DMAC Mode Register (EDMR) bit 0(SWR) = 1.

c) Execute an initial set-up of EtherC, E-DMAC and receive descriptors.

d) Activate a receive function of E-DMAC by setting EDRRR bit 0(RR) = 1.

e) Start to receive data by setting EtherC Mode Register (ECMR) bit 6(RE) = 1.