# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                  |         | Document<br>No.         | TN-RX*-A0243A/E                                                                           | Rev.    | 1.00 |

|-----------------------|----------------------------------------------------------------------------------------------------------|---------|-------------------------|-------------------------------------------------------------------------------------------|---------|------|

| Title                 | Errata to the Section on Electrical Characteristics in the User's Manuals for the RX72M and RX72N Groups |         | Information<br>Category | Technical Notification                                                                    |         |      |

| Applicable<br>Product |                                                                                                          | Lot No. |                         | RX72M Group User's<br>Hardware Rev.1.00                                                   | Manual: |      |

|                       | RX72M Group,<br>RX72N Group                                                                              | All     | Reference<br>Document   | (R01UH0804EJ0100)<br>RX72N Group User's Manual:<br>Hardware Rev.1.00<br>(R01UH0824EJ0100) |         |      |

This document describes corrections to the section on Electrical Characteristics in the User's Manual: Hardware, Rev.1.00 for the applicable products stated above. Page, table, and figure numbers are based on the manual for the RX72M Group. Refer to the table on the last page of this update for the corresponding page, table, and figure numbers in the manual for the RX72N Group. Group.

# • Page 3243 of 3322

The frequency of ICLK described in Conditions of Table 65.26, Bus Timing is corrected as follows.

## Before correction

```

Table 65.26

Bus Timing

Conditions 1: VCC = AVCC0 = AVCC1 = VCC USB = V<sub>BATT</sub> = 2.7 to 3.6 V, 2.7 V ≤ VREFH0 ≤ AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V,

ICLK = PCLKA = 8 to 120 MHz, PCLKB = BCLK = SDCLK = 8 to 60 MHz, T<sub>a</sub> = T<sub>opr</sub>,

Output load conditions: V_{OH} = VCC \times 0.5, V_{OL} = VCC \times 0.5, C = 30 \text{ pF},

High-drive output is selected by the driving ability control register.

Conditions 2: VCC = AVCC0 = AVCC1 = VCC USB = V<sub>BATT</sub> = 3.0 to 3.6 V, 3.0 V ≤ VREFH0 ≤ AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V,

ICLK = PCLKA = 8 to 120 MHz, PCLKB = \overline{8} to 60 MHz, 60 MHz < BCLK = SDCLK \leq 80 MHz, T<sub>a</sub> = T<sub>opr</sub>,

Output load conditions: V_{OH} = VCC \times 0.5, V_{OL} = VCC \times 0.5,

C = 15 pF for the SDCLK pin, C = 30 pF for other pins.

To control the drive capacity when using the SDRAM: set the PFBCR3.SDCLKDRV bit in external bus control

register 1 to 1 to select the drive capacity of the SDCLK pin,

and set the SDRAM pins other than the SDCLK pin as high-

speed-interface driving outputs.

After correction

Table 61.26

Bus Timing

Conditions 1: VCC = AVCC0 = AVCC1 = VCC_USB = V<sub>BATT</sub> = 2.7 to 3.6 V, 2.7 V ≤ VREFH0 ≤ AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS_USB = 0 V,

ICLK = 8 to 240 MHz, PCLKA = 8 to 120 MHz, PCLKB = BCLK = SDCLK = 8 to 60 MHz, T<sub>a</sub> = T<sub>opr</sub>,

Output load conditions: V_{OH} = 0.5 \times VCC, V_{OL} = 0.5 \times VCC, C = 30 \text{ pF},

High-drive output is selected by the drive capacity control register.

Conditions 2: VCC = AVCC0 = AVCC1 = VCC_USB = V<sub>BATT</sub> = 3.0 to 3.6 V, 3.0 V ≤ VREFH0 ≤ AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V,

ICLK = 60 to 240 MHz, PCLKA = 8 to 120 MHz, PCLKB = 8 to 60 MHz, 60 MHz < BCLK = SDCLK ≤ 80 MHz,

T_a = T_{opr},

Output load conditions: V_{OH} = 0.5 \times VCC, V_{OL} = 0.5 \times VCC,

C = 15 \text{ pF} for the SDCLK pin, C = 30 \text{ pF} for other pins.

To control the drive capacity when using the SDRAM: set the PFBCR3.SDCLKDRV bit in external bus control

register 1 to 1 to select the drive capacity of the SDCLK pin,

and set the SDRAM pins other than the SDCLK pin as high-

speed-interface driving outputs.

```

## • Page 3256 of 3322

The frequency of ICLK described in Conditions of Table 65.27, EXDMAC Timing is corrected as follows.

#### Before correction

#### Table 65.27 EXDMAC Timing

#### After correction

#### Table 65.27 EXDMAC Timing

```

Conditions: VCC = AVCC0 = AVCC1 = VCC_USB = V_{BATT} = 2.7 to 3.6 V, 2.7 V ≤ VREFH0 ≤ AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS_USB = 0 V,

ICLK = 8 to 240 MHz, PCLKA = 8 to 120 MHz, PCLKB = 8 to 60 MHz, BCLK = SDCLK = 8 to 80 MHz, T<sub>a</sub> = T<sub>opr</sub>,

Output load conditions: V<sub>OH</sub> = 0.5 × VCC, V<sub>OL</sub> = 0.5 × VCC, C = 30 pF,

High-drive output is selected by the drive capacity control register.

```

## • Page 2988 of 3322

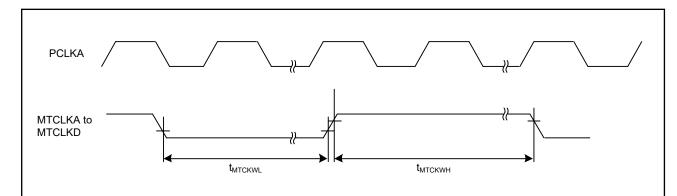

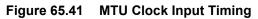

The MTIOC1A pin is added to Figure 65.41, MTU Clock Input Timing as follows.

Before correction

## After correction

## • Page 3264 of 3322

Figure 65.51, Output Disable Time of POEG in Response to the Oscillation Stop Detection is corrected as follows.

#### Before correction

| Main clock or PLL clo | ock           |              |              |               |                     | Qutput disabled |

|-----------------------|---------------|--------------|--------------|---------------|---------------------|-----------------|

| GPTW PWM output       | pin           |              |              |               | t <sub>POEGOS</sub> |                 |

| Figure 65.51          | Output Disabl | e Time of PO | EG in Respor | ise to the Os | cillation Stop De   | etection        |

| er correction         |               |              |              |               |                     |                 |

| Main clock                                                          |         |             |

|---------------------------------------------------------------------|---------|-------------|

| Oscillation stop detection<br>signal (internal signal) <sub>-</sub> | )/      |             |

| GPTW PWM output pins                                                | s Outpu | ts disabled |

Figure 65.51 Output Disable Time of POEG in Response to the Oscillation Stop Detection

## • Page 3280 of 3322

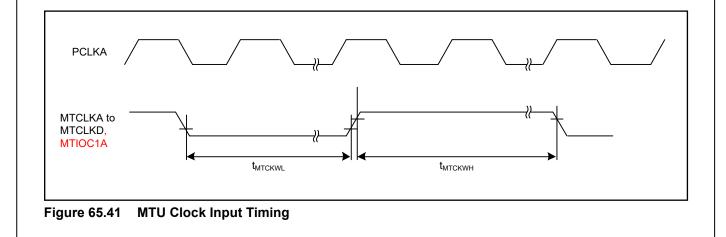

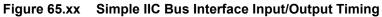

The following figure is added to illustrate the input and output timing of the simple IIC bus interface.

#### After correction

# • Page, Table, and Figure Numbers

| ltom                                                                                                 | Page, Table, and Figure Numbers   |                                   |  |

|------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--|

| Item                                                                                                 | RX72M Group                       | RX72N Group                       |  |

| Table of Bus Timing                                                                                  | Page 3243 of 3322<br>Table 65.26  | Page 3143 of 3222<br>Table 63.26  |  |

| Table of EXDMAC Timing                                                                               | Page 3256 of 3322<br>Table 65.27  | Page 3156 of 3222<br>Table 63.27  |  |

| Figure of MTU Clock Input Timing                                                                     | Page 3260 of 3322<br>Figure 65.41 | Page 3160 of 3222<br>Figure 63.41 |  |

| Figure of Output Disable Time of POEG in Response to the Oscillation Stop Detection                  | Page 3264 of 3322<br>Figure 65.51 | Page 3164 of 3222<br>Figure 63.51 |  |

| Figure of RIIC Bus Interface Input/Output Timing and<br>Simple IIC Bus Interface Input/Output Timing | Page 3280 of 3322<br>Figure 65.72 | Page 3180 of 3222<br>Figure 63.72 |  |