# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                   |                | Document<br>No.         | TN-RX*-A0205A/E                             | Rev. | 1.00 |

|-----------------------|-----------------------------------------------------------|----------------|-------------------------|---------------------------------------------|------|------|

| Title                 | Errata to RX66T Group User's Manual: Hardware<br>Rev.1.00 |                | Information<br>Category | Technical Notification                      |      |      |

| Applicable<br>Product | RX66T Group                                               | Lot No.<br>All | Reference<br>Document   | RX66T Group User's I<br>Rev.1.00 (R01UH0749 |      |      |

This document describes corrections to the RX66T Group User's Manual: Hardware, Rev.1.00.

The corrections are indicated in red in the list below.

#### • Page 52 of 2314

The CoreMark score in "Features" section is corrected as follows.

#### Before correction

- 32-bit RXv3 CPU core

- Max. operating frequency: 160 MHz Capable of 816 Core Mark in operation at 160 MHz

#### After correction

#### ■ 32-bit RXv3 CPU core

• Maximum operating frequency: 160 MHz Capable of 928 CoreMark in operation at 160 MHz

#### • Page 599 of 2314

Description in "Driving Ability Switching" column of P36 and P37 is corrected as follows.

#### Before correction

#### Table 20.5 Port Functions

| Port  | Pin        | Input Pull-up | Open-Drain<br>Output | Driving Ability Switching | 5-V Tolerant |

|-------|------------|---------------|----------------------|---------------------------|--------------|

|       |            | ()            | Omitted)             |                           |              |

| PORT3 | P30 to P35 | $\checkmark$  | $\checkmark$         | Normal drive/high drive   | —            |

|       | P36, P37   | $\checkmark$  | √                    |                           | _            |

|       |            | ()            | Omitted)             |                           |              |

#### After correction

#### Table 20.5 Port Functions

| Port  | Pin        | Input Pull-up | Open-Drain<br>Output | Driving Ability Switching | 5-V Tolerant |

|-------|------------|---------------|----------------------|---------------------------|--------------|

|       |            | (             | Omitted)             |                           |              |

| PORT3 | P30 to P35 | $\checkmark$  | $\checkmark$         | Normal drive/high drive   | —            |

|       | P36, P37   | $\checkmark$  | ✓                    | Fixed to normal output    | _            |

|       |            | (             | Omitted)             |                           |              |

# • Page 1065 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.5, General PWM Timer Start Source Select Register (GTSSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                 | Description                                                                                                                                                                                                             | R/W |

|-----|--------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | SSGTRGAR     | GTETRGA Rising Source Count<br>Start Enable              | 0: Disables count start at rising of the GTETRGA input<br>1: Enables count start at rising of the GTETRGA input                                                                                                         | R/W |

| b1  | SSGTRGAF     | GTETRGA Falling Source Count<br>Start Enable             | 0: Disables count start at falling of the GTETRGA input<br>1: Enables count start at falling of the GTETRGA input                                                                                                       | R/W |

|     | (Omitted     | : Descriptions for b7 and b6, b5 and b4                  | , and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                     |     |

| b8  | SSCARBL      | A Pin at Rising and B Pin 0 Source<br>Count Start Enable | <ol> <li>Disables count start at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> <li>Enables count start at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | SSCARBH      | A Pin at Rising and B Pin 1 Source<br>Count Start Enable | <ol> <li>Disables count start at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> <li>Enables count start at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | escriptions for b15 and b14, b13 and b1                  | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                  |     |

|     |              | (Omitted: b31 to b                                       | o16 are not modified)                                                                                                                                                                                                   |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                            | R/W |

|-----|--------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | SSGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li><sup>b1 b0</sup></li> <li>0 0: The GTETRGA signal is not used as a trigger to start counting.</li> <li>0 1: The counter starts at a rising edge of the GTETRGA</li> </ul>                                                                     | R/W |

| b1  | SSGTRGAF     | _                                                       | signal.<br>1 0: The counter starts at a falling edge of the GTETRGA<br>signal.<br>1 1: The counter starts at both edges of the GTETRGA<br>signal.                                                                                                      | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                  |     |

| b8  | SSCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li>b9 b8</li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to start counting.</li> <li>0 1: The counter starts at a rising edge of the GTIOCnA</li> </ul>                                                                 | R/W |

| b9  | SSCARBH      | -                                                       | <ul> <li>signal while the GTIOCnB pin is driven low.</li> <li>1 0: The counter starts at a rising edge of the GTIOCnA signal while the GTIOCnB pin is driven high.</li> <li>1 1: The counter starts at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | escriptions for b15 and b14, b13 and                    | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                               |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                               |     |

# • Page 1068 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.6, General PWM Timer Stop Source Select Register (GTPSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                           | R/W |

|-----|--------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | PSGTRGAR     | GTETRGA Rising Source Count<br>Stop Enable              | 0: Disables count stop at rising of the GTETRGA input<br>1: Enables count stop at rising of the GTETRGA input                                                                                                         | R/W |

| b1  | PSGTRGAF     | GTETRGA Falling Source Count<br>Stop Enable             | 0: Disables count stop at falling of the GTETRGA input<br>1: Enables count stop at falling of the GTETRGA input                                                                                                       | R/W |

|     | (Omitted     | Descriptions for b7 and b6, b5 and b4                   | l, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                  |     |

| b8  | PSCARBL      | A Pin at Rising and B Pin 0 Source<br>Count Stop Enable | <ol> <li>Disables count stop at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> <li>Enables count stop at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | PSCARBH      | A Pin at Rising and B Pin 1 Source<br>Count Stop Enable | <ol> <li>Disables count stop at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> <li>Enables count stop at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | escriptions for b15 and b14, b13 and b1                 | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                |     |

|     |              | (Omitted: b31 to b                                      | o16 are not modified)                                                                                                                                                                                                 |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                          | R/W |

|-----|--------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | PSGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li><sup>b1 b0</sup></li> <li>0 0: The GTETRGA signal is not used as a trigger to stop counting.</li> <li>0 1: The counter stops at a rising edge of the GTETRGA</li> </ul>                                                                     | R/W |

| b1  | PSGTRGAF     |                                                         | signal.<br>1 0: The counter stops at a falling edge of the GTETRGA<br>signal.<br>1 1: The counter stops at both edges of the GTETRGA<br>signal.                                                                                                      | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                |     |

| b8  | PSCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li>b9 b8</li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to stop counting.</li> <li>0 1: The counter stops at a rising edge of the GTIOCnA</li> </ul>                                                                 | R/W |

| b9  | PSCARBH      | -                                                       | <ul> <li>signal while the GTIOCnB pin is driven low.</li> <li>1 0: The counter stops at a rising edge of the GTIOCnA signal while the GTIOCnB pin is driven high.</li> <li>1 1: The counter stops at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                             |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                             |     |

# • Page 1071 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.7, General PWM Timer Clear Source Select Register (GTCSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                   | Description                                                                                                                                                                                                                 | R/W |

|-----|--------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | CSGTRGAR     | GTETRGA Rising Source Counter<br>Clear Enable              | 0: Disables counter clear at rising of the GTETRGA input<br>1: Enables counter clear at rising of the GTETRGA input                                                                                                         | R/W |

| b1  | CSGTRGAF     | GTETRGA Falling Source Counter<br>Clear Enable             | 0: Disables counter clear at falling of the GTETRGA input<br>1: Enables counter clear at falling of the GTETRGA input                                                                                                       | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and b4                      | , and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                         |     |

| b8  | CSCARBL      | A Pin at Rising and B Pin 0 Source<br>Counter Clear Enable | <ol> <li>Disables counter clear at rising of the GTIOCnA pin<br/>input while the GTIOCnB pin input is 0.</li> <li>Enables counter clear at rising of the GTIOCnA pin<br/>input while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | CSCARBH      | A Pin at Rising and B Pin 1 Source<br>Counter Clear Enable | <ol> <li>Disables counter clear at rising of the GTIOCnA pin<br/>input while the GTIOCnB pin input is 1.</li> <li>Enables counter clear at rising of the GTIOCnA pin<br/>input while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and b1                     | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                      |     |

|     |              | (Omitted: b31 to b                                         | o16 are not modified)                                                                                                                                                                                                       |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                                    | R/W |

|-----|--------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | CSGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li>b1 b0</li> <li>0 0: The GTETRGA signal is not used as a trigger to clear the counter.</li> <li>0 1: The counter is cleared at a rising edge of the OTETROA signal</li> </ul>                                                                          | R/W |

| b1  | CSGTRGAF     |                                                         | <ul> <li>GTETRGA signal.</li> <li>1 0: The counter is cleared at a falling edge of the GTETRGA signal.</li> <li>1 1: The counter is cleared at both edges of the GTETRGA signal.</li> </ul>                                                                    | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                          |     |

| b8  | CSCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li>b9 b8</li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to clear the counter.</li> <li>0 1: The counter is cleared at a rising edge of the GTIOCnA</li> </ul>                                                                  | R/W |

| b9  | CSCARBH      | -                                                       | <ul> <li>signal while the GTIOCnB pin is driven low.</li> <li>1 0: The counter is cleared at a rising edge of the GTIOCnA signal while the GTIOCnB pin is driven high.</li> <li>1 1: The counter is cleared at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                                       |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                                       |     |

#### • Page 1074 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.8, General PWM Timer Count-Up Source Select Register (GTUPSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                              | Description                                                                                                                                                                                                       | R/W |

|-----|--------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | USGTRGAR     | GTETRGA Rising Source Count-Up<br>Enable              | 0: Disables count-up at rising of the GTETRGA input<br>1: Enables count-up at rising of the GTETRGA input                                                                                                         | R/W |

| b1  | USGTRGAF     | GTETRGA Falling Source<br>Count-Up Enable             | 0: Disables count-up at falling of the GTETRGA input<br>1: Enables count-up at falling of the GTETRGA input                                                                                                       | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and b4                 | , and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                               |     |

| b8  | USCARBL      | A Pin at Rising and B Pin 0 Source<br>Count-Up Enable | <ol> <li>Disables count-up at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> <li>Enables count-up at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | USCARBH      | A Pin at Rising and B Pin 1 Source<br>Count-Up Enable | <ol> <li>Disables count-up at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> <li>Enables count-up at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and b1                | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                            |     |

|     |              | (Omitted: b31 to b                                    | 16 are not modified)                                                                                                                                                                                              |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W |

|-----|--------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | USGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li>b1 b0</li> <li>0 0: The GTETRGA signal is not used as a trigger to increment the counter.</li> <li>0 1: The counter is incremented at a rising edge of the output of the distance of</li></ul> | R/W |

| b1  | USGTRGAF     | -                                                       | <ul> <li>GTETRGA signal.</li> <li>1 0: The counter is incremented at a falling edge of the GTETRGA signal.</li> <li>1 1: The counter is incremented at both edges of the GTETRGA signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| b8  | USCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li><sup>b9 b8</sup></li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to increment the counter.</li> <li>0 1: The counter is incremented at a rising edge of the</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W |

| b9  | USCARBH      | -                                                       | <ul> <li>GTIOCnA signal while the GTIOCnB pin is driven low.</li> <li>1 0: The counter is incremented at a rising edge of the<br/>GTIOCnA signal while the GTIOCnB pin is driven high.</li> <li>1 1: The counter is incremented at a rising edge of the<br/>GTIOCnA signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

# • Page 1077 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.9, General PWM Timer Count-Down Source Select Register (GTDNSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                           | R/W |

|-----|--------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | DSGTRGAR     | GTETRGA Rising Source Count-<br>Down Enable             | 0: Disables count-down at rising of the GTETRGA input<br>1: Enables count-down at rising of the GTETRGA input                                                                                                         | R/W |

| b1  | DSGTRGAF     | GTETRGA Falling Source Count-<br>Down Enable            | 0: Disables count-down at falling of the GTETRGA input<br>1: Enables count-down at falling of the GTETRGA input                                                                                                       | R/W |

|     | (Omitted     | Descriptions for b7 and b6, b5 and b4                   | , and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                   |     |

| b8  | DSCARBL      | A Pin at Rising and B Pin 0 Source<br>Count-Down Enable | <ol> <li>Disables count-down at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> <li>Enables count-down at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | DSCARBH      | A Pin at Rising and B Pin 1 Source<br>Count-Down Enable | <ol> <li>Disables count-down at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> <li>Enables count-down at rising of the GTIOCnA pin input<br/>while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and b1                  | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                |     |

|     |              | (Omitted: b31 to b                                      | o16 are not modified)                                                                                                                                                                                                 |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                                                    | R/W |

|-----|--------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | DSGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li>b1 b0</li> <li>0 0: The GTETRGA signal is not used as a trigger to decrement the counter.</li> <li>0 1: The counter is decremented at a rising edge of the OTETRO decimation.</li> </ul>                                                                              | R/W |

| b1  | DSGTRGAF     |                                                         | <ul> <li>GTETRGA signal.</li> <li>1 0: The counter is decremented at a falling edge of the GTETRGA signal.</li> <li>1 1: The counter is decremented at both edges of the GTETRGA signal.</li> </ul>                                                                            | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                                          |     |

| b8  | DSCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li><sup>b9 b8</sup></li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to decrement the counter.</li> <li>0 1: The counter is decremented at a rising edge of the</li> </ul>                                                                       | R/W |

| b9  | DSCARBH      | -                                                       | <ul> <li>GTIOCnA signal while the GTIOCnB pin is driven low.</li> <li>1 0: The counter is decremented at a rising edge of the GTIOCnA signal while the GTIOCnB pin is driven high.</li> <li>1 1: The counter is decremented at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                                                       |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                                                       |     |

#### • Page 1080 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.10, General PWM Timer Input Capture Source Select Register A (GTICASR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                          | Description                                                                                                                                                                                                                               | R/W |

|-----|--------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | ASGTRGAR     | GTETRGA Rising Source GTCCRA<br>Input Capture Enable              | <ul> <li>0: Disables GTCCRA input capture at rising of the<br/>GTETRGA input</li> <li>1: Enables GTCCRA input capture at rising of the<br/>GTETRGA input</li> </ul>                                                                       | R/W |

| b1  | ASGTRGAF     | GTETRGA Falling Source GTCCRA<br>Input Capture Enable             | <ol> <li>Disables GTCCRA input capture at falling of the<br/>GTETRGA input</li> <li>Enables GTCCRA input capture at falling of the<br/>GTETRGA input</li> </ol>                                                                           | R/W |

|     | (Omitted     | : Descriptions for b7 and b6, b5 and b4,                          | and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                         |     |

| b8  | ASCARBL      | A Pin at Rising and B Pin 0 Source<br>GTCCRA Input Capture Enable | <ol> <li>Disables GTCCRA input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 0.</li> <li>Enables GTCCRA input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | ASCARBH      | A Pin at Rising and B Pin 1 Source<br>GTCCRA Input Capture Enable | <ol> <li>Disables GTCCRA input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 1.</li> <li>Enables GTCCRA input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | escriptions for b15 and b14, b13 and b12                          | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                    |     |

|     |              |                                                                   |                                                                                                                                                                                                                                           |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                                                                                                                                                | R/W |

|-----|--------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | ASGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li>b1 b0</li> <li>0 0: The GTETRGA signal is not used as a trigger to capture the counter value in the GTCCRA register.</li> <li>0 1: The counter value is captured in the GTCCRA register</li> </ul>                                                                                                                                                                | R/W |

| b1  | ASGTRGAF     |                                                         | <ul> <li>at a rising edge of the GTETRGA signal.</li> <li>1 0: The counter value is captured in the GTCCRA register<br/>at a falling edge of the GTETRGA signal.</li> <li>1 1: The counter value is captured in the GTCCRA register<br/>at both edges of the GTETRGA signal.</li> </ul>                                                                                    | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                                                                                                                                      |     |

| b8  | ASCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li>b9 b8</li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to capture the counter value in the GTCCRA register.</li> <li>0 1: The counter value is captured in the GTCCRA register</li> </ul>                                                                                                                                                 | R/W |

| b9  | ASCARBH      | -                                                       | <ul> <li>at a rising edge of the GTIOCnA signal while the<br/>GTIOCnB pin is driven low.</li> <li>1 0: The counter value is captured in the GTCCRA register<br/>at a rising edge of the GTIOCnA signal while the<br/>GTIOCnB pin is driven high.</li> <li>1 1: The counter value is captured in the GTCCRA register<br/>at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                                                                                                                                                   |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                                                                                                                                                   |     |

#### • Page 1084 of 2314

Bit name and expressions of the description column for the bit description table in 24.2.11, General PWM Timer Input Capture Source Select Register B (GTICBSR) are modified as follows.

#### Before correction

| Bit | Symbol       | Bit Name                                                          | Description                                                                                                                                                                                                                               | R/W |

|-----|--------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | BSGTRGAR     | GTETRGA Rising Source GTCCRB<br>Input Capture Enable              | <ul> <li>0: Disables GTCCRB input capture at rising of the<br/>GTETRGA input</li> <li>1: Enables GTCCRB input capture at rising of the<br/>GTETRGA input</li> </ul>                                                                       | R/W |

| b1  | BSGTRGAF     | GTETRGA Falling Source GTCCRB<br>Input Capture Enable             | <ul> <li>0: Disables GTCCRB input capture at falling of the<br/>GTETRGA input</li> <li>1: Enables GTCCRB input capture at falling of the<br/>GTETRGA input</li> </ul>                                                                     | R/W |

|     | (Omitted     | Descriptions for b7 and b6, b5 and b4,                            | and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                         |     |

| b8  | BSCARBL      | A Pin at Rising and B Pin 0 Source<br>GTCCRB Input Capture Enable | <ol> <li>Disables GTCCRB input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 0.</li> <li>Enables GTCCRB input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 0.</li> </ol> | R/W |

| b9  | BSCARBH      | A Pin at Rising and B Pin 1 Source<br>GTCCRB Input Capture Enable | <ol> <li>Disables GTCCRB input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 1.</li> <li>Enables GTCCRB input capture at rising of the<br/>GTIOCnA pin input while the GTIOCnB pin input is 1.</li> </ol> | R/W |

|     | (Omitted: De | escriptions for b15 and b14, b13 and b12                          | 2, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                    |     |

|     |              |                                                                   |                                                                                                                                                                                                                                           |     |

| Bit | Symbol       | Bit Name                                                | Description                                                                                                                                                                                                                                                                                                                                                                | R/W |

|-----|--------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | BSGTRGAR     | GTETRGA Signal Edge Select                              | <ul> <li>b1 b0</li> <li>0 0: The GTETRGA signal is not used as a trigger to capture the counter value in the GTCCRB register.</li> <li>0 1: The counter value is captured in the GTCCRB register</li> </ul>                                                                                                                                                                | R/W |

| b1  | BSGTRGAF     |                                                         | <ul> <li>at a rising edge of the GTETRGA signal.</li> <li>1 0: The counter value is captured in the GTCCRB register<br/>at a falling edge of the GTETRGA signal.</li> <li>1 1: The counter value is captured in the GTCCRB register<br/>at both edges of the GTETRGA signal.</li> </ul>                                                                                    | R/W |

|     | (Omitted:    | Descriptions for b7 and b6, b5 and                      | b4, and b3 and b2 are similar to those for b1 and b0)                                                                                                                                                                                                                                                                                                                      |     |

| b8  | BSCARBL      | GTIOCnA Signal Rising Edge<br>Applying Condition Select | <ul> <li><sup>b9 b8</sup></li> <li>0 0: Rising edge of the GTIOCnA signal is not used as a trigger to capture the counter value in the GTCCRB register.</li> <li>0 1: The counter value is captured in the GTCCRB register</li> </ul>                                                                                                                                      | R/W |

| b9  | BSCARBH      | -                                                       | <ul> <li>at a rising edge of the GTIOCnA signal while the<br/>GTIOCnB pin is driven low.</li> <li>1 0: The counter value is captured in the GTCCRB register<br/>at a rising edge of the GTIOCnA signal while the<br/>GTIOCnB pin is driven high.</li> <li>1 1: The counter value is captured in the GTCCRB register<br/>at a rising edge of the GTIOCnA signal.</li> </ul> | R/W |

|     | (Omitted: De | scriptions for b15 and b14, b13 and                     | b b12, and b11 and b10 are similar to those for b9 and b8)                                                                                                                                                                                                                                                                                                                 |     |

|     |              | (Omitted: b31                                           | to b16 are not modified)                                                                                                                                                                                                                                                                                                                                                   |     |

#### • Page 1896 of 2314

The first paragraph of the descriptions for the ANSB0n bit in 38.2.6 (1) S12AD.ADANSB0 is modified as follows.

#### Before correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSB0n bit selects analog input channels for A/D conversion from among AN000 to AN007 in group B when group scan mode is selected. The S12AD.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD.ADANSA0 and ADANSA1 registers and the S12AD.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSB0n bit selects analog input channels for A/D conversion from among AN000 to AN007 in group B when group scan mode is selected. The S12AD.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD.ADANSA0 register), the channels specified in group C (the S12AD.ADANSC0 register), and the channels corresponding to group A, selected with the

S12AD.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1897 of 2314

The first paragraph of the descriptions for the ANSB0n bit in 38.2.6 (2) S12AD1.ADANSB0 is modified as follows.

#### Before correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSB0n bit selects analog input channels for A/D conversion from among AN100 to AN107 in group B when group scan mode is selected. The S12AD1.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD1.ADANSA0 and ADANSA1 registers and the S12AD1.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSB0n bit selects analog input channels for A/D conversion from among AN100 to AN107 in group B when group scan mode is selected. The S12AD1.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD1.ADANSA0 register), the channels specified in group C (the S12AD1.ADANSC0 register), and the channels corresponding to group A, selected with the S12AD1.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1898 of 2314

The first paragraph of the descriptions for the ANSB0n bit in 38.2.6 (3) S12AD2.ADANSB0 is modified as follows.

#### Before correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 11)

The ANSB0n bit selects analog input channels for A/D conversion from among AN200 to AN211 in group B when group scan mode is selected. The S12AD2.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD2.ADANSA0 and ADANSA1 registers and the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSB0n Bit (A/D Conversion Channel Select) (n = 00 to 11)

The ANSB0n bit selects analog input channels for A/D conversion from among AN200 to AN211 in group B when group scan mode is selected. The S12AD2.ADANSB0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD2.ADANSA0 and S12AD2.ADANSA1 registers), the channels specified in group C (the S12AD2.ADANSC0 and S12AD2.ADANSC1 registers), and the channels corresponding to group A, selected with the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1899 of 2314

The first paragraph of the descriptions for the ANSB1n bit in section 38.2.7, A/D Channel Select Register B1 (ADANSB1) is modified as follows.

#### Before correction

#### ANSB1n Bit (A/D Conversion Channel Select) (n = 00, 01)

The ANSB1n bit selects analog input channels for A/D conversion from among AN216 to AN217 in group B when group scan mode is selected. The S12AD2.ADANSB1 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD2.ADANSA0 and ADANSA1 registers and the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSB1n Bit (A/D Conversion Channel Select) (n = 00, 01)

The ANSB1n bit selects analog input channels for A/D conversion from among AN216 to AN217 in group B when group scan mode is selected. The S12AD2.ADANSB1 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD2.ADANSA0 and S12AD2.ADANSA1 registers), the channels specified in group C (the S12AD2.ADANSC0 and S12AD2.ADANSC1 registers), and the channels corresponding to group A, selected with the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1900 of 2314

The first paragraph of the descriptions for the ANSCOn bit in 38.2.8 (1) S12AD.ADANSCO is modified as follows.

#### Before correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSC0n bit selects analog input channels for A/D conversion from among AN000 to AN007 in group C when group scan mode is selected. The S12AD.ADANSC0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD.ADANSA0 and ADANSA1 registers and the S12AD.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSCOn bit selects analog input channels for A/D conversion from among AN000 to AN007 in group C when group scan mode is selected. The S12AD.ADANSCO register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD.ADANSAO register), the channels specified in group B (the S12AD.ADANSBO register), and the channels corresponding to group A, selected with the

S12AD.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1901 of 2314

The first paragraph of the descriptions for the ANSCOn bit in 38.2.8 (2) S12AD1.ADANSCO is modified as follows.

#### Before correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSCOn bit selects analog input channels for A/D conversion from among AN100 to AN107 in group C when group scan mode is selected. The S12AD1.ADANSCO register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD1.ADANSA0 and ADANSA1 registers and the S12AD1.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 07)

The ANSC0n bit selects analog input channels for A/D conversion from among AN100 to AN107 in group C when group scan mode is selected. The S12AD1.ADANSC0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD1.ADANSA0 register), the channels specified in group B (the S12AD1.ADANSB0 register), and the channels corresponding to group A, selected with the S12AD1.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1902 of 2314

The first paragraph of the descriptions for the ANSCOn bit in 38.2.8 (3) S12AD2.ADANSCO is modified as follows.

#### Before correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 11)

The ANSCOn bit selects analog input channels for A/D conversion from among AN200 to AN211 in group C when group scan mode is selected. The S12AD2.ADANSCO register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected by the S12AD2.ADANSA0 and ADANSA1 registers, the S12AD2.ADANSB0 and ADANSB1 registers, or the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded from the channels to be selected and the number of channels to be set.

#### After correction

#### ANSC0n Bit (A/D Conversion Channel Select) (n = 00 to 11)

The ANSC0n bit selects analog input channels for A/D conversion from among AN200 to AN211 in group C when group scan mode is selected. The S12AD2.ADANSC0 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD2.ADANSA0 and S12AD2.ADANSA1 registers), the channels specified in group B (the S12AD2.ADANSB0 and S12AD2.ADANSB1 registers), and the channels corresponding to group A, selected with the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 1903 of 2314

The first paragraph of the descriptions for the ANSC1n bit in section 38.2.9, A/D Channel Select Register C1 (ADANSC1) is modified as follows.

#### Before correction

#### ANSC1n Bit (A/D Conversion Channel Select) (n = 00, 01)

The ANSC1n bit selects analog input channels for A/D conversion from among AN216 to AN217 in group C when group scan mode is selected. The S12AD2.ADANSC1 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the channels corresponding to group A, selected with the S12AD2.ADANSA0 and ADANSA1 registers, the S12AD2.ADANSB0 and ADANSB1 registers, or the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode) should be excluded as the channels to be selected and the number of channels to be set.

#### After correction

#### ANSC1n Bit (A/D Conversion Channel Select) (n = 00, 01)

The ANSC1n bit selects analog input channels for A/D conversion from among AN216 to AN217 in group C when group scan mode is selected. The S12AD2.ADANSC1 register is used for group scan mode only; not used for any other modes. The channels specified in group A (the S12AD2.ADANSA0 and S12AD2.ADANSA1 registers), the channels specified in group B (the S12AD2.ADANSB0 and S12AD2.ADANSB1 registers), and the channels corresponding to group A, selected with the S12AD2.ADCSR.DBLANS[4:0] bits in double trigger mode should be excluded as the channels to be selected and the number of channels to be set.

#### • Page 2234 of 2314

Table 45.3, Recommended Operating Conditions (2) is added as follows.

#### After correction

#### Table 45.3 Recommended Operating Conditions (2)

| Item                                                     | Symbol           | Value           |

|----------------------------------------------------------|------------------|-----------------|

| Decoupling capacitance to stabilize the internal voltage | C <sub>VCL</sub> | 0.47 µF ± 30%*1 |

Note 1. Use a multilayer ceramic capacitor whose nominal capacitance is 0.47 µF and a capacitance tolerance is ±30% or better.

#### • Page 2236 of 2314

The output voltage of the VCL pin is added to Table 45.4, DC Characteristics (2) as follows.

#### After correction

#### Table 45.4DC Characteristics (2)

| Item                          | Symbol          | Min. | Тур. | Max. | Unit | Test Conditions |

|-------------------------------|-----------------|------|------|------|------|-----------------|

| Output voltage of the VCL pin | V <sub>CL</sub> | —    | 1.25 | _    | V    |                 |

#### • Page 2243 of 2314

Descriptions of total output current in Table 45.11, Permissible Output Currents are modified as follows.

#### Before correction

|                                               | Item                                                                                                          | Symbol            | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|------|

|                                               | (Omitted)                                                                                                     |                   |      |      |      | mA   |

| Permissible low-level output current (total)  | Total of all output pins (except for RIIC pins, P43, P47, PH1 to PH3, PH5 to PH7, P50 to P55, and P60 to P65) | Σ I <sub>OL</sub> | _    | _    | 110  | -    |

|                                               | Total of pins P43, P47, PH1 to PH3, PH5 to PH7, P50 to P55, and P60 to P65                                    |                   | _    | —    | 110  |      |

|                                               | (Omitted)                                                                                                     |                   |      |      |      |      |

| Permissible high-level output current (total) | Total of all output pins (except for P43, P47, PH1 to PH3, PH5 to PH7, P50 to P55, and P60 to P65)            | Σ I <sub>OH</sub> | _    | —    | -35  |      |

|                                               | Total of pins P43, P47, PH1 to PH3, PH5 to PH7, P50 to P55, and P60 to P65                                    |                   | —    | —    | -35  |      |

|                                                 | Item                     |           | Symbol            | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|--------------------------|-----------|-------------------|------|------|------|------|

|                                                 |                          | (Omitted) |                   |      |      |      | mA   |

| Permissible low-level output<br>current (total) | Total of all output pins |           | $\Sigma I_{OL}$   |      | —    | 110  |      |

|                                                 |                          | (Omitted) |                   |      |      |      |      |

| Permissible high-level output current (total)   | Total of all output pins |           | Σ I <sub>OH</sub> |      | —    | -35  |      |

RENESAS

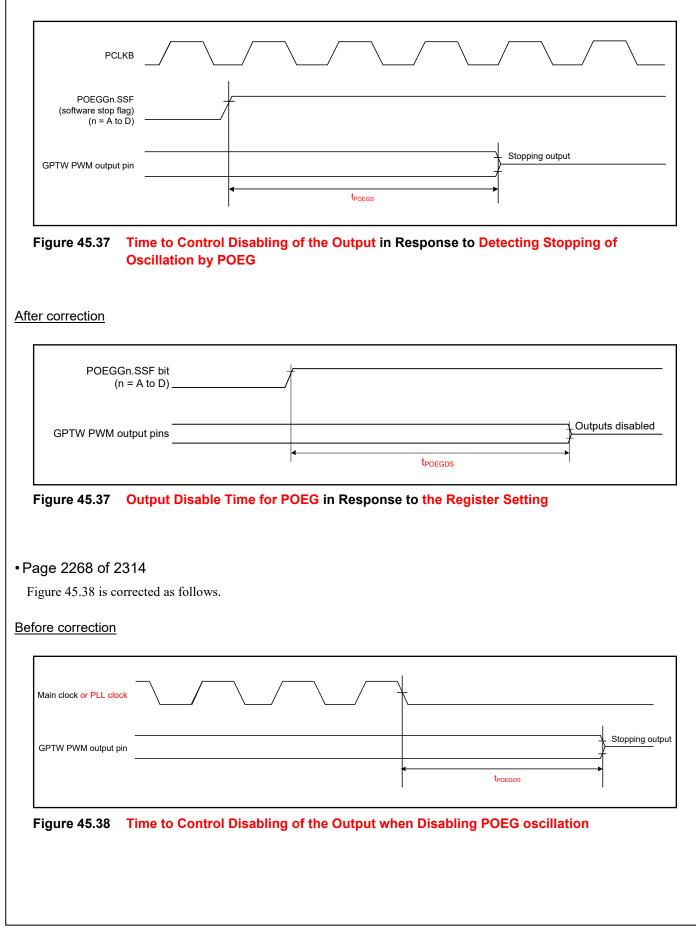

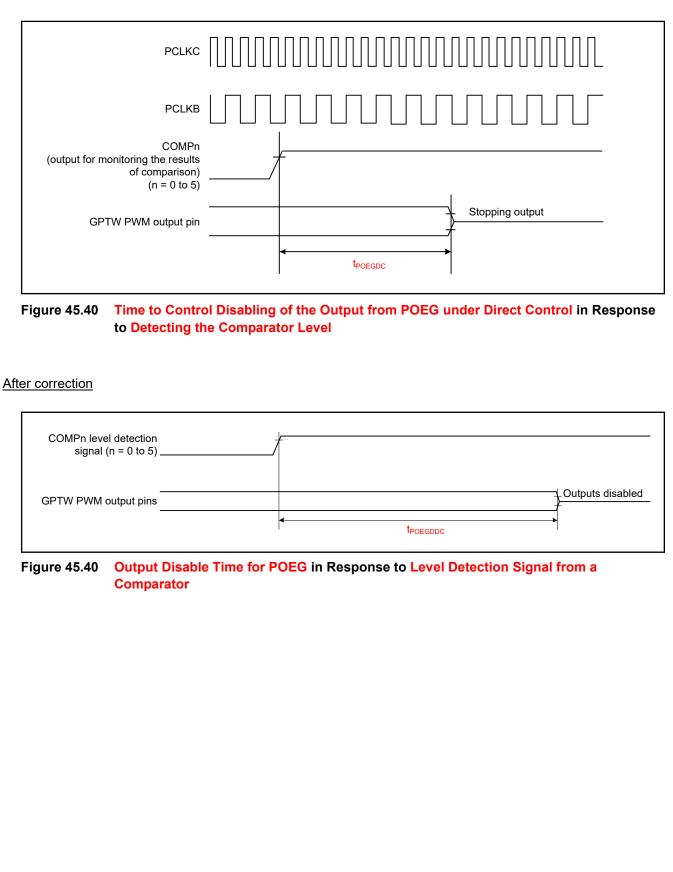

# • Page 2264 of 2314

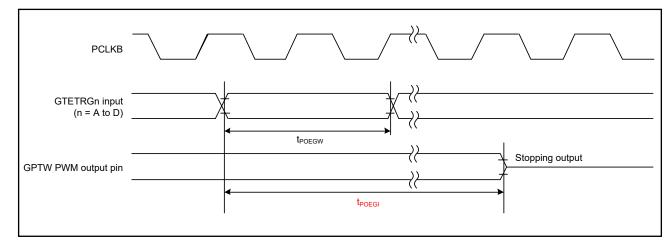

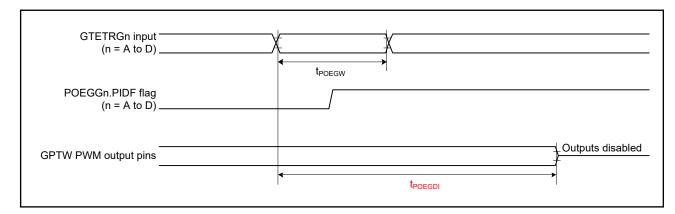

Maximum value for  $t_{POEGDC}$  in Table 45.30, POE and POEG Timing is corrected and some expressions are modified as follows.

|      | Iter                                                                      | n                                                                                                                                                          | Symbol               | Min. | typ. | Max.          | Unit*1  | Test Conditions                                                                                                                                                              |

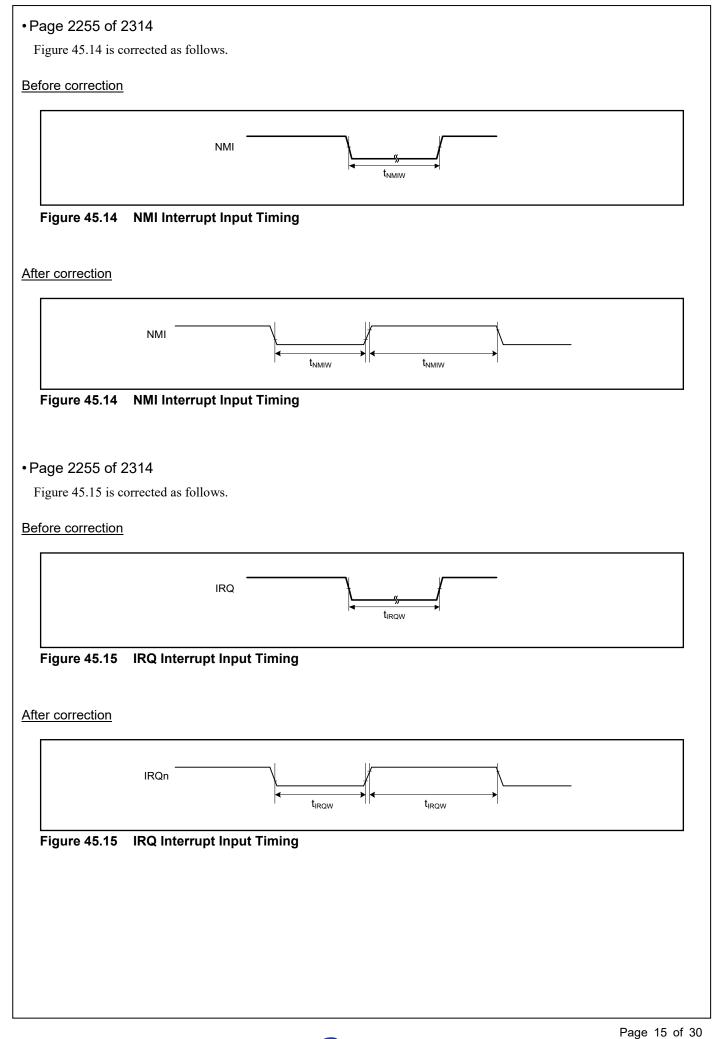

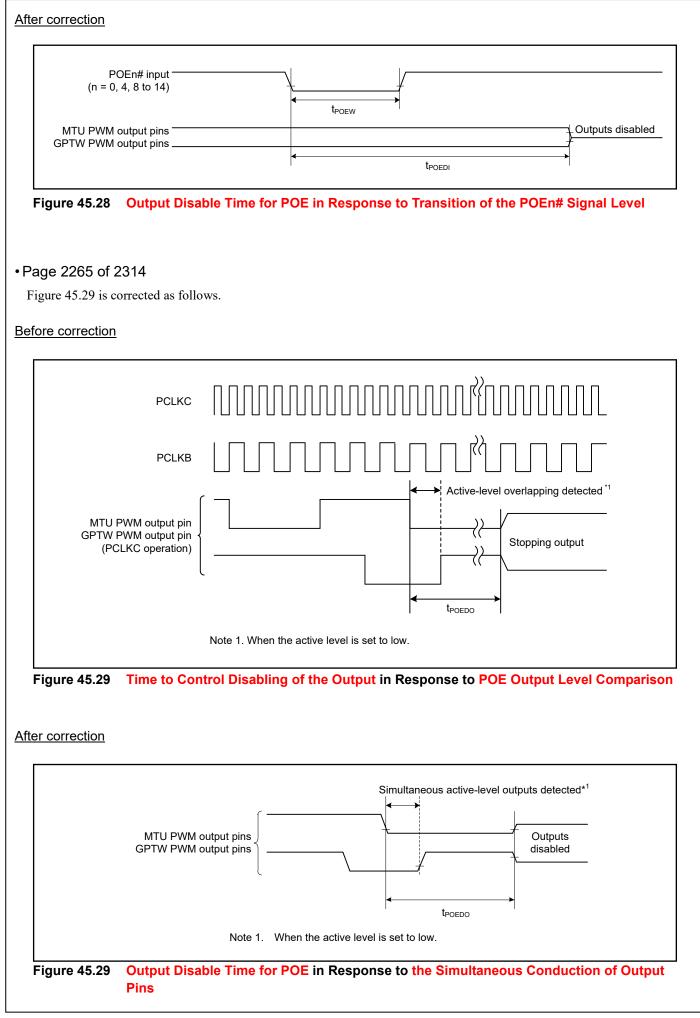

|------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|