# **RENESAS TECHNICAL UPDATE**

〒211-8668 神奈川県川崎市中原区下沼部1753 ルネサスエレクトロニクス株式会社 問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製品分類 |                                          | MPU & MCU | 発行番号   | TN-16C-A233A/J |                                                               | Rev. | 第1版 |

|------|------------------------------------------|-----------|--------|----------------|---------------------------------------------------------------|------|-----|

| 題名   | R32C/153グループ ユーザーズマニュアル ハードウェア編の<br>誤記訂正 |           |        | 情報分類           | 技術情報                                                          |      |     |

| 適用製品 | R32C                                     | /153 グループ | 対象ロット等 | 関連資料           | R32C/153グループ<br>ユーザーズマニュア<br>ハードウェア編 Rev<br>(RJJ09B0537-0110) |      |     |

R32C/153グループ ユーザーズマニュアル ハードウェア編 Rev.1.10において誤記がありましたので、以下のとおり訂正いたします。

### 〈訂正内容〉

•Page 62, 63, 76, 77, 90, 91, 104, 105 of 647

表4.42、表4.43、表4.56、表4.57、表4.70、表4.71、表4.84、表4.85のレジスタ名を以下のとおり訂正いたします。

【誤】

CANiアクセプタンスマスクレジスタk

【正】

CANiマスクレジスタk

•Page 65, 79, 93, 107 of 647

表4.45、表4.59、表4.73、表4.87のCiMSMRレジスタのリセット後の値を以下のとおり訂正いたします。

【誤】

XXXX XX00b

【正】

0000 0000b

### •Page 119 of 647

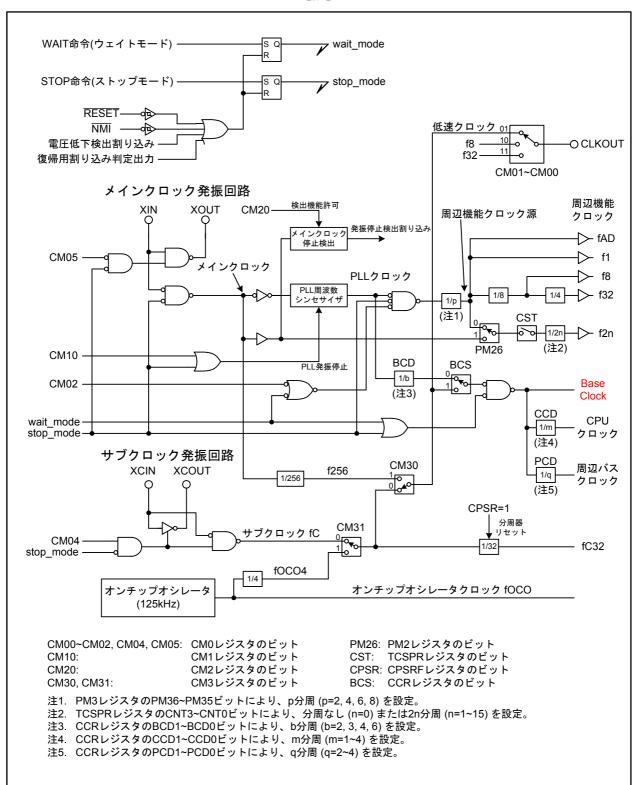

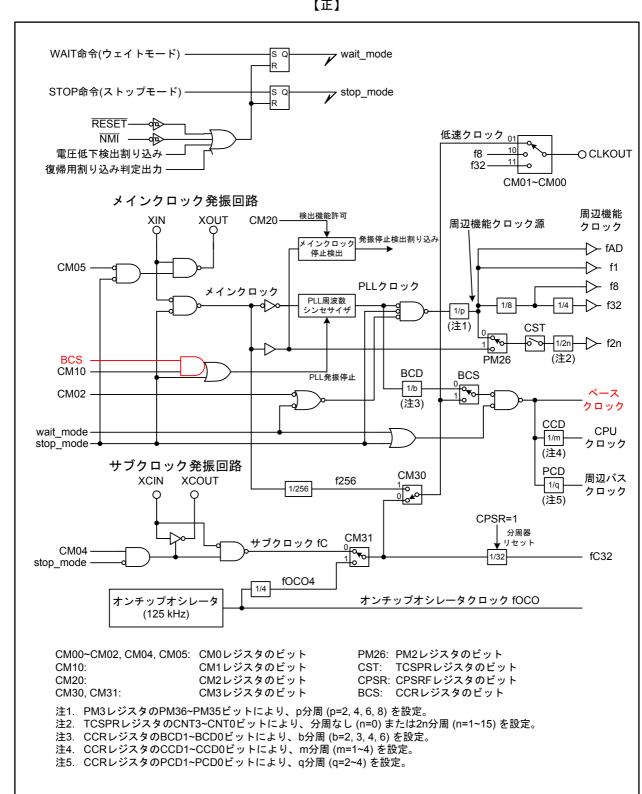

図7.1を以下のとおり訂正いたします。

### 【誤】

### 図7.1 クロック発生回路のブロック図

## 【正】

#### 図7.1 クロック発生回路のブロック図

### •Page 122 of 647

図7.4の注2の文章を以下のとおり訂正いたします。

#### 【誤】

注2. CCR レジスタのBCS ビットが"0"(ベースクロック源はPLLクロック)の場合、CM10 ビットを"1" にすることはできません。

#### 【正】

注2. CCR レジスタのBCS ビットが"0"(ベースクロック源はPLLクロック)の場合、CM10 ビットを"1" にしても PLL 周波数シンセサイザの発振は停止しません。

### •Page 133 of 647

7.2 本文の3段落目の一部を以下のとおり削除いたします。

#### 【誤】

発振停止が検出されたとき、CM2レジスタの以下のビットが変化します。

- •CM22ビット=1(メインクロック停止を検出)

- CM23 ビット=1 (メインクロック停止)(図 7.18 状態遷移図(サブクロック使用時)参照)

#### 【正】

発振停止が検出されたとき、CM2レジスタの以下のビットが変化します。

- CM22ビット=1(メインクロック停止を検出)

- •CM23ビット=1(メインクロック停止)

### •Page 151 of 647

図9.1の注1を以下のとおり変更いたします。

#### 【誤】

注1. PRC2 ビットは"1"を書いた後、任意の番地に書き込みを実行すると"0"になります。他のビットは "0"になりませんので、プログラムで"0"にしてください。

#### 【正】

注1. PRC2 ビットは"1"を書いた後、任意の番地に書き込みを実行すると"0"になります。

### •Page 203 of 647

13.1.2項本文の1段落目を以下のとおり変更いたします。

#### 【誤】

DMAC II インデックスは12~60 バイトで構成されるデータテーブルで、転送モード、転送カウンタ、転送元アドレス(または即値データ)、演算対象のアドレス、転送先アドレス、チェーン転送ベースアドレス、転送完了割り込みベクタアドレスのパラメータを格納します。

#### (正)

DMAC IIインデックスは12~60 バイトで構成されるデータテーブルで、転送モード、転送カウンタ、転送元アドレス(または即値データ)、演算対象のアドレス、転送先アドレス、チェーン転送ベースアドレス、転送完了割り込み処理分岐先アドレスの各パラメータを格納します。

発行日: 2013年5月23日

#### •Page 203 of 647

図13.2のパラメータ名を以下のとおり変更いたします。

【誤】

転送完了割り込みベクタアドレス

【正】

転送完了割り込み処理分岐先アドレス

### •Page 203 of 647

図13.2内の下部説明文の一部を以下のとおり変更いたします。

#### 【誤】

DMAC II の起動要因となる周辺機能割り込みの割り込みベクタに、DMAC II インデックスの先頭番地を設定してください。

### 【正】

DMAC II の起動要因となる周辺機能割り込みの割り込みベクタ<mark>領域に、DMAC II</mark>インデックスの先頭番地を設定してください。

### •Page 204 of 647

表13.2上部IADRの名称および説明を以下のとおり変更いたします。

#### 【誤】

・転送完了割り込みベクタアドレス(IADR)

4バイトデータで、転送完了割り込み処理の飛び先アドレスを設定してください。転送完了割り込みを 使用する場合のみ、このデータを設定してください。

#### 【正】

・転送完了割り込み処理分岐先アドレス(IADR)

4バイトデータで、転送完了割り込み処理ルーチンの先頭番地を設定してください。転送完了割り込みを使用する場合のみ、このデータを設定してください。

### •Page 206 of 647

13.1.4項本文の1段落目を以下のとおり変更いたします。

#### 【誤】

DMAC II の起動要因となる周辺機能割り込みの割り込みベクタに、DMAC II インデックスの先頭番地を設定してください。

#### 【正】

DMAC II の起動要因となる周辺機能割り込みの割り込みベクタ<mark>領域に、DMAC II インデックスの先頭番地を設定してください。</mark>

#### •Page 216 of 647

15.1 本文ワンショットタイマモードの説明を以下のとおり変更いたします。

#### 【誤】

カウント値が"0000h"になるまでの間1度だけパルスを出力するモード

#### 【正】

トリガが入力されてから、カウント値が"0000h"になるまでの期間、パルスを出力するモード

### •Page 227 of 647

図15.13、図15.14の端子名を以下のとおり訂正いたします。

【誤】

INT2

【正】

ĪNT2

### •Page 254 of 647

16.3 本文の3段落目の一部を以下のとおり削除いたします。

### 【誤】

また三相モード1では、タイマB2割り込みごとにカウンタへのリロード値がTAi、TAi-1 (i=4, 1, 2)と入れ替わるため、タイマB2割り込みの頻度を半分に減らすことができます。このモードではTAi レジスタ設定値とTAi1 レジスタ設定値の合計がTB2 レジスタ設定値と一致するようにします。

#### (正)

また三相モード1では、タイマB2割り込みごとにカウンタへのリロード値がTAi、TAi-1 (i=4, 1, 2)と入れ替わるため、タイマB2割り込みの頻度を半分に減らすことができます。

### •Page 259 of 647

図16.18の注2を以下のとおり訂正いたします。

### 【誤】

注2. INV1レジスタのINV11ビットが"1"(三相モード1)の場合

#### 【正】

注2. INVC1 レジスタの INV11 ビットが"1"(三相モード1) の場合

### •Page 269 of 647

図17.7のUiIRSビットの機能欄を以下のとおり変更いたします。

【誤】

0: UiTB レジスタ空 (TI=1)

【正】

0: 送信バッファ空 (TI=1)

### •Page 279 of 647

図17.18の波形の名称を以下のとおり訂正いたします。

【誤】

UiC0 レジスタのTXEPTフラグ

【正】

UiC0レジスタのTXEPTビット

### •Page 279 of 647

図17.18の設定条件記載箇所の4項目目を以下のとおり訂正いたします。

### 【誤】

• UiC1 レジスタ、U34CON レジスタのUiRS ビット=0 (UiTB レジスタ空で割り込み要求発生)

#### (正)

• UiC1 レジスタ、U34CON レジスタのUilRS ビット=0 (送信バッファ空で割り込み要求発生)

### •Page 320 of 647

18.1.3項本文を以下のとおり変更いたします。

### 【誤】

選択した端子の入力電圧を1回ずつA/D変換するモードです。表 18.4に単掃引モードの仕様を示します。

#### 【正】

選択した複数の端子の入力電圧を1回ずつ変換するモードです。表 18.4に単掃引モードの仕様を示します。

#### •Page 320 of 647

表18.4の機能の仕様欄を以下のとおり変更いたします。

#### 【誤】

AD0CON1 レジスタのSCAN1~SCAN0 ビットとAD0CON2 レジスタのAPS1~APS0 ビットで選択した端子の入力電圧を1回ずつA/D変換する

#### 【正】

AD0CON1 レジスタのSCAN1~SCAN0 ビットと AD0CON2 レジスタのAPS1~APS0 ビットで選択した<mark>複数の</mark>端子の入力電圧を1回ずつ変換する

### •Page 321 of 647

18.1.4項本文を以下のとおり変更いたします。

### 【誤】

選択した端子の入力電圧を繰り返しA/D変換するモードです。表 18.5 に繰り返し掃引モード0の仕様を示します。

#### 【正】

選択した<mark>複数の</mark>端子の入力電圧を繰り返し変換するモードです。表 18.5 に繰り返し掃引モード0の仕様を示します。

### •Page 321 of 647

表18.5の機能の仕様欄を以下のとおり変更いたします。

#### 【誤】

AD0CON1 レジスタの SCAN1~SCAN0 ビットと AD0CON2 レジスタの APS1~APS0 ビットで選択した端子の入力電圧を繰り返し A/D 変換する

### 【正】

AD0CON1 レジスタのSCAN1~SCAN0 ビットとAD0CON2 レジスタのAPS1~APS0 ビットで選択した複数の端子の入力電圧を繰り返し変換する

### •Page 322 of 647

18.1.5項本文を以下のとおり変更いたします。

### 【誤】

選択した端子に重点をおいて8本の端子の入力電圧を繰り返しA/D変換するモードです。表 18.6に繰り返し掃引モード1の仕様を示します。

#### 【正】

選択した  $1\sim4$  本の端子に重点をおいて、8 本の端子の入力電圧を繰り返し変換するモードです。表 18.6 に繰り返し掃引モード1 の仕様を示します。

### •Page 322 of 647

表18.6の機能の仕様欄を以下のとおり変更いたします。

### 【誤】

AD0CON1 レジスタの SCAN1~SCAN0 ビットと AD0CON2 レジスタの APS1 ~APS0 ビットで選択した端子 に重点をおいて、8端子を繰り返しA/D変換する

#### 【正】

AD0CON1レジスタのSCAN1~SCAN0ビットとAD0CON2レジスタのAPS1~APS0ビットで選択した1~4本 の端子に重点をおいて、8本の端子の入力電圧を繰り返し変換する

### •Page 322 of 647

表18.6の項目名を以下のとおり変更いたします。

【誤】

重点的に行う端子

【正】

重点的にA/D変換を行う端子

### •Page 334 of 647

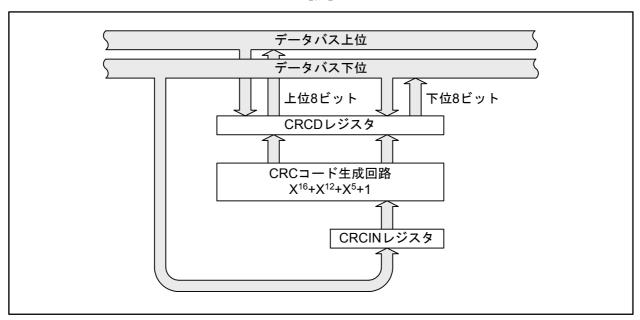

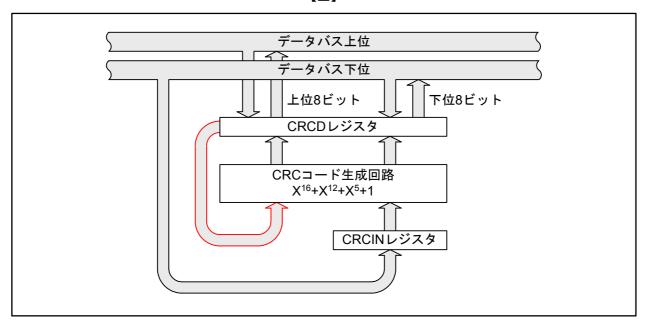

図20.1を以下のとおり訂正いたします。

### 【誤】

図20.1 CRC演算回路のブロック図

### 【正】

図20.1 CRC演算回路のブロック図

### •Page 348 of 647

図22.8の注3を以下のとおり削除いたします。

【誤】

注3. ゲート機能解除後、GOCビットは"0"になります。

【正】

―なし―

### •Page 349 of 647

図22.10のレジスタシンボルの一部を以下のとおり訂正いたします。

【誤】

G2TM6, G3TM7

【正】

G2TM6, G2TM7

### •Page 381 of 647

図23.3の機能欄のビット表記を以下のとおり訂正いたします。

【誤】

b6 b5 b4

【正】

b2 b1 b0

### •Page 467 of 647

25.1.9.5項本文の3段落目を以下のとおり訂正いたします。

#### 【誤】

オーバライトモードとオーバランモードの両方において、EOF の6番目のビットに続くfCAN (CAN システムクロック)の5サイクルの間は、MSGLOST ビットはプログラムで"0"を書いても"0"になりません。

### 【正】

オーバライトモードとオーバランモードの両方において、EOFの6番目のビットに続く周辺バスクロック5サイクルの間は、MSGLOSTビットはプログラムで"0"を書いても"0"になりません。

#### •Page 471 of 647

25.1.10.3項本文の3段落目を以下のとおり訂正いたします。

#### 【誤】

オーバランモードとオーバライトモードのどちらも、受信 FIFO がフルでメッセージの受信が決定している場合、ハードウェアプロテクトにより EOFの6番目のビットに続く fCAN (CAN システムクロック)の5サイクルの間は、プログラムで"0"(受信 FIFO メッセージロスト未発生)になりません。

#### 【正】

オーバランモードとオーバライトモードのどちらも、受信 FIFO がフルでメッセージの受信が決定している場合、ハードウェアプロテクトにより EOF の6番目のビットに続く周辺バスクロック5サイクルの間は、プログラムで"0"(受信 FIFO メッセージロスト未発生)になりません。

### •Page 481 of 647

図25.19の(b6-b5)の機能欄から以下のとおり文章を一部削除いたします。

#### (誤)

何も配置されていない。書く場合、"0"を書いてください。 読んだ場合、その値は"0"

#### 【正】

何も配置されていない。読んだ場合、その値は"0"

### Page 489 of 647

25.1.20.8項 BLIF ビットの説明を以下のとおり訂正、加筆いたします(TN-16C-A229A/J 参照)。

#### 【誤】

CANモジュールがCANオペレーションモードの間、CANバス上に32の連続するドミナントビットを検出すると、"1"になります。

"1"になった後、以下のどちらかで再検出します。

- •このビットを"1"から"0"にした後、レセシブビットを検出

- このビットを"1"から"0"にした後、CANリセットモードもしくはCAN Haltモードに遷移し、再度 CANオペレーションモードに遷移

### 【正】

CANモジュールがCANオペレーションモードの間、CANバス上に32の連続するドミナントビットを検出すると、"1"になります。

"1"になった後、以下のいずれかの条件が成立するとバスロックを再検出できるようになります。

- このビットを"1"から"0"にした後、レセシブビットを検出(バスロック解消)

- このビットを"1"から"0"にした後、CANリセットモードに遷移し、再度CANオペレーションモードに遷移(内部リセット)

### •Page 498 of 647

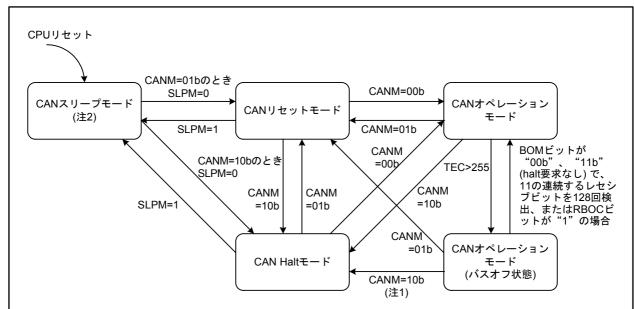

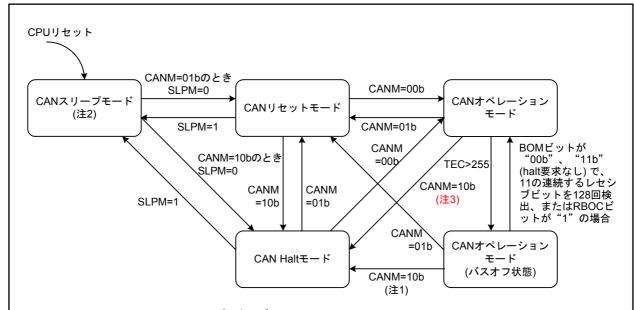

図25.34 に以下のとおり注3を追加いたします(TN-16C-A229A/J参照)。

### 【誤】

CANM, SLPM, BOM, RBOC: CiCTLRレジスタのビット

注1. バスオフ状態からCAN Haltモードへの遷移タイミングは、BOMビットの設定に依存します。 BOMビットが"01b"のとき、状態遷移のタイミングはバスオフ状態への遷移直後になります。 BOMビットが"10b"のとき、状態遷移のタイミングはバスオフ状態終了時になります。 BOMビットが"11b"のとき、状態遷移のタイミングはCANMビットが"10b"(CAN Haltモード)の設定時になります。

注2. CANスリープモードを設定/解除する場合は、SLPMビットを変更してください。

#### 図25.34 CAN動作モード間の遷移 (i=0~3)

#### 【正】

CANM, SLPM, BOM, RBOC: CiCTLRレジスタのビット

- 注1. バスオフ状態からCAN Haltモードへの遷移タイミングは、BOMビットの設定に依存します。 BOMビットが"01b"のとき、状態遷移のタイミングはバスオフ状態への遷移直後になります。 BOMビットが"10b"のとき、状態遷移のタイミングはバスオフ状態終了時になります。 BOMビットが"11b"のとき、状態遷移のタイミングはCANMビットを"10b"(CAN Haltモード)にしたときになります。

- 注2. CANスリープモードを設定/解除する場合は、SLPMビットを変更してください。

- 注3. CANバスがドミナントレベルでロックされている間は、CAN Haltモードに遷移しません。その場合は、CANリセットモードに遷移してください。

### 図25.34 CAN動作モード間の遷移 (i=0~3)

### •Page 500 of 647

表25.9 を以下のとおり加筆、訂正いたします(TN-16C-A229A/J 参照)。

【誤】 表 25.9 CAN リセットモードと CAN Haltモードでの動作

| モード      | 受信               | 送信               | バスオフ                          |

|----------|------------------|------------------|-------------------------------|

| CANリセット  | メッセージ受信の終了を待     | メッセージ送信の終了を      | バスオフ復帰 <mark>の終了</mark> を待たずに |

| モード      | たずにCANリセットモード    | 待って CAN リセットモード  | CANリセットモードに遷移                 |

|          | に遷移              | に遷移(注1、4)        |                               |

| CAN Halt | メッセージ受信の終了を      | メッセージ送信の終了を      | 【BOMビットが"00b"の場合】             |

| モード      | 待ってCAN Haltモードに遷 | 待ってCAN Haltモードに遷 | バスオフ復帰後のみ、プログ                 |

|          | 移(注2、3)          | 移(注1、4)          | ラムのHalt要求を受け付ける               |

|          |                  |                  | 【BOM ビットが"01b"の場合】            |

|          |                  |                  | バスオフ復帰 <mark>の終了</mark> を待たず  |

|          |                  |                  | に自動的にCAN Haltモード              |

|          |                  |                  | に遷移(プログラムのHalt要               |

|          |                  |                  | 求とは無関係に)                      |

|          |                  |                  | 【BOMビットが"10b"の場合】             |

|          |                  |                  | バスオフ復帰 <mark>の終了</mark> を待って  |

|          |                  |                  | 自動的にCAN Haltモードに              |

|          |                  |                  | 遷移(プログラムのHalt要求               |

|          |                  |                  | とは無関係に)                       |

|          |                  |                  | 【BOMビットが"11b"の場合】             |

|          |                  |                  | -<br>バスオフ中にプログラムによ            |

|          |                  |                  | るHalt要求があると、CAN               |

|          |                  |                  | Haltモードに遷移(バスオフ               |

|          |                  |                  | 復帰の終了を待たずに)                   |

BOMビット: CiCTLR レジスタのビット(i=0~3)

- 注1. いくつかのメッセージが送信要求されている場合、最初の送信完了後にモードを遷移します。サス ペンドトランスミッション中に CAN リセットモードが要求されている状態では、バスアイドルに なったとき、次の送信が終了したとき、またはCANモジュールが受信になったときに、モードを遷 移します。

- 注2. CAN バスがドミナントレベルでロックされた場合、CiEIFR レジスタの BLIF ビットをモニタすると、 プログラムはバスロック状態を検出できます。

- 注3. CAN Haltモードが要求された後、受信中にCANバスエラーが発生すると、CAN Haltモードに遷移し

- 注4. CAN リセットモードまたは CAN Halt モードが要求された後、送信中に CAN バスエラーまたは CAN アービトレーションロストが発生すると、要求されたCAN モードに遷移します。

【正】 表25.9 CAN リセットモードと CAN Haltモードでの動作

| モード      | 受信               | 送信                       | バスオフ               |

|----------|------------------|--------------------------|--------------------|

| CANリセット  | メッセージ受信の終了を待     | メッセージ送信の終了を              | バスオフ復帰を待たずにCAN     |

| モード      | たずにCANリセットモード    | 待って CAN リセットモード          | リセットモードに遷移         |

|          | に遷移              | に遷移(注1、4)                |                    |

| CAN Halt | メッセージ受信の終了を      | メッセージ送信の終了を              | 【BOMビットが"00b"の場合】  |

| モード      | 待ってCAN Haltモードに遷 | 待ってCAN Haltモードに遷         | バスオフ復帰後のみ、プログ      |

|          | 移(注2、3)          | 移(注1、 <mark>2、</mark> 4) | ラムのHalt要求を受け付ける    |

|          |                  |                          | 【BOMビットが"01b"の場合】  |

|          |                  |                          | バスオフ復帰を待たずに自動      |

|          |                  |                          | 的にCAN Haltモードに遷移(  |

|          |                  |                          | プログラムのHalt要求とは無    |

|          |                  |                          | 関係に)               |

|          |                  |                          | 【BOM ビットが"10b"の場合】 |

|          |                  |                          | バスオフ復帰を待って自動的      |

|          |                  |                          | にCAN Haltモードに遷移(プ  |

|          |                  |                          | ログラムのHalt要求とは無関    |

|          |                  |                          | 係に)                |

|          |                  |                          | 【BOMビットが"11b"の場合】  |

|          |                  |                          | バスオフ中にプログラムによ      |

|          |                  |                          | るHalt要求があると、CAN    |

|          |                  |                          | Haltモードに遷移(バスオフ    |

|          |                  |                          | 復帰を待たずに)           |

BOMビット: CiCTLR レジスタのビット(i=0~3)

- 注1. いくつかのメッセージ送信が要求されている場合、最初のメッセージ送信が完了した後にモードを 遷移します。サスペンドトランスミッション中に CAN リセットモードが要求されている状態では、 バスアイドルになったとき、次の送信が終了したとき、またはCANモジュールが受信になったとき に、モードを遷移します。

- 注2. CAN バスがドミナントレベルでロックされた場合、CiEIFR レジスタの BLIF ビットをモニタすると、 プログラムはバスロックを検出できます。CAN バスがドミナントレベルでロックされている間は、 CAN Haltモードに遷移しません。この場合は、CANリセットモードに遷移してください。

- 注3. CAN Haltモードが要求された後、受信中にCANバスエラーが発生すると、CAN Haltモードに遷移し ます (ただし、CAN バスがドミナントレベルでロックされている場合は、CAN Halt モードに遷移し ません)。

- 注4. CAN リセットモードまたは CAN Halt モードが要求された後、送信中に CAN バスエラーまたは CAN アービトレーションロストが発生すると、要求された動作モードに遷移します(ただし、CANバスが ドミナントレベルでロックされている場合は、CAN Haltモードに遷移しません)。

#### •Page 501 of 647

25.2.3項本文の1段落目を以下のとおり訂正いたします。

### 【誤】

CAN スリープモードは、CAN モジュールへのクロック供給を停止することによって、消費電流を低減するためのモードです。MCUのハードウェアリセットまたはソフトウェアリセット実行後、CAN スリープモードから動作を開始します。

### 【正】

CAN スリープモードは、CAN モジュールへのクロック供給を停止することによって、消費電流を低減するためのモードです。MCUのリセット後は、CAN スリープモードから動作を開始します。

### •Page 504 of 647

図25.36のPCDビット部のqの値を以下のとおり訂正いたします。

【誤】

q=1, 2, 3, 4

【正】

q=2, 3, 4

### •Page 516 of 647

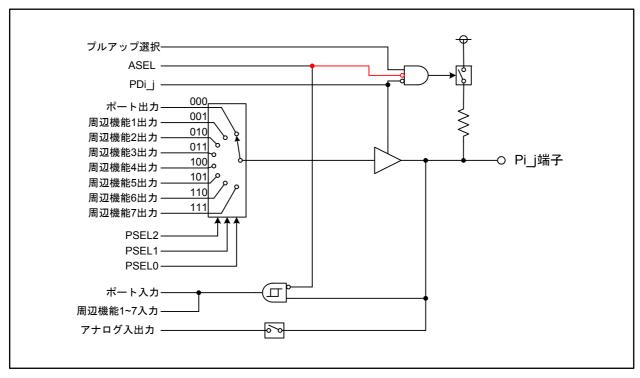

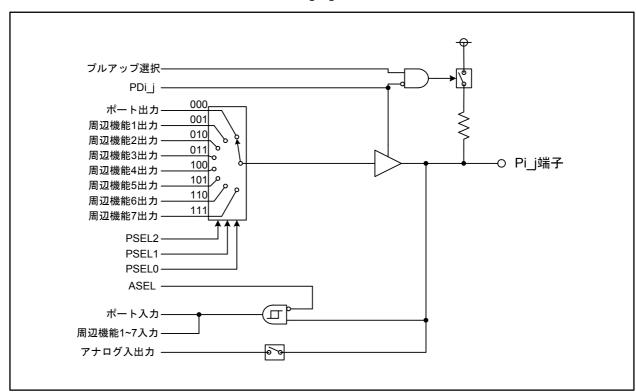

26章 章頭本文を以下のとおり訂正いたします(TN-16C-A199A/J参照)。

#### 【誤】

プルアップ抵抗は端子が出力になっている場合と、アナログ入出力になっている場合には、レジスタの設定内容にかかわらず切り離されます。

#### 【正】

プルアップ抵抗は、端子が出力になっている場合には、レジスタの設定内容にかかわらず切り離されます。

### •Page 516 of 647

図26.1を以下のとおり訂正いたします(TN-16C-A199A/J参照)。

### 【誤】

図26.1 入出力端子ブロック図(代表例)(i=0~15、j=0~7)

### 【正】

図26.1 入出力端子ブロック図(代表例)(i=0~15、j=0~7)

以上