# **RENESAS TECHNICAL UPDATE**

〒211-8668 神奈川県川崎市中原区下沼部1753 ルネサスエレクトロニクス株式会社 問合せ窓口 http://japan.renesas.com/inquiry

E-mail: csc@renesas.com

| 製品分類 |                               | MPU & MCU | 発行番号   | TN-16C-A206A/J |                                                | Rev. | 第1版      |

|------|-------------------------------|-----------|--------|----------------|------------------------------------------------|------|----------|

| 題名   | R32C/120グループ ハードウェアマニュアルの誤記訂正 |           | 情報分類   | 技術情報           |                                                |      |          |

| 適用製品 | R32C                          | /120グループ  | 対象ロット等 | 関連資料           | R32C/120グループ<br>ハードウェアマニコ<br>(RJJ09B0504-0110) | ェアルI | Rev.1.10 |

R32C/120 グループ ハードウェアマニュアル Rev.1.10 において誤記がありましたので、以下のとおり訂正いたします。

# 〈訂正内容〉

•Page 11 of 582

表1.7のクロック出力の機能を以下のとおり訂正いたします。

【誤】

fC、f8または、f32と同じ周期のクロックを出力します

[正]

低速クロック、f8または、f32と同じ周期のクロックを出力します

•Page 39 of 582

表4.20 IFSO レジスタのリセット後の値を以下のとおり訂正いたします。

【誤】

X000 X000b

【正】

X0X0 X000b

•Page 57, 58 of 582

表4.38、表4.39のレジスタ名を以下のとおり訂正いたします。

【誤】

CANOアクセプタンスマスクレジスタk

【正】

CAN0マスクレジスタk

| XXXX XX00b | 【誤】  |  |

|------------|------|--|

|            | [正]  |  |

| 0000 0000Ь | (11) |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

|            |      |  |

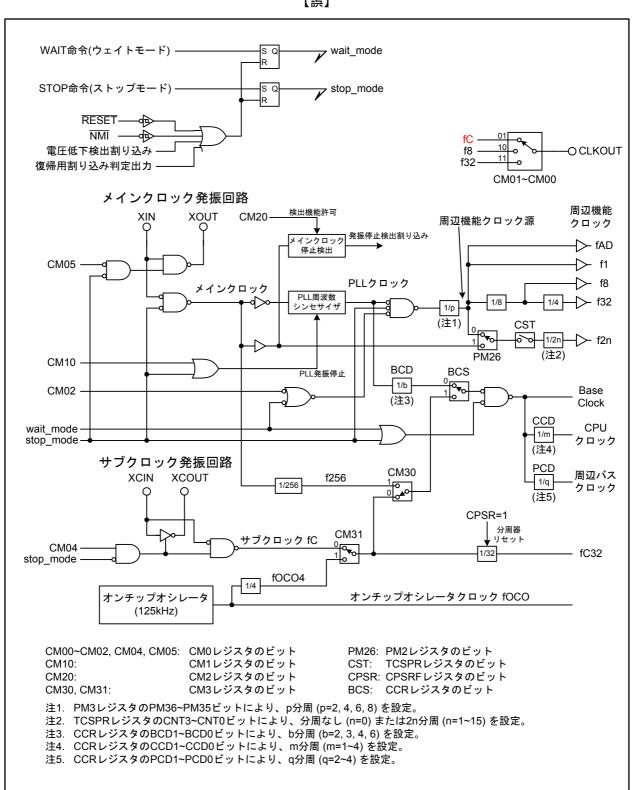

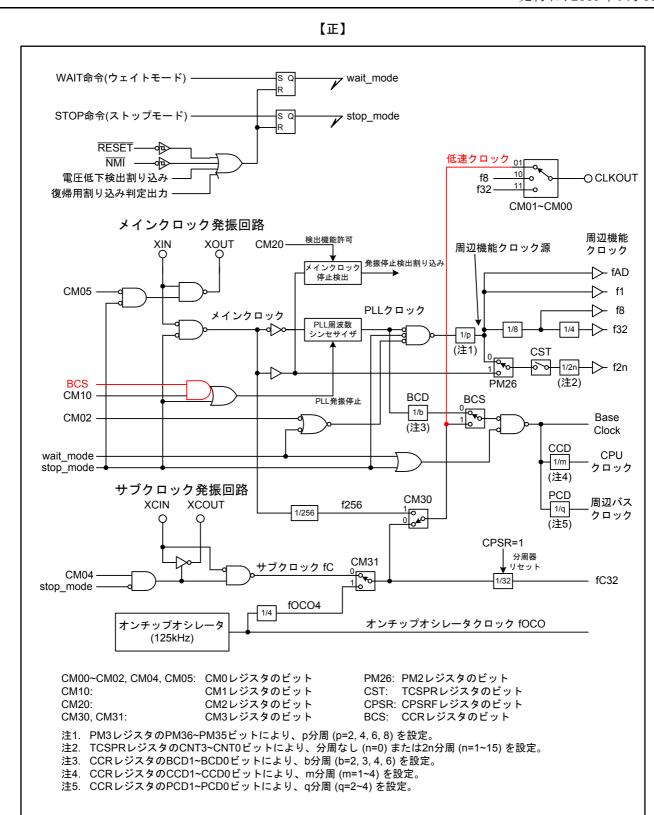

# •Page 72 of 582

図7.1を以下のとおり訂正いたします。

### 【誤】

#### クロック発生回路のブロック図 図7.1

図7.1 クロック発生回路のブロック図

#### •Page 73 of 582

図7.2の注2、注6の文章をそれぞれ以下のとおり訂正いたします。

#### 【誤】

- 注2. ベースクロック分周値と周辺バスクロック分周値は、同時に値を変更しないでください。同時に変更した場合、周辺バスクロックが動作上限周波数を越える場合があります。ベースクロックの周波数を上げる場合は、先に周辺バスクロック分周値を大きくした後、ベースクロック分周値を小さくしてください。

- 注6. これらの低速クロックの切り替えは、CM3レジスタのCM31~CM30ビットで行います。

#### (正)

- 注2. ベースクロック分周値と周辺バスクロック分周値は、同時に値を変更しないでください。同時に変更した場合、周辺バスクロックが動作上限周波数を越える場合があります。

- 注6. これらの低速クロックの切り替えは、CM3 レジスタのCM31~CM30 ビットで行います。先に CM31~CM30 ビットでいずれかのクロックを選択した後、このビットを"1"にしてください。

# •Page 74, 87, 94, 97 of 582

図7.3のCM01~CM00ビットの機能欄、7.6本文、表7.3、表7.4、表7.6のfCをそれぞれ以下のとおり訂正いたします。

#### 【誤】

図7.3: fCを出力

7.6: **fC**、f8、またはf32をCLKOUT端子から出力できます。

表7.3: fCを出力 表7.4: fC選択時 表7.6: fC選択時

#### 【正】

図7.3: 低速クロックを出力

7.6: **低速**クロック、f8、またはf32をCLKOUT端子から出力できます。

表7.3: 低速クロックを出力 表7.4: 低速クロック選択時 表7.6: 低速クロック選択時

# •Page 74 of 582

図7.3のCM06ビットに対し、以下の注記を追加いたします。

#### 【誤】

一なし―

# 【正】

注7. このビットはウォッチドッグタイマを動作させる前に設定してください。動作中に書き換える場合は、WDTSレジスタに書いた直後に実施してください。

#### •Page 75 of 582

図7.4の注2の文章を以下のとおり訂正いたします。

# 【誤】

注2. CCR レジスタのBCS ビットが"0"(ベースクロック源はPLLクロック)の場合、CM10 ビットを"1" にすることはできません。

#### 【正】

注2. CCR レジスタのBCS ビットが"0"(ベースクロック源はPLLクロック)の場合、CM10 ビットを"1" にしても PLL 周波数シンセサイザの発振は停止しません。

# •Page 75 of 582

図7.4のCM15ビットに対し、以下の注記を追加いたします。

【誤】

一なし—

#### 【正】

注4. メインクロックを停止させると"1"になります。"0"にするときは、メインクロックの発振が十分安定してから実施してください。

# •Page 76 of 582

図7.6の注1に以下のとおり文章を追記いたします。

# 【誤】

注1. このレジスタはPRCR2レジスタのPRC27ビットを"1"(書き込み許可)にした後で書き換えてください。

#### 【正】

注1. このレジスタはPRCR2レジスタのPRC27ビットを"1"(書き込み許可)にした後で書き換えてください。また、CCRレジスタのBCSビットが"0"(PLLクロック)のときに書き換えてください。

# •Page 77 of 582

図7.9の注3内の記述を以下のとおり訂正いたします。

#### 【誤】

CM0レジスタのCM05ビット(メインクロックは停止しない) CM1レジスタのCM10ビット(PLLは停止しない)

#### (正)

CM0 レジスタの CM05 ビット(メインクロックの発振/停止) CM1 レジスタの CM10 ビット(PLLの発振/停止)

#### •Page 77 of 582

図7.9のPM26ビットに対し、以下の注記を追加いたします。

【誤】

一なし一

#### 【正】

注6. このビットを変更するときは、f2nを使用するすべての周辺機能を停止してから書き換えてくださ V10

# •Page 78 of 582

図7.10の注1に以下のとおり文章を追記いたします。

#### 【誤】

注1. このレジスタはPRCRレジスタのPRC0ビットを"l"(書き込み許可)にした後で書き換えてくださ い。

#### 【正】

注1. このレジスタはPRCRレジスタのPRC0ビットを"1"(書き込み許可)にした後で書き換えてくださ い。また、fAD、f1、f8、f32、クロック源に周辺機能クロック源を選択したf2nを使用するすべての 周辺機能を停止してから書き換えてください。

# •Page 82 of 582

図7.15のSEOビットのビット名と機能欄をそれぞれ以下のとおり訂正いたします。

【誤】

ビット名: 自励発振モード設定ビット 機能欄: 0:メインクロック逓倍モード

1: 自励発振モード

【正】

ビット名: 自励発振動作設定ビット 機能欄: 0:メインクロック逓倍動作

1: 自励発振動作

# •Page 82 of 582

図7.16のPLSレジスタに対し、以下の注記を追加いたします。

【誤】

―なし―

#### 【正】

注1. このレジスタはPLC1 レジスタのSEO ビットを"1"(自励発振動作)にするとリセットされます。な お、メインクロックを停止させたり、PLLを停止させたりした場合、レジスタの更新も停止します。

# •Page 85 of 582

7.2.1項本文2段落目に以下のとおり文章を追記いたします。

### 【誤】

発振停止検出後、メインクロックの発振が再開した場合、PLL周波数シンセサイザの発振が安定するまでに一時的にPLLクロック周波数が設定周波数を超える場合があります。発振停止を検出した後は、速やかにプログラムでベースクロックの分周比(CCRレジスタのBCD1~BCD0ビットで設定)と、周辺機能クロック源の分周比(PM3レジスタのPM36~PM35ビットで設定)を上げてください。

#### 【正】

発振停止検出後、メインクロックの発振が再開した場合、PLL周波数シンセサイザの発振が安定するまでに一時的にPLLクロック周波数が設定周波数を超える場合があります。発振停止を検出した後は、速やかにプログラムでメインクロックの再発振を抑止する(CM0レジスタのCM05ビットを"1"にする)か、ベースクロックの分周比(CCRレジスタのBCD1~BCD0ビットで設定)と周辺機能クロック源の分周比(PM3レジスタのPM36~PM35ビットで設定)を上げてください。

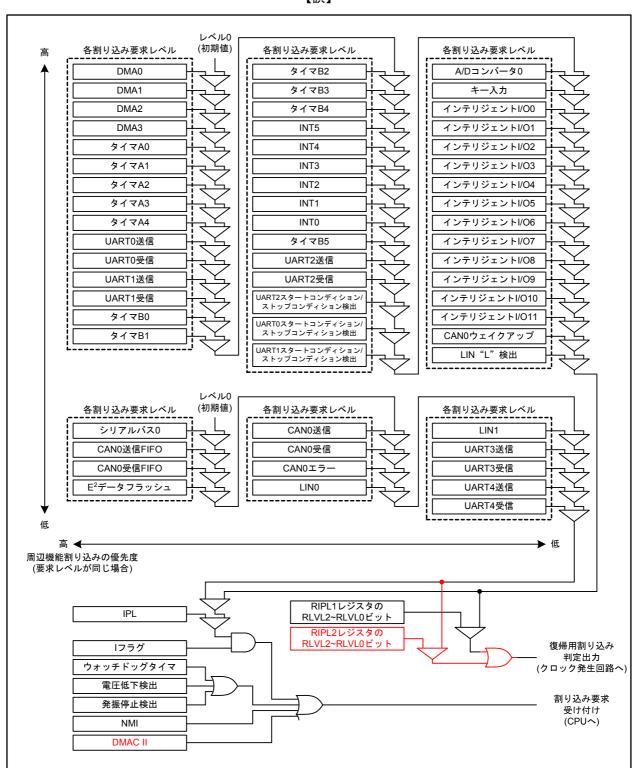

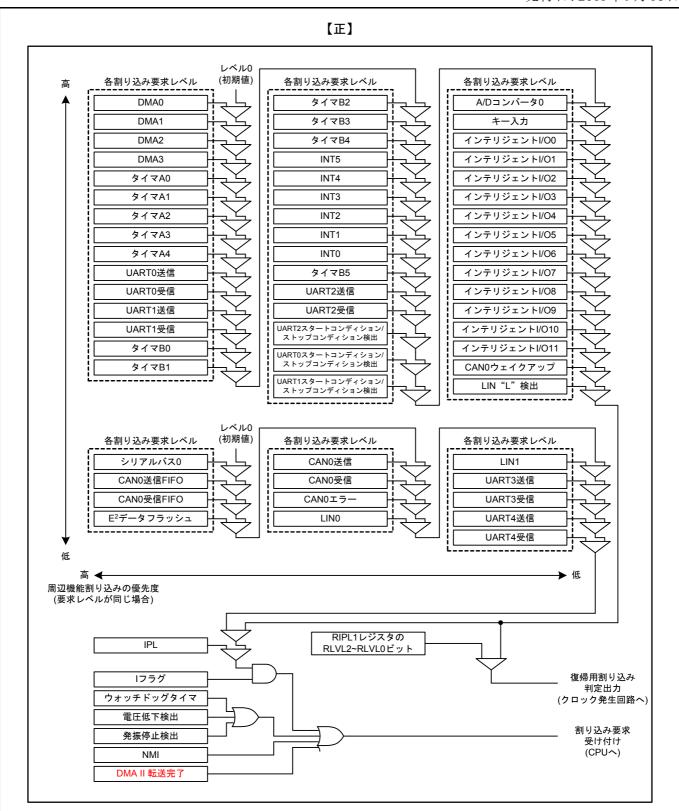

# •Page 123 of 582

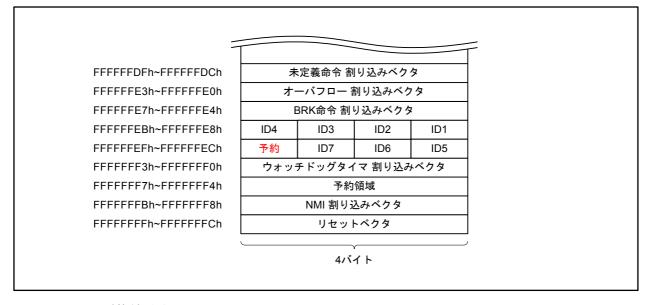

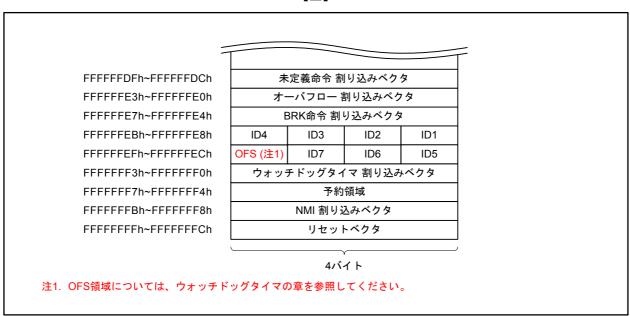

図10.8を以下のとおり訂正いたします。

# 【誤】

図7.1 割り込み優先順位判定回路

図7.1 割り込み優先順位判定回路

# •Page 128 of 582

図10.14の(b0)の機能欄から以下のとおり文章を一部削除いたします。

# 【誤】

何も配置されていない。書く場合、"0"を書いてください。 読んだ場合、その値は"1"

#### 【正】

何も配置されていない。読んだ場合、その値は"1"

# •Page 128 of 582

図10.14の注3を以下のとおり訂正いたします。

#### 【誤】

注3. 該当ビットに機能が割り当てられている場合、"0"のみ書けます。"1"を書いても変化しません。"0"を書く場合、AND命令またはBCLR命令を使用してください。

#### 【正】

注3. 該当ビットに機能が割り当てられている場合、"0"のみ書けます。"1"は書かないでください。"0"を書く場合、AND命令またはBCLR命令を使用してください。

# •Page 132 of 582

図11.2の(b4-b0)に対し、以下の注記を追加いたします。

【誤】

―なし―

#### 【正】

注1. カウントソースにオンチップオシレータを使用している場合、読み出し中にカウント値が変わり不定値が読めることがあります。

# •Page 134 of 582

図11.5の注3に以下のとおり文章を追記いたします。

#### 【誤】

注3. WDTONビットが"1"の場合、これらの設定は無効です。

#### 【正】

注3. WDTONビットが"1"の場合、これらの設定は無効です。WDTONビットが"0"の場合、これらのビットに設定した値がWDKレジスタ、PM2レジスタに反映されます。

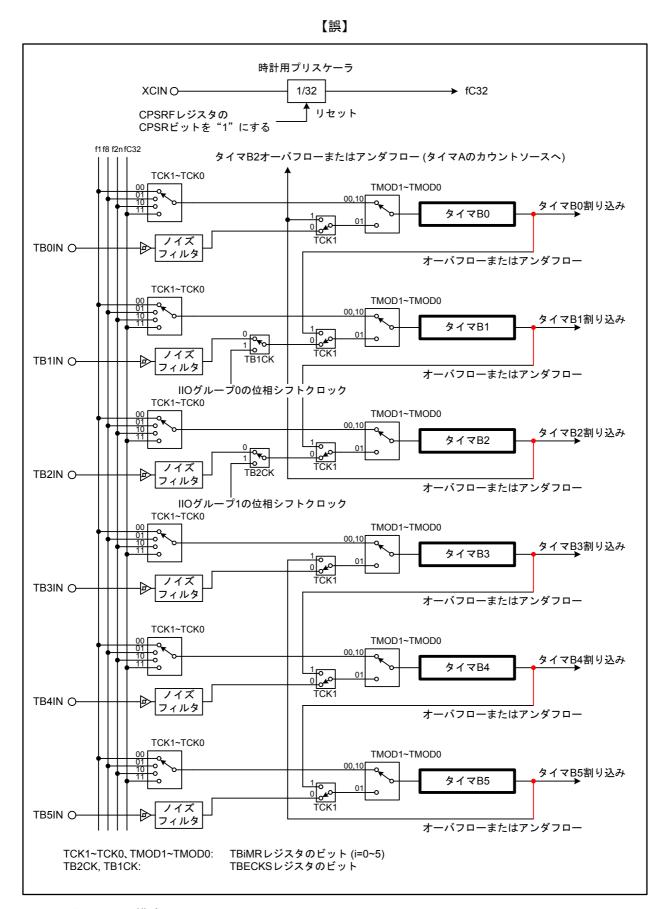

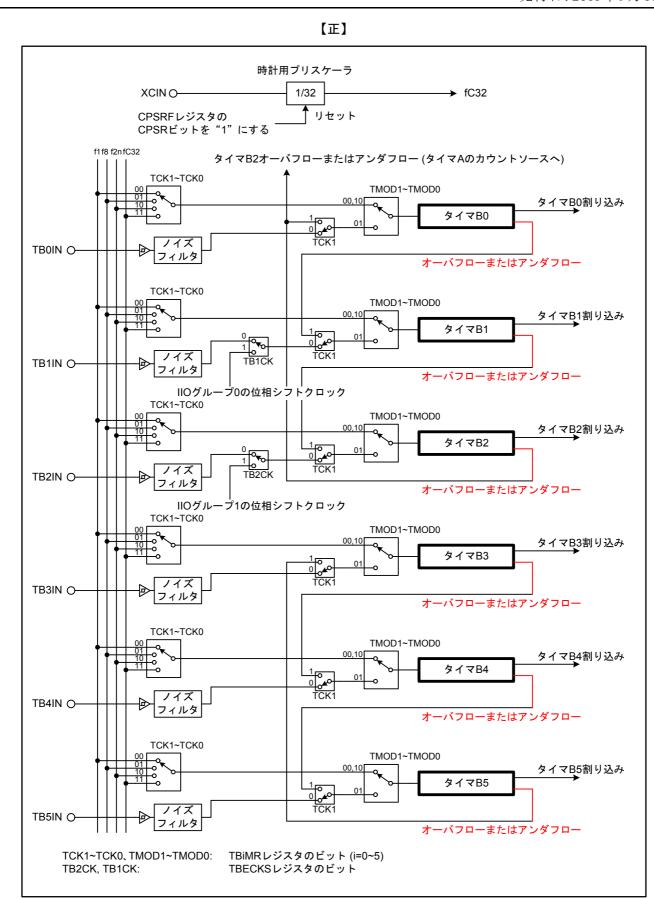

# •Page 164 of 582

図15.2を以下のとおり訂正いたします。

図15.2 タイマBの構成

図15.2 タイマBの構成

#### •Page 198, 202 of 582

図16.3のINV13ビットの機能欄、図16.9のPWCONビットの機能欄をそれぞれ以下のとおり訂正いたします。

# 【誤】

INV13: タイマAリロード制御信号が...

PWCON: 奇数回目のタイマA出力

# 【正】

INV13: タイマA1 リロード制御信号が...

PWCON: タイマA1 リロード制御信号が"0"のときのタイマB2アンダフロー

#### •Page 202 of 582

図16.8のMR2ビットとMR3ビットの説明文を以下のとおり訂正いたします。

#### 【誤】

MR2: 三相モータ制御用タイマ機能では"0"にしてください

MR3: 何も配置されていない。書く場合、"0"を書いてください。読んだ場合、その値は不定

#### 【正】

MR2: 何も配置されていない。書く場合、"0"を書いてください。読んだ場合、その値は不定

MR3: 三相モータ制御用タイマ機能では無効。書く場合、"0"を書いてください。読んだ場合、その値は不定

# •Page 203 of 582

16.3本文の3段落目の一部を以下のとおり削除いたします。

# 【誤】

また三相モード1では、タイマB2割り込みごとにカウンタへのリロード値がTAi、TAi-1 (i=4, 1, 2)を入れ替わるため、タイマB2割り込みの頻度を半分に減らすことができます。このモードではTAi レジスタ設定値とTAi1 レジスタ設定値の合計がTB2 レジスタ設定値と一致するようにします。

#### 【正】

また三相モード1では、タイマB2割り込みごとにカウンタへのリロード値がTAi、TAi-1 (i=4, 1, 2)を入れ替わるため、タイマB2割り込みの頻度を半分に減らすことができます。

# •Page 208 of 582

図16.18の(1)の1項目目を以下のとおり訂正いたします。

#### (誤)

• INV01=0、ICTB2=2h (タイマB2アンダフロー 2回目ごとにタイマB2割り込み)、またはINV01=1、INV00=1、ICTB2=1h (タイマAリロード制御信号の立ち下がりでタイマB2割り込み)

#### 【正】

• INV01=0、ICTB2=2h (タイマB2アンダフロー 2回目ごとにタイマB2割り込み)、またはINV01=1、INV00=1、ICTB2=1h (タイマA1 リロード制御信号が"1"のときのタイマB2アンダフローごとにタイマB2割り込み)

#### •Page 210 of 582

16.6.1項本文を以下のとおり訂正いたします。

#### 【誤】

• PM2 レジスタの PM24 ビットが"1" (NMI 有効)で、INVC0 レジスタの INV03 ビットが"1" (三相 モータ制御用タイマ出力許可)かつ、INV02 ビットが"1" (三相モータ制御用タイマ機能を使用する)のとき、NMI端子に"L"を入力すると TA1OUT、TA2OUT、TA4OUT端子はハイインピーダンスになります。

#### 【正】

• PM2 レジスタの PM24 ビットが"1" (NMI 有効)、かつ IOBC レジスタの SDE ビットが"1" (シャット <mark>ダウン機能有効</mark>)で、INVC0 レジスタの INV02 ビットが"1" (三相モータ制御用タイマ機能を使用 する)、かつ INV03 ビットが"1" (三相モータ制御用タイマ出力許可)のとき、 NMI 端子に"L"を入力すると TA1OUT、TA2OUT、TA4OUT 端子はハイインピーダンスになります。

# •Page 210 of 582

16.6.2項本文を以下のとおり訂正いたします。

#### 【誤】

• タイマB2がオーバフローする前後で、TAi1 レジスタ (i=1, 2, 4)に値を設定しないでください。 TAi1 レジスタに値を設定する場合は、TB2 レジスタの値を読んで、オーバフローまでに十分な時間があることを確認してから設定してください。TB2 レジスタの読み出しと、TAi1 レジスタへの書き込みの間隔が開かないよう、この間に割り込み処理などが実行されないようにしてください。また、TB2 レジスタを読み出した結果、オーバフローまでに十分な時間がない場合は、オーバフローするまで待った後 TAi1 レジスタを設定してください。

#### 【正】

• タイマB2がアンダフローする前後で、TAi1 レジスタ(i=1,2,4)に値を設定しないでください。 TAi1 レジスタに値を設定する場合は、TB2 レジスタの値を読んで、アンダフローまでに十分な時間があることを確認してから設定してください。TB2 レジスタの読み出しと、TAi1 レジスタへの書き込みの間隔があかないよう、この間に割り込み処理などが実行されないようにしてください。また、TB2 レジスタを読み出した結果、アンダフローまでに十分な時間がない場合は、アンダフローするまで待った後 TAi1 レジスタを設定してください。

# •Page 228 of 582

図17.18の波形の名称を以下のとおり訂正いたします。

【誤】

•UiC0レジスタのTXEPTフラグ

【正】

•UiC0レジスタのTXEPTビット

# •Page 228 of 582

図17.18の設定条件記載箇所の4項目目を以下のとおり訂正いたします。

# 【誤】

• UiC1 レジスタ、U34CON レジスタのUiRS ビット=0 (UiTB レジスタ空で割り込み要求発生)

# 【正】

•UiC1 レジスタ、U34CON レジスタのUiIRS ビット=0 (UiTB レジスタ空で割り込み要求発生)

# •Page 272, 273 of 582

表18.7、表18.8の開始条件の仕様に、以下のとおり1項目追加いたします。

【誤】

一なし―

【正】

•TRG1、TRG0ビットが"10b" ADSTビットを"1"にした後、タイマAO割り込み要求が発生したとき

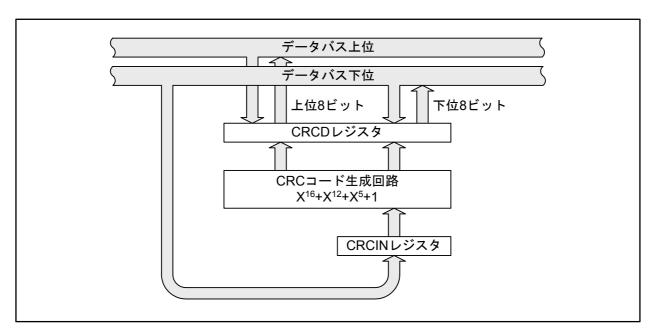

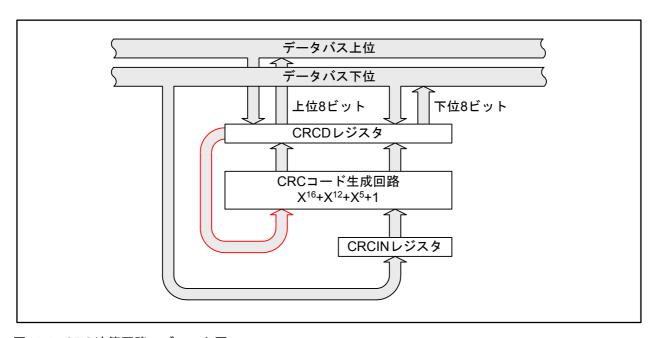

# •Page 283 of 582

図20.1を以下のとおり訂正いたします。

# 【誤】

図20.1 CRC演算回路のブロック図

# 【正】

図20.1 CRC演算回路のブロック図

# •Page 291, 292 of 582

図22.1左上の「 $\overline{\text{INT0}}$ 端子からの要求」、図22.2左上の「 $\overline{\text{INT1}}$ 端子からの要求」をそれぞれ以下のとおり訂正 いたします。

【誤】

図22.1: INTO端子からの要求 図22.2: INTI端子からの要求

【正】

図22.1: INTO端子またはINTI端子からの要求 図22.2: INTO端子またはINTI端子からの要求

# •Page 294 of 582

図22.5のRST2ビットの機能を以下のとおり訂正いたします。

【誤】

1: INTi 端子への"L"入力でベースタイマリセットする

(正)

1: INTO/INT1 端子への"L"入力でベースタイマをリセットする

# •Page 294 of 582

図22.5の注3を以下のとおり訂正いたします。

#### 【誤】

注3. グループ0の場合 $\overline{\text{INTO}}$ 端子、グループ1の場合 $\overline{\text{INTI}}$ 端子に"L"を入力するとベースタイマリセットをします。

#### 【正】

注3. IFS2レジスタでUDiZ信号用に選択した外部割り込み入力端子に"L"を入力するとベースタイマをリセットをします。

# •Page 295 of 582

図22.6の注3を以下のとおり削除いたします。

【誤】

注3. ゲート機能解除後、GOCビットは"0"になります。

【正】

一なし―

# •Page 301 of 582

表22.2のベースタイマリセット条件の仕様の一部を以下のとおり訂正いたします。

【誤】

•外部割り込み端子に"L"を入力

グループ0: INTO端子 グループ1: INTI端子

【正】

外部割り込み端子(INTOまたはINTI)に"L"を入力 グループ0: IFS2 レジスタのIFS23~IFS22 ビットで選択 グループ1: IFS2 レジスタのIFS27~IFS26 ビットで選択

# •Page 302 of 582

図22.15の入力信号の一部を以下のとおり訂正いたします。

【誤】

INTi端子に"L"を入力

【正】

INTO/INT1端子に"L"を入力

# •Page 328 of 582

図23.3の機能欄のビット表記を以下のとおり訂正いたします。

【誤】

b6 b5 b4

【正】

b2 b1 b0

# •Page 362 of 582

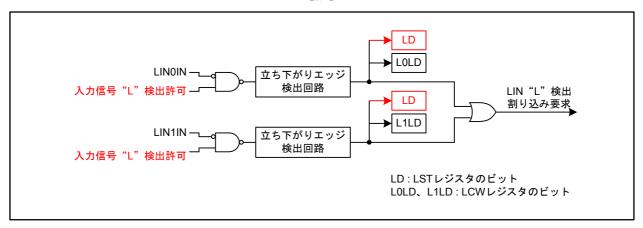

図24.3のLOLD、L1LDビットに対し、以下の注記を追加いたします。

【誤】

―なし―

【正】

注1. これらのビットのうち1つでも"1"になっている場合、新たな入力信号"L"検出割り込みは発生しません。

#### •Page 364 of 582

図24.7の注4の文章を以下のとおり訂正いたします。

#### 【誤】

注4. 入力信号の立ち下がりを検出すると、LST レジスタのLD ビットが"1"になり、割り込みが発生します。なお、LD ビットが"1"のときにこのビットを"0"にしても、LD ビットは"0"になりません。

#### 【正】

注4. このビットが"1"のときに入力信号の立ち下がりを検出した場合、または入力信号が"L"のときにこのビットを"1"にした場合、LSTレジスタのLDビットが"1"になり、割り込み要求が発生します。

# •Page 371 of 582

図24.16のLDビットに対し、以下の注記を追加いたします。

【誤】

一なし一

#### [正]

注3. このビットが"1"の場合、他チャネルのLDビットが"1"になっても、あるいは新たに自チャネルで LDビットが"1"になる条件が整ったとしても、新たな割り込み要求は発生しません。

# •Page 375 of 582

表24.3(1)のソフトウェア処理の4項目目を以下のとおり訂正いたします。

#### [担]

• LBRK レジスタのBFTL3~BFTL0 ビットでブレーク幅(13~28 Tbit)、BFTD1~BFTD0 ビットでブレークデリミタ幅(1~4 Tbit)を設定

#### 【正】

• LBRK レジスタのBLT3~BLT0 ビットでブレーク幅(13~28 Tbit)、BDT1~BDT0 ビットでブレークデリミタ幅(1~4 Tbit)を設定

#### •Page 376 of 582

表24.4(4)のLINモジュール処理の一部を以下のとおり訂正いたします。

# 【誤】

インタバイトスペース送信

(LRFC レジスタの RFDL3~RFDL0 ビットで指定したデータ長分繰り返し。LEST レジスタの BER=1 (ビットエラー検出)なら中断。エラー発生時には、(5)のチェックサム送信は実行しません)

# 【正】

インタバイトスペース送信

(LRFC レジスタの RFDL3~RFDL0 ビットで指定したデータ長分繰り返す。エラー発生時は(6)へ)

# •Page 377 of 582

表24.5(4)のLINモジュール処理の一部を以下のとおり訂正いたします。

# 【誤】

スタートビット検出によりデータ3受信

(LRFC レジスタのRFDL3~RFDL0 ビットで指定したデータ長分繰り返し。LEST レジスタのいずれかの ビットが"1"(何らかのエラー検出)なら中断。エラー発生時には、(5)のチェックサム判定は実施しま せん)

# 【正】

スタートビット検出によりデータ3受信

(LRFCレジスタのRFDL3~RFDL0ビットで指定したデータ長分繰り返す。エラー発生時は受信を中断し て(5)へ。ただしその場合は、(5)のチェックサム判定は実施しません)

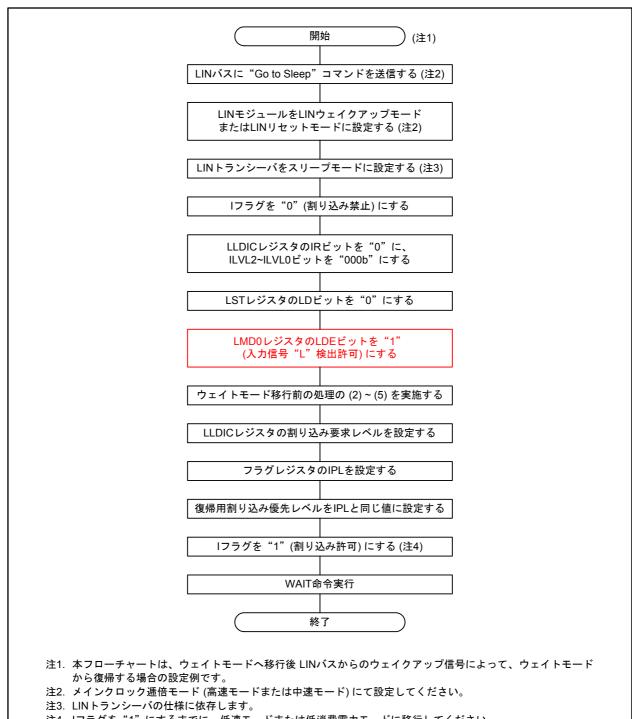

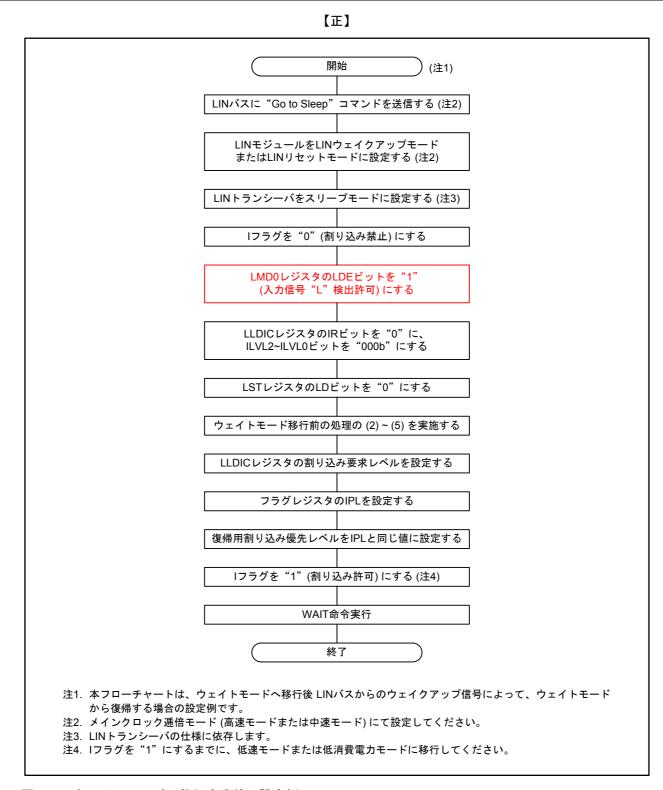

### •Page 386 of 582

図24.30を以下のとおり訂正いたします。

### 【誤】

注4. Iフラグを"1"にするまでに、低速モードまたは低消費電力モードに移行してください。

図24.30 ウェイトモードへ遷移する前の設定例

図24.30 ウェイトモードへ移行する前の設定例

### •Page 387 of 582

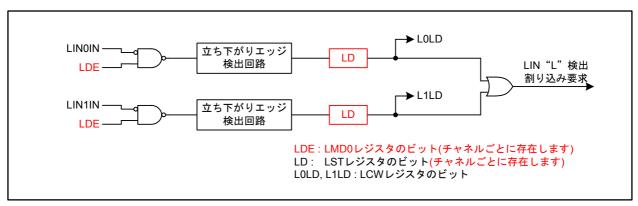

表24.8の入力信号"L"検出の条件欄に以下のとおり文章を追記いたします。

#### 【誤】

LMD0レジスタのLDEビットが"1"(入力信号"L"検出許可)で、LINjIN端子からの入力信号の立ち下がりエッジを検出したとき

#### 【正】

LMD0レジスタのLDEビットが"1"(入力信号"L"検出許可)のとき、LINjIN端子からの入力信号の立ち下がりエッジを検出した、またはLINjIN端子が"L"のときにLDEビットを"1"にした

# •Page 390 of 582

24.11の本文9~10行目に以下のとおり文章を追記いたします。

### 【誤】

ぞれぞれの割り込み要求は、LMD0レジスタの対応するビットが"1"(割り込み許可)のときに、LSTレジスタの対応するフラグが"1"になると出力されます。

#### 【正】

ぞれぞれの割り込み要求は、LMD0レジスタの対応するビットが"1"(割り込み許可)のときに、LSTレジスタの対応するフラグが"1"になると出力されます。なお、複数の要因の論理和をとっているため、いずれかの要因が"1"であると他の要因による新たな割り込み要求は発生しません。

# •Page 390 of 582

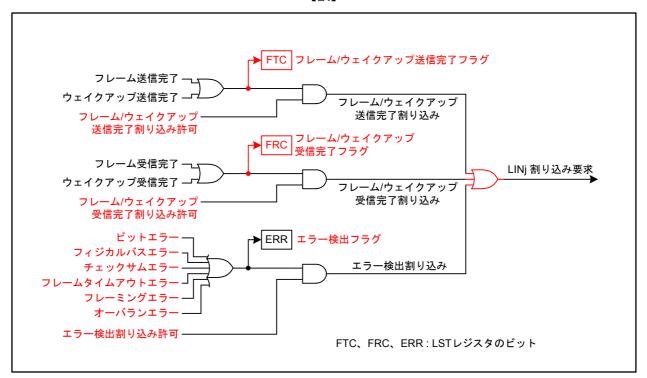

図24.32を以下のとおり訂正いたします。

### 【誤】

図24.32 LINj割り込みブロック図(j=0, 1)

### 【正】

図24.32 LINj割り込みブロック図(j=0, 1)

# •Page 390 of 582

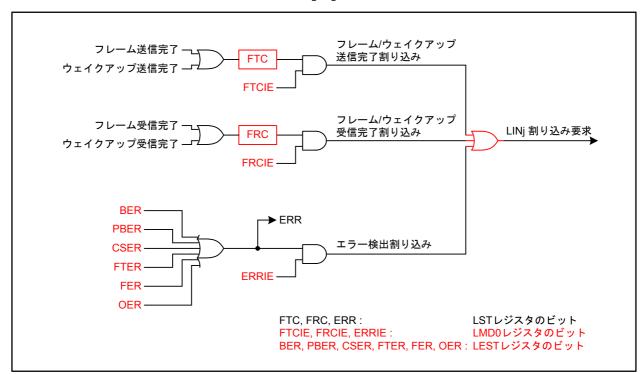

図24.33を以下のとおり訂正いたします。

# 【誤】

図24.33 LIN"L" 検出割り込みブロック図

# 【正】

図24.33 LIN"L" 検出割り込みブロック図

### •Page 391 of 582

25 本文の4行目を以下のとおり訂正いたします。

# 【誤】

表25.1にCANモジュールの仕様、図25.1にCANモジュールブロック図を示します。

#### 【正】

表25.1、表25.2にCANモジュールの仕様、図25.1にCANモジュールブロック図を示します。

# •Page 415 of 582

図25.11の注2を以下のとおり訂正いたします。

#### 【誤】

注2. RFMLFビットと同時にRFEビットに"0"を書いてください。

#### 【正】

注2. RFEビットを"0"にするときは、RFMLFビットも同時に"0"にしてください。

### Page 426 of 582

図25.19の(b6-b5)の機能欄から以下のとおり文章を一部削除いたします。

#### 【誤】

何も配置されていない。書く場合、"0"を書いてください。 読んだ場合、その値は"0"

#### 【正】

何も配置されていない。読んだ場合、その値は"0"

# •Page 437 of 582

図25.28の注4を以下のとおり訂正いたします。

# 【誤】

注4. 同時に1つ以上のエラー条件が検出された場合は、関係するすべてのビットが"1"になります。

#### 【正】

注4. 同時に2つ以上のエラーが検出された場合は、該当するすべてのビットが"1"になります。

#### •Page 446 of 582

25.2.3項本文を以下のとおり訂正いたします。

#### 【誤】

CANスリープモードは、CANモジュールへのクロック供給を停止することによって、消費電流を低 減するためのモードです。MCUのハードウェアリセットまたはソフトウェアリセット実行後、CANスリー プモードから動作を開始します。

#### 【正】

CANスリープモードは、CANモジュールへのクロック供給を停止することによって、消費電流を低 減するためのモードです。MCUのリセット後は、CANスリープモードから動作を開始します。

# •Page 449 of 582

図25.36のPCDビット部のqの値を以下のとおり訂正いたします。

【誤】

q=1, 2, 3, 4

【正】

q=2, 3, 4

# •Page 461 of 582

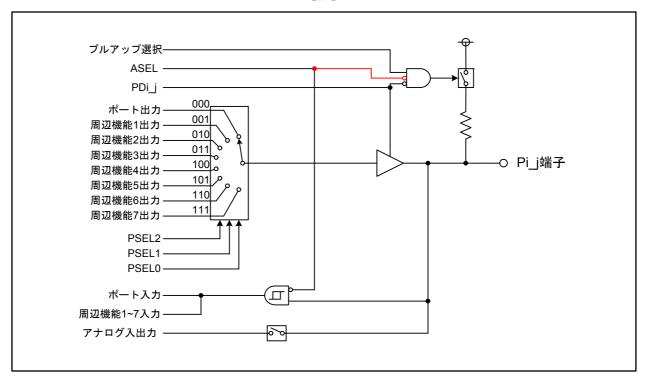

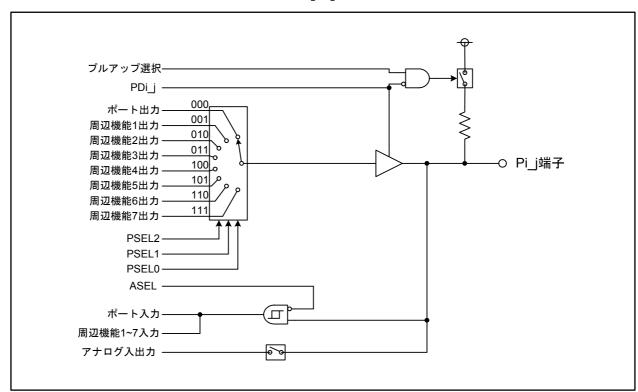

26 本文の2段落目を以下のとおり訂正いたします(TN-16C-A198A/J参照)。

#### 【誤】

また、端子4本ごとにプルアップ抵抗の有無を選択できます。プルアップ抵抗は端子が出力になっている 場合と、アナログ入出力になっている場合には、レジスタの設定内容にかかわらず切り離されます。

#### 【正】

また、端子4本ごとにプルアップ抵抗の有無を選択できます。プルアップ抵抗は端子が出力になっている 場合、レジスタの設定内容にかかわらず切り離されます。

# •Page 461 of 582

図26.1を以下のとおり訂正いたします(TN-16C-A198A/J参照)。

# 【誤】

図26.1 入出力端子ブロック図(代表例)(i=0~10、j=0~7)

### 【正】

図26.1 入出力端子ブロック図(代表例)(i=0~10、j=0~7)

# •Page 486 of 582

表27.3の保護対象を以下のとおり訂正いたします。

### 【誤】

### 表27.3 プロテクトの種類と特徴

| プロテクト | ロックビットプロテクト     | ROMコードプロテクト  | IDコードプロテクト   |

|-------|-----------------|--------------|--------------|

| 保護対象  | 消去、書き込み         | 読み出し、消去、書き込み | 読み出し、書き込み    |

| :     | :               | :            | :            |

| 解除方法  | FMR レジスタのLBDビッ  | シリアルライタでプロテク | シリアルライタから正しい |

|       | トを"1"(ロックビット無効) | トビットがセットされたブ | IDコードを入力する   |

|       | にする             | ロックすべてを消去する  |              |

|       | 恒久的には上記操作の後、    |              |              |

|       | 該当ブロックを消去する     |              |              |

# 【正】

#### 表27.3 プロテクトの種類と特徴

| プロテクト | ロックビットプロテクト     | ROMコードプロテクト  | IDコードプロテクト   |

|-------|-----------------|--------------|--------------|

| 保護対象  | 消去、書き込み         | 読み出し、書き込み    | 読み出し、消去、書き込み |

| :     | :               | :            | :            |

| 解除方法  | FMR レジスタのLBD ビッ | プロテクトビットがセット |              |

|       | トを"1"(ロックビット無効) | されたブロックすべてを消 | IDコードを入力する   |

|       | にする             | 去する          |              |

|       | 恒久的には上記操作の後、    |              |              |

|       | 該当ブロックを消去する     |              |              |

### •Page 486 of 582

27.2.2 本文の1段落目の一部を以下のとおり削除いたします。

# 【誤】

パラレル入出力モードに対して有効なプロテクトです。ROM コードプロテクトが有効な場合、パラレル ライタでは、いずれの領域の内容も読み書きできません。ROM コードプロテクトを解除するには、シリア ルライタを使ってプロテクトビットを"0"(プロテクト)にしたすべてのブロックを消去してください。

# 【正】

パラレル入出力モードに対して有効なプロテクトです。ROM コードプロテクトが有効な場合、パラレル ライタでは、いずれの領域の内容も読み書きできません。ROM コードプロテクトを解除するには、プロテ クトビットを"0"(プロテクト)にしたすべてのブロックを消去してください。

# •Page 487 of 582

図27.2を以下のとおり訂正いたします。

# 【誤】

### 図27.2 IDコード格納番地

### 【正】

図27.2 IDコード格納番地

#### •Page 489 of 582

表27.5のEW0モード、EW1モード欄に記載しているコマンド名を以下のとおり訂正いたします。

【誤】

- •イレーズコマンド

- リードステータスレジスタコマンド

【正】

- ブロックイレーズコマンド

- リードステータスレジスタモード移行コマンド

### •Page 495, 497 of 582

図27.12、図27.13の信号名をそれぞれ以下のとおり訂正いたします。

【誤】

図 27.12: <u>CS0</u>

A23~A0,  $\overline{BC0}$ ~ $\overline{BC3}$

図 27.13: <del>CS0~CS3</del>

A23~A0,  $\overline{BC0}$ ~ $\overline{BC3}$

【正】

図27.12: チップセレクト

アドレス

図27.13: チップセレクト

アドレス

# •Page 515 of 582

図28.2の注3、注5の文章をそれぞれ以下のとおり訂正いたします。

注3. このビットを"1"にすると、実行中の処理を中断して初期状態に戻ります。

注5. E2FI レジスタにどのような値を書いても00F3h(リードコマンド)が設定されます。このモードに設定 しておくことにより、プログラム暴走時にデータが上書きされるのを予防できます。

注3. このビットを"1"にすると、実行中の処理を中断して初期状態に戻ります。なお、レジスタは初期化 されません。

注5. E2FIレジスタにどのような値を書いても00F3h(リードコマンド)が設定されます。

#### •Page 533 of 582

図29.5の信号名を以下のとおり訂正いたします。

【誤】

$\frac{y-\dot{y}+7\rho\nu}{CS0}$

A23~A0,  $\overline{BC0}$ ~ $\overline{BC3}$

$\frac{7}{\text{CS0}}$

A23~A0,  $\overline{BC0}$ ~ $\overline{BC3}$

【正】

リードサイクル チップセレクト アドレス

ライトサイクル チップセレクト アドレス

# •Page 568 of 582

30.7.1項本文を以下のとおり訂正いたします。

#### 【誤】

• PM2 レジスタの PM24 ビットが"1"(NMI有効)で、INVC0 レジスタの INV03 ビットが"1"(三相 モータ制御用タイマ出力許可)かつ、INV02 ビットが"1"(三相モータ制御用タイマ機能を使用する)のとき、 $\overline{\text{NMI}}$ 端子に"L"を入力すると TA1OUT、TA2OUT、TA4OUT端子はハイインピーダンスになります。

### 【正】

• PM2 レジスタの PM24 ビットが"1" (NMI 有効)、かつ IOBC レジスタの SDE ビットが"1" (シャット <mark>ダウン機能有効</mark>)で、INVC0 レジスタの INV02 ビットが"1" (三相モータ制御用タイマ機能を使用 する)、かつ INV03 ビットが"1" (三相モータ制御用タイマ出力許可)のとき、 NMI 端子に"L"を入力すると TA1OUT、TA2OUT、TA4OUT 端子はハイインピーダンスになります。

#### •Page 568 of 582

30.7.2項本文を以下のとおり訂正いたします。

#### 【誤】

• タイマB2 がオーバフローする前後で、TAi1 レジスタ(i=1, 2, 4)に値を設定しないでください。 TAil レジスタに値を設定する場合は、TB2 レジスタの値を読んで、オーバフローまでに十分な時 間があることを確認してから設定してください。TB2レジスタの読み出しと、TAilレジスタへの 書き込みの間隔が開かないよう、この間に割り込み処理などが実行されないようにしてくださ い。また、TB2レジスタを読み出した結果、オーバフローまでに十分な時間がない場合は、オー バフローするまで待った後TAil レジスタを設定してください。

#### 【正】

• タイマB2がアンダフローする前後で、TAi1レジスタ(i=1, 2, 4)に値を設定しないでください。 TAil レジスタに値を設定する場合は、TB2 レジスタの値を読んで、アンダフローまでに十分な時 間があることを確認してから設定してください。TB2レジスタの読み出しと、TAilレジスタへの 書き込みの間隔があかないよう、この間に割り込み処理などが実行されないようにしてくださ い。また、TB2レジスタを読み出した結果、アンダフローまでに十分な時間がない場合は、アン ダフローするまで待った後TAil レジスタを設定してください。

以上