## **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | IMPU/MCU                                                                                                                               |                         |                        | TN-SH7-A869A/E                                                           | Rev. | 1.00   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------------------------|------|--------|

| Title                 | Description Omitted from the Hardware Manu<br>Regarding the Condition for Clearing the TEN<br>TDRE Bit, and RDRF Bit in the SSU Module | Information<br>Category | Technical Notification |                                                                          |      |        |

|                       |                                                                                                                                        | Lot No.                 |                        | SH7280 Group, SH7243 Group User<br>Manual: Hardware<br>(R01UH0229EJ0300) |      |        |

| Applicable<br>Product | SH7280 Series                                                                                                                          | All lots                | Reference<br>Document  |                                                                          |      | User's |

In the description of the condition for clearing the TEND bit, TDRE bit, and RDRF bit in the SSU module of the above products, a statement of the need to set the FCLRM bit was unfortunately omitted. Therefore, we will be amending the descriptions.

[Contents]

18.3.5 SS Status Register (SSSR)

Erroneous:

| Bit | Bit<br>Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TEND        | 0                | R/W | Transmit End<br>[Setting conditions]<br>• When the last bit of transmit data is transmitted while the TENDSTS bit in<br>SSCR2 is cleared to 0 and the TDRE bit is set to 1<br>• After the last bit of transmit data is transmitted while the TENDSTS bit in<br>SSCR2 is set to 1 and the TDRE bit is set to 1<br>[Clearing conditions]<br>• When writing 0 after reading TEND = 1<br>• When writing data to SSTDR                                                                                                                                                                                                                                                     |

| 2   | TDRE        | 1                | R/W | <ul> <li>Transmit Data Empty Indicates whether or not SSTDR contains transmit data. [Setting conditions] <ul> <li>When the TE bit in SSER is 0</li> </ul> </li> <li>When data is transferred from SSTDR to SSTRSR and SSTDR is ready to be written to. [Clearing conditions] <ul> <li>When writing 0 after reading TDRE = 1</li> <li>When writing data to SSTDR with TE = 1</li> <li>When transmit data is written to SSTDR while the DMAC is activated by an SSTXI.</li> </ul> </li> <li>When transmit data is written to SSTDR while the DISEL bit in MRB of the DTC is 0 if the DMAC/DTC is activated by an SSTXI interrupt and then DMAC is activated.</li> </ul> |

| 1   | RDRF        | 0                | R/W | <ul> <li>Receive Data Register Full<br/>Indicates whether or not SSRDR contains receive data.<br/>[Setting condition]</li> <li>When receive data is transferred from SSTRSR to SSRDR after successful<br/>serial data reception<br/>[Clearing conditions]</li> <li>When writing 0 after reading RDRF = 1</li> <li>When reading receive data from SSRDR</li> <li>When transmit data is read into SSRDR while the DISEL bit in MRB of the<br/>DTC is 0 if the DMAC/DTC is activated by an SSRXI interrupt and then DTC<br/>is activated</li> </ul>                                                                                                                      |

| Corrected: |  |

|------------|--|

|------------|--|

| Bit | Bit<br>Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----|-------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3   | TEND        | 0                | R/W | Transmit End<br>[Setting conditions]<br>• When the last bit of transmit data is transmitted while the TENDSTS bit in<br>SSCR2 is cleared to 0 and the TDRE bit is set to 1<br>• After the last bit of transmit data is transmitted while the TENDSTS bit in<br>SSCR2 is set to 1 and the TDRE bit is set to 1<br>[Clearing conditions]<br>• When writing 0 after reading TEND = 1<br>• When writing data to SSTDR with FCLRM =1<br>• When transmit data is written to SSTDR while the DMAC is activated by an<br>SSTXI with FCLRM =1.<br>• When the DTC is activated by an SSTXI interrupt and transmit data is written<br>to SSTDR while the DISEL bit in MRB of the DTC is 0 (except when DTC<br>transfer counter value is H'0000)* <sup>1</sup> |  |

| 2   | TDRE        | 1                | R/W | Transmit Data Empty<br>Indicates whether or not SSTDR contains transmit data.<br>[Setting conditions]<br>• When the TE bit in SSER is 0<br>• When data is transferred from SSTDR to SSTRSR and SSTDR is ready to<br>be written to.<br>[Clearing conditions]<br>• When writing 0 after reading TDRE = 1<br>• When writing data to SSTDR with TE = 1 and FCLRM = 1<br>• When transmit data is written to SSTDR while the DMAC is activated by an<br>SSTXI with FCLRM =1.<br>• When the DTC is activated by an SSTXI interrupt and transmit data is written<br>to SSTDR while the DISEL bit in MRB of the DTC is 0 (except when DTC<br>transfer counter value is H'0000)* <sup>1</sup>                                                                |  |

| 1   | RDRF        | 0                | R/W | <ul> <li>Receive Data Register Full<br/>Indicates whether or not SSRDR contains receive data.<br/>[Setting condition]</li> <li>When receive data is transferred from SSTRSR to SSRDR after successful<br/>serial data reception<br/>[Clearing conditions]</li> <li>When writing 0 after reading RDRF = 1</li> <li>When reading receive data from SSRDR with FCLRM =1</li> <li>When receive data is read from SSRDR while the DMAC is activated by an<br/>SSRXI with FCLRM =1.</li> <li>When the DTC is activated by an SSRXI interrupt and receive data is read<br/>into SSRDR while the DISEL bit in MRB of the DTC is 0 (except when DTC<br/>transfer counter value is H'0000)*<sup>1</sup></li> </ul>                                           |  |

Note: \*1 Clearing the FCLRM bit to 0 enables transfer by the DTC.

## 18.4.5 SSU Mode

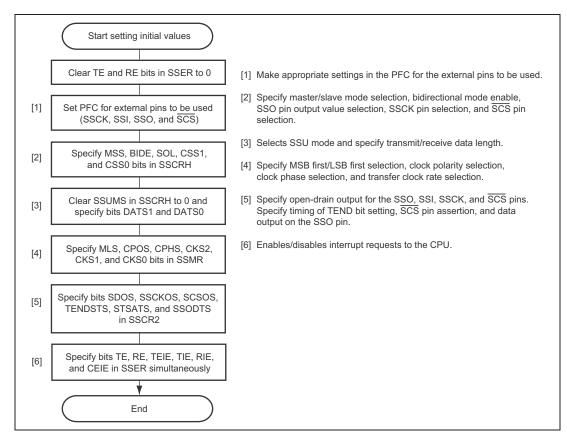

## Erroneous:

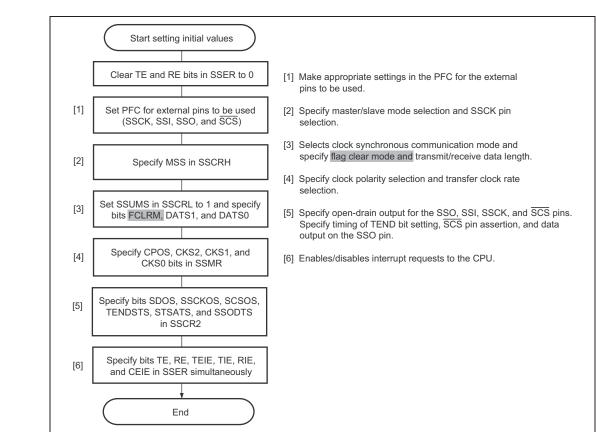

Figure 18.4 Example of Initial Settings in SSU Mode

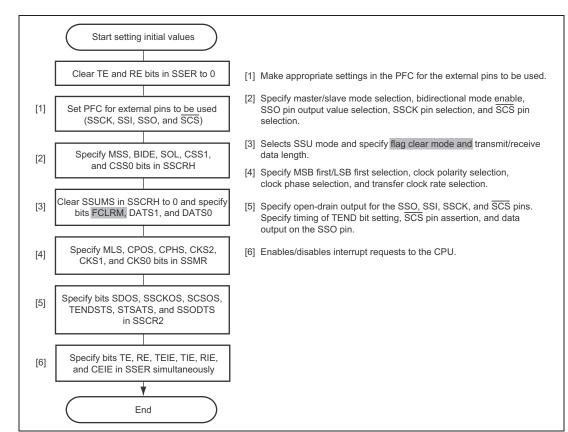

Figure 18.4 Example of Initial Settings in SSU Mode

## Erroneous:

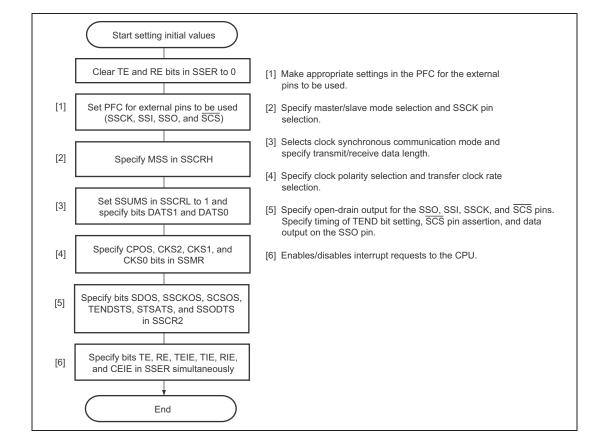

Figure 18.12 Example of Initial Settings in Clock Synchronous Communication Mode

Figure 18.12 Example of Initial Settings in Clock Synchronous Communication Mode