# RENESAS TECHNICAL UPDATE

〒211-8668 神奈川県川崎市中原区下沼部1753

ルネサス エレクトロニクス株式会社

問合せ窓口 <http://japan.renesas.com/contact/>

E-mail: csc@renesas.com

| 製品分類 | MPU & MCU                                                        | 発行番号   | TN-RX*-A102A/J | Rev.                                                                      | 第1版 |

|------|------------------------------------------------------------------|--------|----------------|---------------------------------------------------------------------------|-----|

| 題名   | RX62N グループ、RX621 グループ USB2.0 ホスト/ファンクションモジュール(USB)に関するマニュアルの誤記訂正 |        | 情報分類           | 技術情報                                                                      |     |

| 適用製品 | RX62N グループ、RX621 グループ                                            | 対象ロット等 | 関連資料           | RX62N グループ、RX621 グループ<br>ユーザーズマニュアル ハードウェア編<br>Rev.1.30 (R01UH0033JJ0130) |     |

|      |                                                                  | 全ロット   |                |                                                                           |     |

RX62N グループ、RX621 グループ ユーザーズマニュアル ハードウェア編のUSB2.0 ホスト/ファンクションモジュール(USB)章において誤記がありましたので、以下のとおり訂正いたします。

## 〈訂正内容〉

### ・用語変更

以下の用語を変更いたします。

#### 【誤】

SOF補間機能

#### 【正】

SOF補完機能

### ・Page 1251 of 1974

表28.1 に以下のとおり注記を追加いたします。

#### 【正】

表28.1 USBの仕様

| 項目 | 内容                                                                                                                                                                                                                                                                                                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 特長 | <ul style="list-style-type: none"> <li>•</li> <li>•</li> <li>(1) ホストコントローラ機能選択時           <ul style="list-style-type: none"> <li>• フルスピード転送 (12Mbps) に対応 (注1)</li> </ul> </li> <li>•</li> <li>(2) ファンクションコントローラ機能選択時           <ul style="list-style-type: none"> <li>• フルスピード転送 (12Mbps) に対応 (注1)</li> </ul> </li> <li>•</li> <li>•</li> </ul> |

以下省略

注1. ロースピード転送 (1.5Mbps) には対応していません。

## •Page 1261 of 1974

28.2.3 DVSTCTR0 レジスタの RHST[2:0] ビットの機能欄を以下のとおり訂正いたします。

## 【誤】

| ビット   | シンボル      | ビット名              | 機能                                                                                                                                                                                                                                                                                                                                   | R/W |

|-------|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b2-b0 | RHST[2:0] | USBバスリセットステータスビット | <ul style="list-style-type: none"> <li>• ホストコントローラ機能選択時<br/>b2 b0<br/>0 0 0 : 通信速度不定 (パワード時あるいは非接続時)<br/>1 x x : USBバスリセット処理中<br/>0 0 1 : ロースピード接続時 (注1)<br/>0 1 0 : フルスピード接続時<br/>【記号説明】 X : Don't care</li> <li>• ファンクションコントローラ機能選択時<br/>b2 b0<br/>0 0 0 : 通信速度不定<br/><b>1 0 0 : USBバスリセット処理中</b><br/>0 1 0 : フルスピード接続時</li> </ul> | R   |

## 【正】

| ビット   | シンボル      | ビット名              | 機能                                                                                                                                                                                                                                                                                                                    | R/W |

|-------|-----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b2-b0 | RHST[2:0] | USBバスリセットステータスビット | <ul style="list-style-type: none"> <li>• ホストコントローラ機能選択時<br/>b2 b0<br/>0 0 0 : 通信速度不定 (パワード時あるいは非接続時)<br/>1 x x : USBバスリセット処理中<br/>0 0 1 : ロースピード接続時 (注1)<br/>0 1 0 : フルスピード接続時<br/>x : Don't care</li> <li>• ファンクションコントローラ機能選択時<br/>b2 b0<br/>0 0 0 : 通信速度不定<br/><b>0 1 0 : USBバスリセット処理中 または フルスピード接続時</b></li> </ul> | R   |

## •Page 1261 of 1974

28.2.3 DVSTCTR0 レジスタの WKUP ビットに関する注意事項を削除いたします。

## 【誤】

注2. “1”のみ書けます。

•Page 1262 of 1974

28.2.3 DVSTCTR0 レジスタのRESUME ビットの説明文を以下のとおり変更いたします。

【誤】

ホストコントローラ機能選択時に、レジューム信号の出力制御を行います。

RESUME ビットを“1”にすると、USB モジュールはポートを K-State ドライブし、レジューム出力を行います。

—(省略)—

【正】

ホストコントローラ機能選択時に、レジューム信号の出力制御を行います。

RESUME ビットを“1”にすると、USB モジュールはポートを K-State ドライブし、レジューム出力を行います。また、RWUPE ビットが“1”かつサスペンド中にリモートウェイクアップ信号を検出すると、USB モジュールはRESUME ビットを”1”にし、同様の動作を行います。

—(省略)—

## •Page 1264 of 1974

28.2.4 CFIFO、D0FIFO、D1FIFO レジスタに関する説明を以下のとおり変更いたします。

## 【誤】

| ビット    | シンボル   | ビット名       | 機能                                                                                | R/W |

|--------|--------|------------|-----------------------------------------------------------------------------------|-----|

| b15-b8 | L[7:0] | FIFOポートビット | FIFOポートレジスタの有効ビットは、MBWビットの設定値およびBIGENDビットの設定値により異なります。<br>有効ビットを、表28.7、表28.8に示します | R/W |

| b7-b0  | H[7:0] |            |                                                                                   |     |

## L[7:0] / H[7:0] (FIFOポートビット)

FIFOPORTビットにアクセスすることにより、FIFOバッファからの受信データを読み出し、もしくはFIFOバッファへの送信データの書き込みを行います。

FIFOポートレジスタへのアクセスは、各FIFOポートコントロールレジスタ (CFIFOCTR、D0FIFOCTRまたはD1FIFOCTR) のFRDYビットが“1”を示しているときのみ可能です。

FIFOポートレジスタの有効ビットは、ポート選択レジスタのMBWビットの設定値およびBIGENDビットの設定値により異なります。有効ビットを表28.7、表28.8に示します。

8ビットアクセス時は、バイトアクセスしてください。また、BIGENDビットの設定は無効です。

16ビットアクセス時は、ワードアクセスしてください。ただし、データ総数が奇数の場合については、最後のデータはバイトアクセスしてください。

アクセスするときのアドレスは、8ビットアクセス時および16ビットアクセス時ともに、設定によらず常にFIFOレジスタの先頭アドレスへアクセスしてください。

表28.7 16ビットアクセス時のエンディアン動作表

| CFIFOSEL.BIGENDビット<br>D0FIFOSEL.BIGENDビット<br>D1FIFOSEL.BIGENDビット | ビット15~8 | ビット7~0 |

|------------------------------------------------------------------|---------|--------|

| 0                                                                | N+1データ  | N+0データ |

| 1                                                                | N+0データ  | N+1データ |

表28.8 8ビットアクセス時のエンディアン動作表

| CFIFOSEL.BIGENDビット<br>D0FIFOSEL.BIGENDビット<br>D1FIFOSEL.BIGENDビット | ビット15~8                | ビット7~0 |

|------------------------------------------------------------------|------------------------|--------|

| 0                                                                | アクセス禁止 <sup>(注1)</sup> | N+0データ |

| 1                                                                | アクセス禁止 <sup>(注1)</sup> | N+0データ |

注1. 禁止領域へのリードアクセスは禁止です。

## 【正】

| ビット    | シンボル   | ビット名       | 機能                                                                                                                              | R/W |

|--------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| b15-b8 | L[7:0] | FIFOポートビット | FIFOポートレジスタの有効ビットは、MBWビットの設定値により異なります。<br>MBWビットが“1”(16ビット幅)の場合は、MDE端子の状態と、BIGENDビットの設定値との関係により、データ配置が変わります。詳細は、表28.7を参照してください。 | R/W |

| b7-b0  | H[7:0] |            | MBWビットが“0”(8ビット幅)の場合は、先頭アドレスにバイトアクセスしてください。                                                                                     |     |

## L(7:0) / H(7:0) (FIFOポートビット)

FIFOポートビットにアクセスすることにより、FIFOバッファからの受信データの読み出し、もしくはFIFOバッファへの送信データの書き込みを行います。

FIFOポートレジスタへのアクセスは、各FIFOポートコントロールレジスタ(CFIFOCTR、D0FIFOCTRまたはD1FIFOCTR)のFRDYビットが“1”を示しているときのみ可能です。

FIFOポートレジスタの有効ビットは、ポート選択レジスタのMBWビット(CFIFOSEL.MBW、D0FIFOSEL.MBW、D1FIFOSEL.MBW)の設定値により異なります。また、MBWビットが“1”(16ビット幅)の場合は、MDE端子の状態と、BIGENDビット(CFIFOSEL.BIGEND、D0FIFOSEL.BIGEND、D1FIFOSEL.BIGEND)の設定値との関係により、RAM上とデータ配置が変わる場合があります。16ビットアクセス時のエンディアン動作を表28.7に示します。

8ビットアクセス時は、バイトアクセスしてください。また、BIGENDビットの設定は無効です。

16ビットアクセス時は、ワードアクセスしてください。ただし、送信データ総数が奇数バイトの場合、最後のデータを書くときはバイトアクセスしてください。

アクセスするときのアドレスは、8ビットアクセス時および16ビットアクセス時ともに、設定によらず常にFIFOレジスタの先頭アドレスへアクセスしてください。

表28.7 16ビットアクセス時のエンディアン動作

| MDMONR.MDE フラグ | CFIFOSEL.BIGENDビット<br>D0FIFOSEL.BIGENDビット<br>D1FIFOSEL.BIGENDビット | ビット15~8   | ビット7~0    | 備考      |

|----------------|------------------------------------------------------------------|-----------|-----------|---------|

| 0(リトルエンディアン)   | 0(リトルエンディアン)                                                     | N+1番地のデータ | N番地のデータ   |         |

|                | 1(ビッグエンディアン)                                                     | N番地のデータ   | N+1番地のデータ | バイト逆転あり |

| 1(ビッグエンディアン)   | 0(リトルエンディアン)                                                     | N+1番地のデータ | N番地のデータ   | バイト逆転あり |

|                | 1(ビッグエンディアン)                                                     | N番地のデータ   | N+1番地のデータ |         |

## •Page 1266, 1268 of 1974

28.2.5 CFIFOSEL、D0FIFOSEL、D1FIFOSELレジスタのREWビットに関する注意事項を以下のとおり訂正いたします。

## 【誤】

注. “0”を読み出すことのみ可能です。

## 【正】

注. 読むと“0”が読めます。

## •Page 1271 of 1974

28.2.6 CFIFOCTR、D0FIFOCTR、D1FIFOCTR レジスタのBCLR ビットに関する注意事項を以下のとおり訂正いたします。

## 【誤】

注1. “0”を読んだ後、“1”を書くことのみ可能です。

## 【正】

注1. 読むと“0”が読みます。

## •Page 1271 of 1974

28.2.6 CFIFOCTR、D0FIFOCTR、D1FIFOCTR レジスタのBVAL ビットに関する注意事項を削除いたします。

## 【誤】

注2. “1”を書くことのみ可能です。

## •Page 1280 of 1974

28.2.12 SOFCFG レジスタのTRNENSEL ビットを以下のとおり予約ビットに訂正いたします。

## 【誤】

| ビット | シンボル     | ビット名                | 機能                            | R/W |

|-----|----------|---------------------|-------------------------------|-----|

| b8  | TRNENSEL | トランザクション有効期間切り替えビット | 0: ロースピード未対応<br>1: 設定しないでください | R/W |

## 【正】

| ビット | シンボル | ビット名  | 機能                          | R/W |

|-----|------|-------|-----------------------------|-----|

| b8  | —    | 予約ビット | 読むと“0”が読みます。書く場合、“0”としてください | R/W |

## •Page 1280 of 1974

28.2.12 SOFCFG レジスタのTRNENSEL ビットの説明文を削除いたします。

## 【誤】

## TRNENSEL ビット (トランザクション有効期間切り替えビット)

フルスピード通信中のポートにおいて、1フレーム中にUSBモジュールがトークン発行を行う期間(トランザクション有効期間)を指定します。

TRNENSEL ビットは、ホストコントローラ機能選択時のみ有効です。

ファンクションコントローラ機能選択時は、“0”にしてください。

## •Page 1281 of 1974

28.2.13 INTSTS0 レジスタのリセット後の値に関する注意事項を以下のとおり訂正いたします。

## 【誤】

|         | b15   | b14  | b13  | b12                 | b11  | b10  | b9   | b8   | b7                | b6        | b5    | b4                  | b3 | b2 | b1        | b0 |

|---------|-------|------|------|---------------------|------|------|------|------|-------------------|-----------|-------|---------------------|----|----|-----------|----|

| リセット後の値 | VBINT | RESM | SOFR | DVST                | CTRT | BEMP | NRDY | BRDY | VBSTS             | DVSQ[2:0] | VALID |                     |    |    | CTSQ[2:0] |    |

|         | 0     | 0    | 0    | 0/1 <sup>(注1)</sup> | 0    | 0    | 0    | 0    | 0 <sup>(注3)</sup> | 0         | 0     | 0/1 <sup>(注2)</sup> | 0  | 0  | 0         | 0  |

注1. パワーオンリセットのとき 0b、USBバスリセットのとき“1b”になります。

注2. パワーオンリセットのとき 000b、USBバスリセットのとき“001b”になります。

注3. USBm\_VBUS 端子が High のとき“1”、Low のとき“0”です。

## 【正】

|         | b15   | b14  | b13  | b12         | b11  | b10  | b9   | b8   | b7        | b6        | b5        | b4          | b3 | b2 | b1        | b0 |

|---------|-------|------|------|-------------|------|------|------|------|-----------|-----------|-----------|-------------|----|----|-----------|----|

| リセット後の値 | VBINT | RESM | SOFR | DVST        | CTRT | BEMP | NRDY | BRDY | VBSTS     | DVSQ[2:0] | VALID     |             |    |    | CTSQ[2:0] |    |

|         | 0     | 0    | 0    | 0/1<br>(注1) | 0    | 0    | 0    | 0    | 0<br>(注2) | 0<br>(注3) | 0<br>(注3) | 0/1<br>(注3) | 0  | 0  | 0         | 0  |

注1. MCUがリセットされると“0”、USBバスリセットが起こると“1”になります。

注2. USBm\_VBUS 端子が High のとき“1”、Low のとき“0”になります。

注3. MCUがリセットされると“000b”、USBバスリセットが起こると“001b”になります。

## •Page 1281 of 1974

28.2.13 INTSTS0 レジスタのDVSQ[2:0]ビットの機能欄を以下のとおり訂正いたします。

## 【誤】

| ビット   | シンボル      | ビット名        | 機能                                                                                                                                         | R/W |

|-------|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b6-b4 | DVSQ[2:0] | デバイスステートビット | b6 b4<br>0 0 0 : パワードステート<br>0 0 1 : デフォルトステート<br>0 1 0 : アドレスステート<br>0 1 1 : コンフィギュレーションステート<br>1 x x : サスペンドステート<br>【記号説明】x : Don't care | R   |

## 【正】

| ビット   | シンボル      | ビット名        | 機能                                                                                                                                                | R/W |

|-------|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b6-b4 | DVSQ[2:0] | デバイスステートビット | b6 b4<br>0 0 0 : Poweredステート<br>0 0 1 : Defaultステート<br>0 1 0 : Addressステート<br>0 1 1 : Configuredステート<br>1 x x : Suspendedステート<br>(x : Don't care) | R   |

**•Page 1290 of 1974**

28.2.18 FRMNUM レジスタのCRCE ビット、OVRN ビットに関する注意事項を以下のとおり訂正いたします。

**【誤】**

注1. “0”のみ書けます。

**【正】**

注1. 各ステータスを“0”にする場合は、クリアしたいビットに“0”を、他のビットには“1”を書いてください。

**•Page 1290 of 1974**

28.2.18 FRMNUM レジスタのCRCE ビットの説明文、5行目以降を以下のとおり訂正いたします。

**【誤】****(1) ホストコントローラ機能選択時**

CRC エラーの検出時には、USB モジュールは内部NRDY 割り込み要求を発生させます。

**(2) ファンクションコントローラ機能選択時**

CRC エラーの検出時には、USB モジュールは内部NRDY 割り込み要求を発生させません。

**【正】**

CRC エラーの検出時には、USB モジュールは内部NRDY 割り込み要求を発生させます。

**•Page 1299 of 1974**

28.2.27 DCPCTR レジスタのSQSET、SQCLR ビットに関する注意事項を以下のとおり訂正いたします。

**【誤】**

注1. 読むと“0”が読めます。“1”を書くことのみ有効です。

**【正】**

注1. 読むと“0”が読めます。

**•Page 1299 of 1974**

28.2.27 DCPCTR レジスタのSUREQCLR、SUREQ ビットに関する注意事項を削除いたします。

**【誤】**

注2. “1”を書くことのみ有効です。

**•Page 1306 of 1974**

28.2.30 PIPEMAXP レジスタの MXPS[8:0] ビットに関する説明文を以下のとおり訂正いたします。

**【誤】**

選択パイプの最大データペイロード(マックスパケットサイズ)を指定します。

MXPS ビットの設定は、転送タイプごとにUSB規格に準拠した値を設定してください。MXPS ビットが“0”的とき、FIFOバッファへの書き込み、または**PID = BUF**の設定は行わないでください。

**【正】**

選択パイプの最大データペイロード(マックスパケットサイズ)を指定します。

MXPS[8:0] ビットの設定は、転送タイプごとにUSB規格に準拠した値を設定してください。**ただし、パイプ1、2の最大値は“256”です。** MXPS[8:0] ビットが“000h”的とき、FIFOバッファにデータを書いたり、**PID[1:0]** ビットを“01b”(BUF) にしないでください。

**•Page 1308, 1313 of 1974**

28.2.32 PIPEnCTR レジスタの SQSET、SQCLR ビットに関する注意事項を以下のとおり訂正いたします。

**【誤】**

注1. “0”読み出し、“1”書き込みのみ有効です。

**【正】**

注1. 読むと“0”が読めます。

**•Page 1324 of 1974**

28.3.1.2 の本文を以下のとおり訂正いたします。

**【誤】**

USBモジュールは、ホストコントローラ機能またはファンクションコントローラ機能を選択することができます。コントローラ機能の選択は、SYSCFG.DCFM ビットで行います。ただし、DCFM ビットの設定は、**パワーオンリセット直後の初期設定またはD+のプルアップ禁止状態(DPRPU = “0”)** で D+/D- のプルダウン禁止状態(DRPD = “0”)**とき**に行ってください。

**【正】**

USBモジュールは、ホストコントローラ機能またはファンクションコントローラ機能を選択することができます。コントローラ機能の選択は、SYSCFG.DCFM ビットで行います。ただし、DCFM ビットの設定は、**リセット解除直後の初期設定時、または D+ のプルアップと D+/D- のプルダウンがともに禁止(SYSCFG.DPRPU = 0かつDRPD = 0)** のときに行ってください。

•Page 1338 of 1974

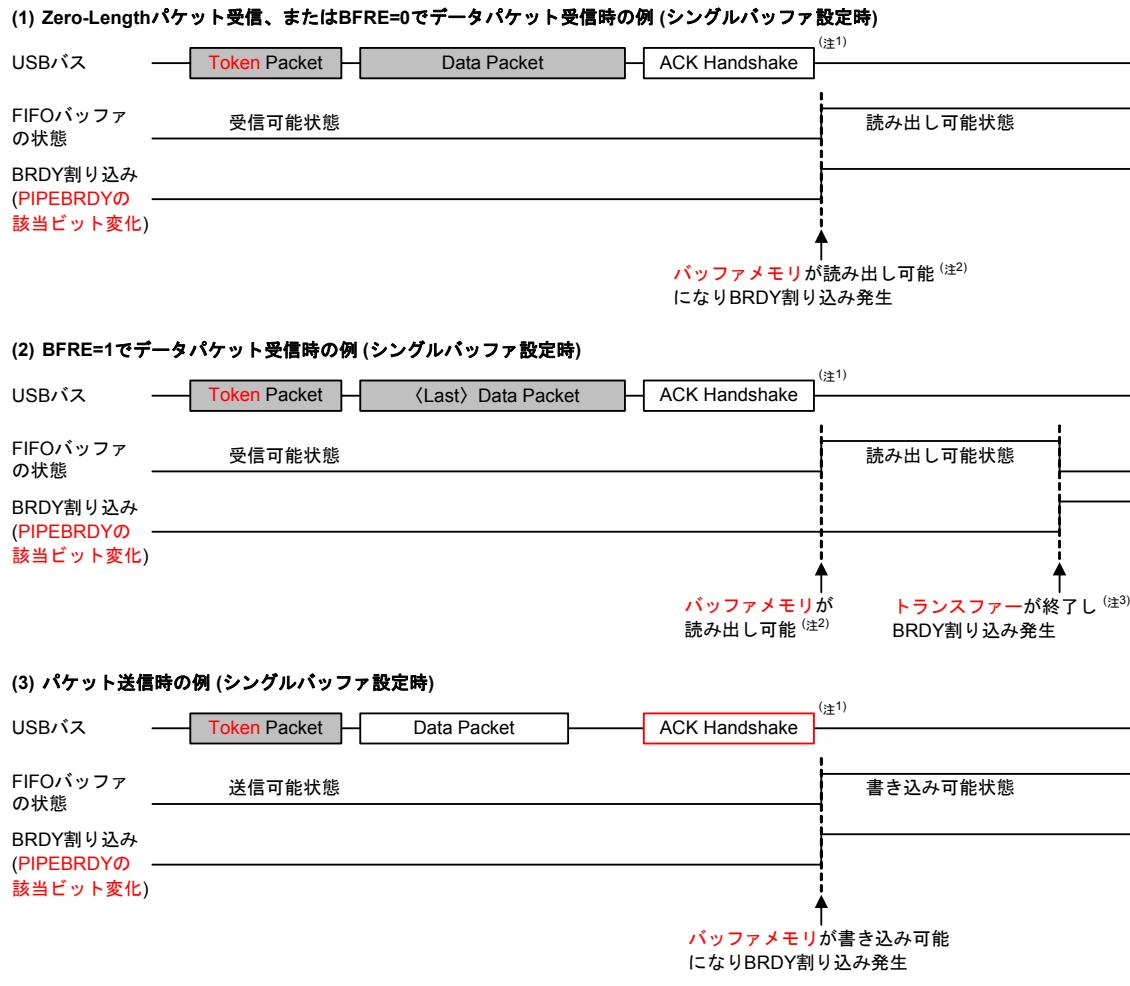

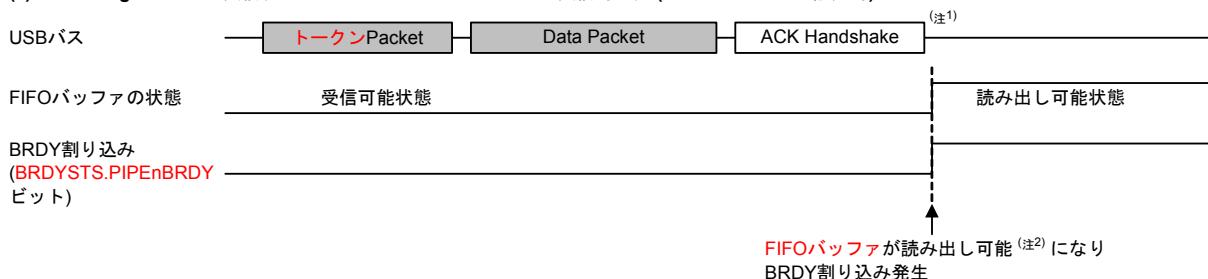

図28.11を以下のとおり訂正いたします。

### 【誤】

注1. アイソクロナス転送の場合はACK Handshakeは存在しません。

注2. FIFOバッファ読み出し可能になる条件は以下のとおりです。

未読み出しデータがCPU側バッファメモリに存在しない状態で1パケット受信が発生した。

注3. トランスマスター終了の条件は以下のとおりです。

以下(1)、(2)いずれかの受信が発生した時

(1) Zero-Lengthを含むショートパケット受信、または

(2) トランザクションカウンタ分のパケット受信

図28.11 BRDY割り込み発生タイミング図

## 【正】

## (1) Zero-Lengthパケット受信、またはBFRE=0でデータパケット受信時の例(シングルバッファ設定時)

## (2) BFRE=1でデータパケット受信時の例(シングルバッファ設定時)

## (3) パケット送信時の例(シングルバッファ設定時)

■ ホストが送信するパケット □ ファンクションが送信するパケット

- 注1. アイソクロナス転送の場合はACK Handshakeは存在しません。

- 注2. FIFOバッファが読み出し可能になる条件は以下のとおりです。

未読み出しデータがCPU側FIFOバッファに存在しない状態で1パケット受信が発生した。

- 注3. 転送終了の条件は以下のとおりです。

以下(1), (2)いずれかの受信が発生した時

(1) Zero-Lengthを含むショートパケット受信、または

(2) トランザクションカウンタ分のパケット受信

図28.11 BRDY割り込み発生タイミング図

## •Page 1342 of 1974

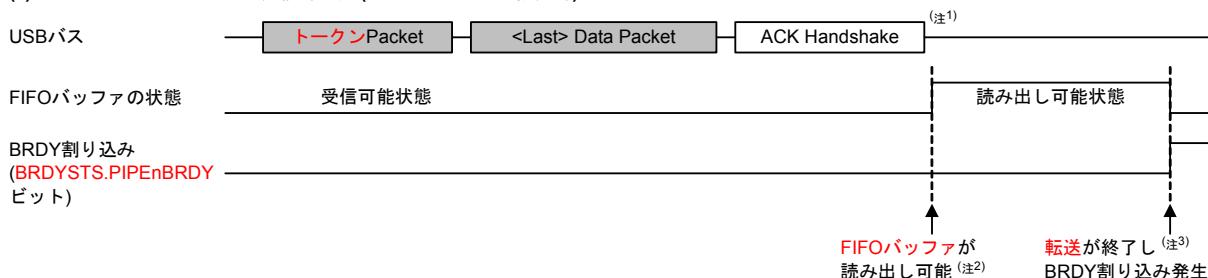

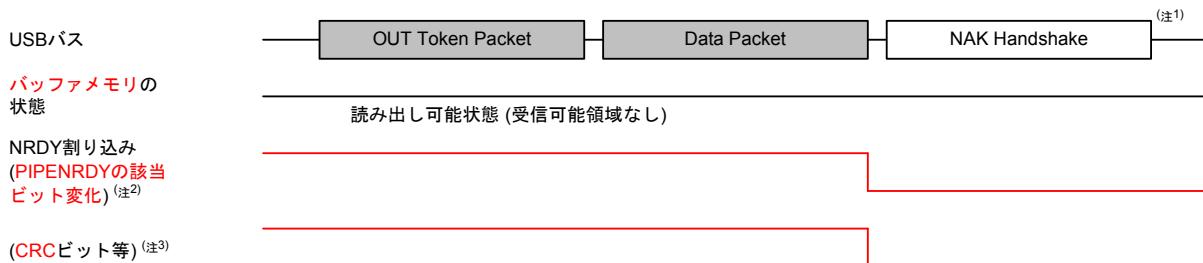

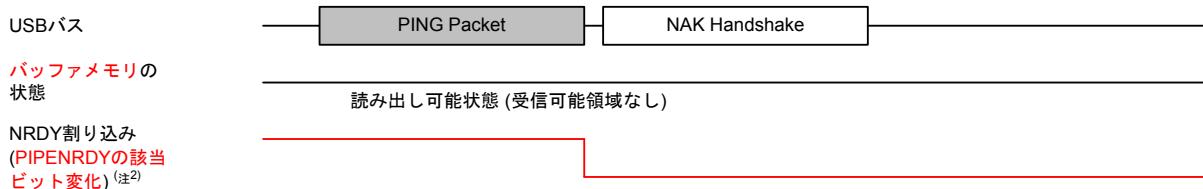

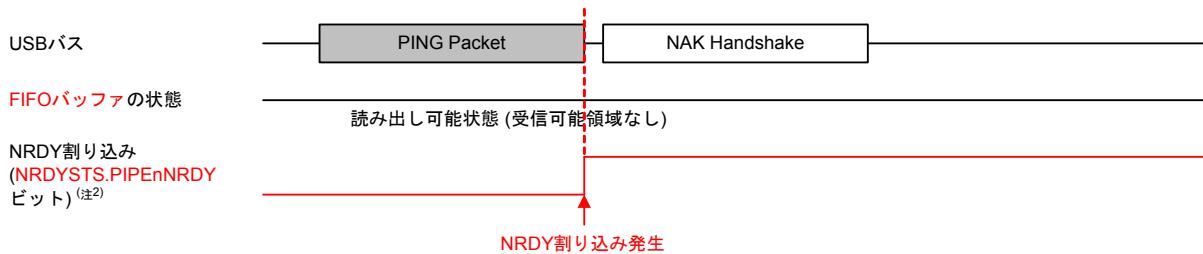

図28.12を以下のとおり訂正いたします。

## 【誤】

## (1) データ送信時の例 (シングルバッファ設定時)

## (2) データ受信; OUTトークン受信時の例 (シングルバッファ設定時)

## (3) データ受信; PINGトークン受信時の例 (シングルバッファ設定時)

Hostが送信するパケット     Peripheralが送信するパケット

注1. Isochronous転送の場合はHandshakeは存在しません。

注2. 当該PipeのPIDビットを“1”に設定している場合のみPIPENRDYビットは“1”に変化します。

注3. 当該Pipeの転送タイプがIsochronous転送の場合のときのみCRCビット、OVRNビットが変化します。

図28.12 NRDY割り込み発生タイミング図 (ファンクションコントローラ機能選択時)

## 【正】

## (1) データ送信時の例 (シングルバッファ設定時)

## (2) データ受信; OUTトークン受信時の例 (シングルバッファ設定時)

## (3) データ受信; PINGトークン受信時の例 (シングルバッファ設定時)

■ ホストが送信するパケット    □ ファンクションが送信するパケット

注1. アイソクロナス転送の場合はHandshakeは存在しません。

注2. PIPEnCTR.PID[1:0]ビットを“01b”(BUF応答)に設定している場合のみPIPEnNRDYビットは“1”に変化します。

注3. 当該Pipeの転送タイプがアイソクロナス転送の場合のみCRCEビット、OVRNビットが変化します。

図28.12 NRDY割り込み発生タイミング図 (ファンクションコントローラ機能選択時)

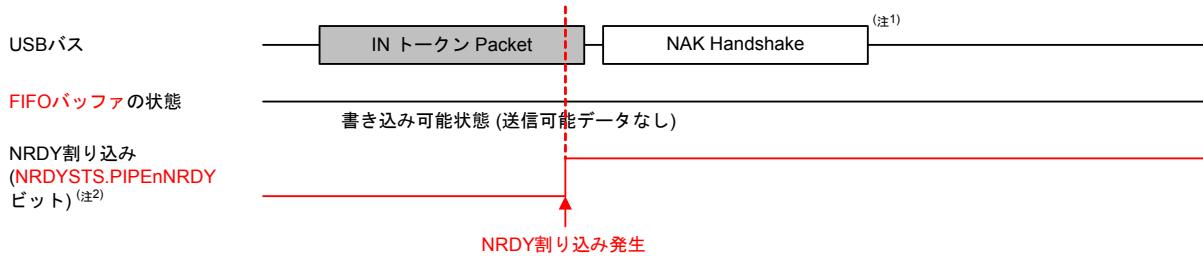

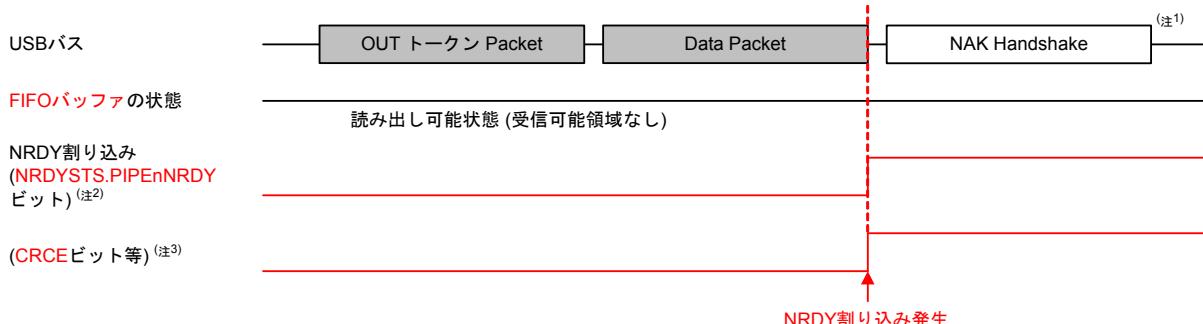

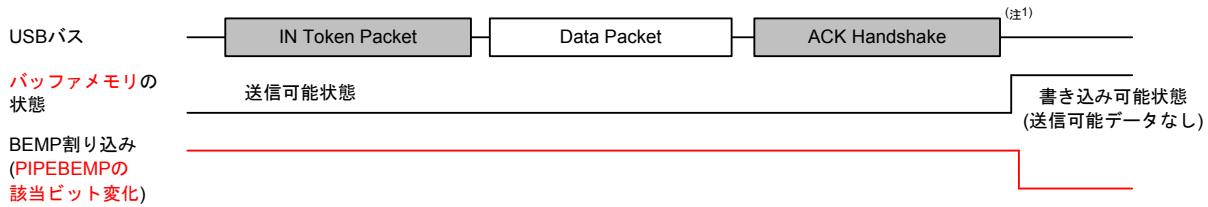

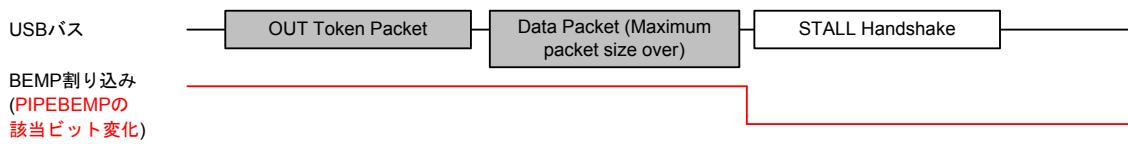

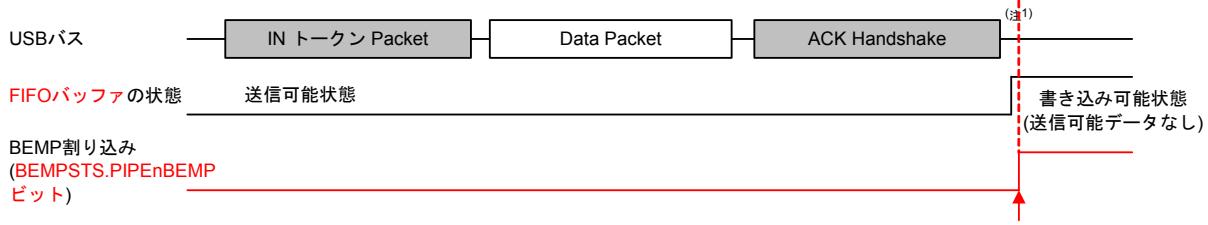

## •Page 1344 of 1974

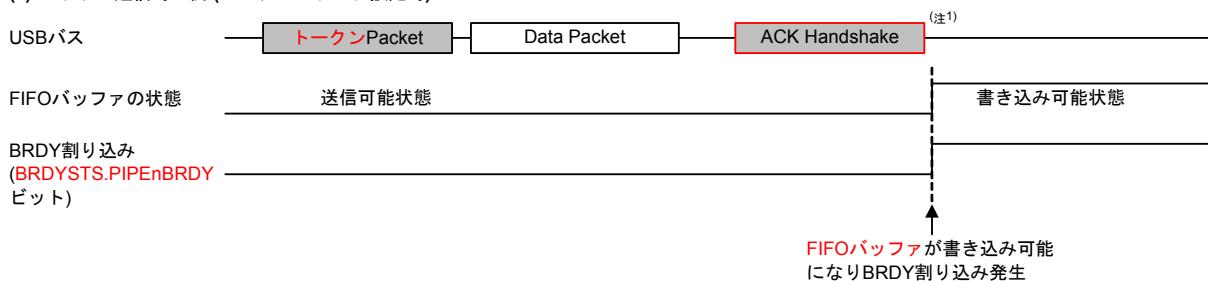

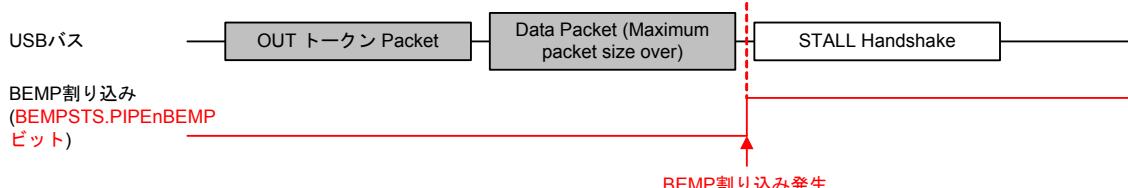

図28.13を以下のとおり訂正いたします。

## 【誤】

## (1) データ送信時の例

## (2) データ受信時の例

■ Hostが送信するパケット      □ Peripheralが送信するパケット

注1. Isochronous転送の場合はHandshakeは存在しません。

図28.13 ファンクションコントローラ機能選択時のBEMP割り込み発生タイミング図

## 【正】

## (1) データ送信時の例

## (2) データ受信時の例

■ ホストが送信するパケット      □ ファンクションが送信するパケット

注1. アイソクロナス転送の場合はHandshakeは存在しません。

図28.13 ファンクションコントローラ機能選択時のBEMP割り込み発生タイミング図

•Page 1361 of 1974

28.3.6.2 (4) 「コントロール転送自動応答機能」の説明文を以下のとおり訂正いたします。

【誤】

(4) コントロール転送自動応答機能

USB モジュールは、正常な SET\_ADDRESS リクエストに自動応答します。SET\_ADDRESS リクエストに下記のエラーがある場合はソフトウェアによる応答が必要です。

- コントロール **リード** 転送以外の場合 : bmRequestType ≠ 00h

- リクエストエラーの場合 : wIndex ≠ 00h

- ノーデータコントロール転送以外の場合 : wLength ≠ 00h

- リクエストエラーの場合 : wValue > 7Fh

- デバイスステートエラーのコントロール転送 : DVSQ[2:0] = 011b (Configured)

SET\_ADDRESS 以外のすべてのリクエストには対応するソフトウェアによる応答が必要です。

【正】

(4) コントロール転送自動応答機能

USB モジュールは、正常な SET\_ADDRESS リクエストに自動応答します。SET\_ADDRESS リクエストに下記のエラーがある場合はソフトウェアによる応答が必要です。

- bmRequestType が“00h”でない場合 : コントロール **ライト** 転送以外

- wIndex が“00h”でない場合 : リクエストエラー

- wLength が“00h”でない場合 : ノーデータコントロール転送以外

- wValue が“7Fh”より大きい場合 : リクエストエラー

- INTSTS0.DVSQ[2:0] ビットが“011b”(Configured **ステート**) の場合 : デバイスステートエラーのコントロール転送

SET\_ADDRESS 以外のすべてのリクエストには対応するソフトウェアによる応答が必要です。

**•Page 1362 of 1974**

28.3.8.1 (1) 「カウンタの初期化」の説明文を以下のとおり訂正いたします。

**【誤】****(1) カウンタの初期化**

USBコントローラがインターバルカウンタを初期化する条件は以下のとおりです。

**•パワーオンリセット:**

IITVビットが初期化されます。

**•ACLRMによるバッファメモリ初期化**

IITVビットは初期化されませんがカウントは初期化されます。**PIPEnCTR.ACRLRMビットを“0”にすることにより、IITVの設定値を最初からカウントします。**

**【正】****(1) カウンタの初期化**

インターバルカウンタは、MCUがリセットされたとき、またはPIPEnCTR.ACRLRMビットを“1”にしたときに初期化されます。なお、ACRLRMビットによる初期化時は、PIPEPERI.IITV[2:0]ビットは初期化されません。

**•Page 1365 of 1974**

28.3.9.3 (1) 「ファンクションコントローラ機能選択時でのカウンタの初期化」の説明文を以下のとおり訂正いたします。

**【誤】****(1) ファンクションコントローラ機能選択時でのカウンタの初期化**

USBモジュールは、下記の条件でインターバルカウンタを初期化します。

**•パワーオンリセット**

IITVビットが初期化されます。

**•ACLRMによるバッファメモリ初期化**

IITVビットは初期化されますがカウントは初期化されます。**ACRLRMビットを“0”にすることにより、IITVの設定値からカウントを開始します。**

**【正】****(1) ファンクションコントローラ機能選択時でのカウンタの初期化**

インターバルカウンタは、MCUがリセットされたとき、またはPIPEnCTR.ACRLRMビットを“1”にしたときに初期化されます。なお、ACRLRMビットによる初期化時は、PIPEPERI.IITV[2:0]ビットは初期化されません。

## •Page 1367 of 1974

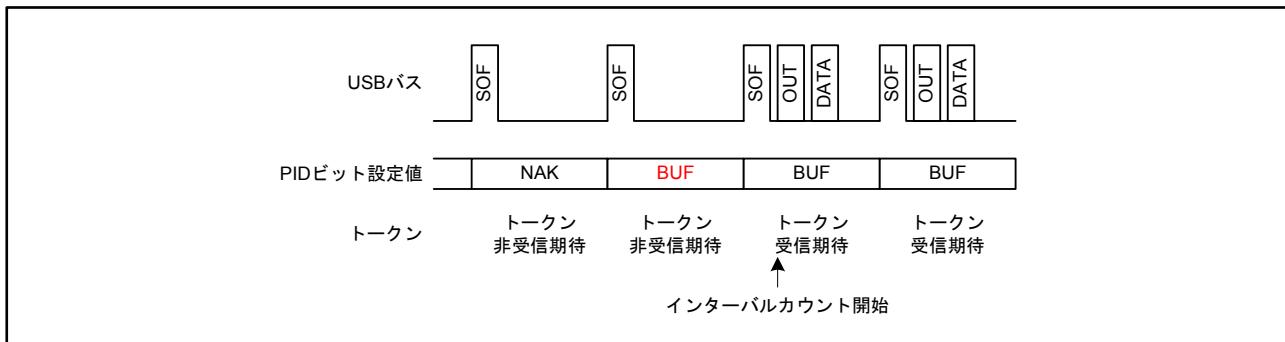

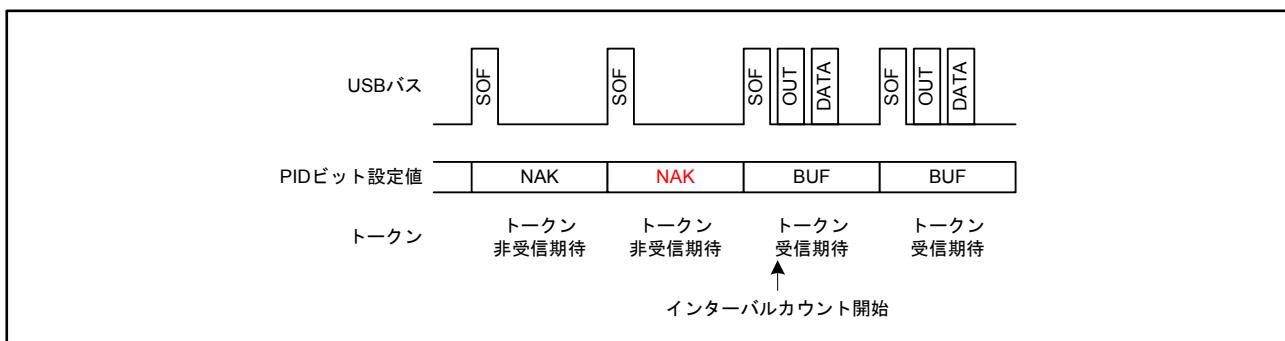

28.3.9.3 (3) の「IITV=“0”のとき」の説明文と図28.18を以下のとおり訂正いたします。

## 【誤】

- IITV=“0”的とき：選択パイプのPIDビットをBUFに変更した次のフレームからインターバルカウントを開始します。

図28.18 IITV = “0”の場合のフレームとトークン受信期待有無の関係

## 【正】

- IITV = 0 の場合

選択パイプのPID[1:0]ビットをBUFに変更した時点でインターバルのカウントを開始します。

図28.18 IITV = 0 の場合のフレームとトークン受信期待有無の関係

•Page 1372 of 1974

28.3.10 「SOF補間機能」の説明文を以下のとおり訂正いたします。

【誤】

ファンクションコントローラ機能を選択時にSOFパケットの破損または欠落のために、1ms間隔でSOFパケットを受信できなかった場合に、USB モジュールはSOF を補間します。SOF 補間動作の開始はSYSCFG.USBE = “1”、SYSCFG.SCKE = “1”かつSOFパケット受信となります。また、下記の条件で補間機能が初期化されます。

- パワーオンリセット

- USBバスリセット

- サスPEND検出

【正】

ファンクションコントローラ機能を選択時にSOFパケットの破損または欠落のために、1ms間隔でSOFパケットを受信できなかった場合に、USB モジュールはSOF を補完します。SOF 補完動作の開始はSYSCFG.USBE ビットが“1”、SYSCFG.SCKE ビットが“1”かつSOFパケット受信となります。また、下記の条件で補完機能が初期化されます。

- MCUのリセット

- USBバスリセット

- サスPEND検出

以上