# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                 | Document<br>No. | TN-RL*-A030A/E          | Rev.                                                                        | 1.00 |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-----------------------------------------------------------------------------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/G14 Descriptions in the Hardware User's Manual<br>Rev. 2.00 Changed |                 | Information<br>Category | Technical Notification                                                      |      |  |

|                       |                                                                                                                         | Lot No.         |                         |                                                                             |      |  |

| Applicable<br>Product | RL78/G14<br>R5F104xxx All lots                                                                                          |                 | Reference<br>Document   | RL78/G14 User's Manual: Hardware<br>Rev.2.00<br>R01UH0186EJ0200 (Nov. 2013) |      |  |

This document describes misstatements found in the RL78/G14 User's Manual: Hardware Rev.2.00 (R01UH0186EJ0200).

### **Corrections**

| Applicable Item                                                                                                                                | Applicable Page        | Contents                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|

| 2.4 Pin Block Diagrams (Figure2-5, Figure2-7 and addition)                                                                                     | Pages 94 and 96        | Incorrect descriptions revised |

| 17.5.7 SNOOZE mode function<br>Timing Chart of SNOOZE Mode Operation (Figure<br>17-74. and Figure 17-76.)                                      | Pages 749 and 751      | Incorrect descriptions revised |

| 17.7.3 SNOOZE mode function                                                                                                                    | Page 809               | Incorrect descriptions revised |

| 17.7.3 SNOOZE mode function<br>Timing Chart of SNOOZE Mode Operation (Figure<br>17-123., Figure 17-124. and Figure 17-126.)                    | Pages 811, 812 and 814 | Incorrect descriptions revised |

| 19.1 Alteration of Note of DTC function                                                                                                        | Page 938               | Incorrect descriptions revised |

| 34.5.1 Serial array unit (9) Communication at different<br>potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode,<br>SCKp external clock input) | Page 1191              | Incorrect descriptions revised |

| 34.7 Data Memory STOP Mode Low Supply Voltage<br>Data Retention Characteristics                                                                | Page 1209              | Content change                 |

| 35.5.1 Serial array unit (7) Communication at different<br>potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode,<br>SCKp external clock input) | Page 1252              | Incorrect descriptions revised |

| 35.7 Data Memory STOP Mode Low Supply Voltage<br>Data Retention Characteristics                                                                | Page 1267              | Content change                 |

### Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

Corrections in the User's Manual: Hardware

| No. | Corrections ar                                                                                                 | nd Applicable Iter | ns                     | Pages in this document |  |

|-----|----------------------------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|--|

|     | Document No.                                                                                                   | English            | R01UH0186EJ0200        | for corrections        |  |

| 1   | Figure 29-6 Format of Option Byt (000C2H/010C2H)                                                               | e                  | Pages 1087             | Page 3                 |  |

| 2   | 2.4 Pin Block Diagrams (Figure2-<br>and addition)                                                              | 5, Figure2-7       | Pages 94 and 96        | Pages 4 to 9           |  |

| 3   | 17.5.7 SNOOZE mode function<br>Timing Chart of SNOOZE Mode C<br>(Figure 17-74. and Figure 17-76.)              | Operation          | Pages 749 and 751      | Pages 10 and 11        |  |

| 4   | 17.7.3 SNOOZE mode function                                                                                    |                    | Page 809               | Page 12                |  |

| 5   | 17.7.3 SNOOZE mode function<br>Timing Chart of SNOOZE Mode C<br>(Figure 17-123., Figure 17-124. ar<br>17-126.) |                    | Pages 811, 812 and 814 | Pages 13 to 15         |  |

| 6   | 19.1 Alteration of Note of DTC fu                                                                              | nction             | Page 938               | Page 16                |  |

| 7   | 34.5.1 Serial array unit (9) Comm<br>different potential (1.8 V, 2.5 V, 3<br>(slave mode, SCKp external clo    | V) (CSI mode)      | Page 1191              | Page 17                |  |

| 8   | 34.7 Data Memory STOP Mode Lo<br>Voltage Data Retention Characte                                               |                    | Page 1209              | Page 18                |  |

| 9   | 35.5.1 Serial array unit (9) Comm<br>different potential (1.8 V, 2.5 V, 3<br>(slave mode, SCKp external clo    | V) (CSI mode)      | Page 1252              | Page 19                |  |

| 10  | 35.7 Data Memory STOP Mode Lo<br>Voltage Data Retention Characte                                               |                    | Page 1267              | Page 20                |  |

Incorrect: Bold with underline; Correct: Gray hatched

### **Revision History**

RL78/G14 User's Manual: Hardware Rev.2.00 Correction for Incorrect Description Notice

| Document Number | Date          | Description                                                      |

|-----------------|---------------|------------------------------------------------------------------|

| TN-RL*-A020A/E  | Dec. 19, 2013 | First edition issued<br>No.1 in a correction                     |

| TN-RL*-A030A/E  | Jul. 2, 2014  | second edition issued<br>No.2 to 10 in corrections (This notice) |

### 1. Figure 29-6 Format of Option Byte (000C2H/010C2H) (page 1087)

Incorrect:

Figure 29-6 Format of Option Byte (000C2H/010C2H)

Address: 000C2H/010C2H Note

| 7      | 6      | 5 | 4       | 3       | 2       | 1       | 0       |

|--------|--------|---|---------|---------|---------|---------|---------|

| CMODE1 | CMODE0 | 1 | FRQSEL4 | FRQSEL3 | FRQSEL2 | FRQSEL1 | FRQSEL0 |

|                  |        | Setting of flash operation mode |                 |                   |  |  |  |  |

|------------------|--------|---------------------------------|-----------------|-------------------|--|--|--|--|

| CMODE1           | CMODE0 |                                 | Operating       | Operating Voltage |  |  |  |  |

|                  |        |                                 | Frequency Range | Range             |  |  |  |  |

| 0                | 0      | LV (low voltage main) mode      | 1 to 4 MHz      | 1.6 to 5.5 V      |  |  |  |  |

| 1                | 0      | LS (low speed main) mode        | 1 to 8 MHz      | 1.8 to 5.5 V      |  |  |  |  |

| 1                | 0      | HS (high speed main) mode       | 1 to 16 MHz     | 2.4 to 5.5 V      |  |  |  |  |

| 1                |        | no (nigh speed main) mode       | 1 to 32 MHz     | 2.7 to 5.5 V      |  |  |  |  |

| Other than above |        | Setting prohibited              | ·               |                   |  |  |  |  |

Date: Jul. 2, 2014

### Correct:

### Figure 29-6 Format of Option Byte (000C2H/010C2H)

Address: 000C2H/010C2H Note

| 7      | 6      | 5 | 4       | 3       | 2       | 1       | 0       |

|--------|--------|---|---------|---------|---------|---------|---------|

| CMODE1 | CMODE0 | 1 | FRQSEL4 | FRQSEL3 | FRQSEL2 | FRQSEL1 | FRQSEL0 |

|            |          | Setting of                 | Setting of flash operation mode |                   |  |  |  |  |  |

|------------|----------|----------------------------|---------------------------------|-------------------|--|--|--|--|--|

| CMODE1     | CMODE0   |                            | Operating                       | Operating Voltage |  |  |  |  |  |

|            |          |                            | Frequency Range                 | Range             |  |  |  |  |  |

| 0          | 0        | LV (low voltage main) mode | 1 to 4 MHz                      | 1.6 to 5.5 V      |  |  |  |  |  |

| 1          | 0        | LS (low speed main) mode   | 1 to 8 MHz                      | 1.8 to 5.5 V      |  |  |  |  |  |

| 1          | 1        | HS (high speed main) mode  | 1 to 16 MHz                     | 2.4 to 5.5 V      |  |  |  |  |  |

| 1 1        |          | HS (high speed main) mode  | 1 to 32 MHz                     | 2.7 to 5.5 V      |  |  |  |  |  |

| Other that | an above | Setting prohibited         | -                               |                   |  |  |  |  |  |

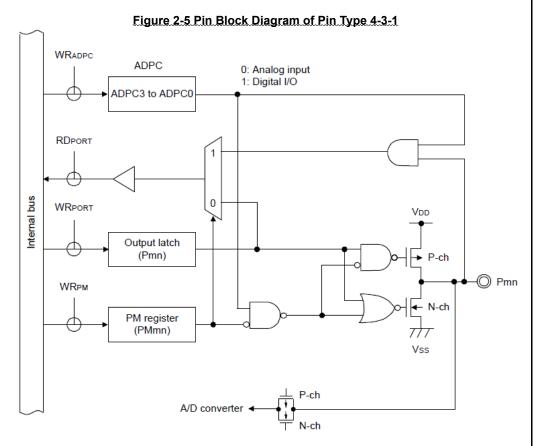

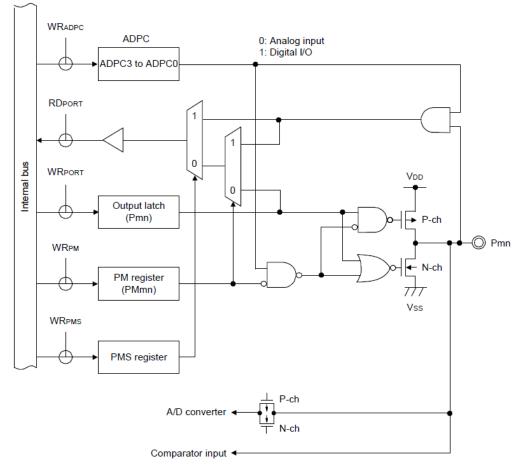

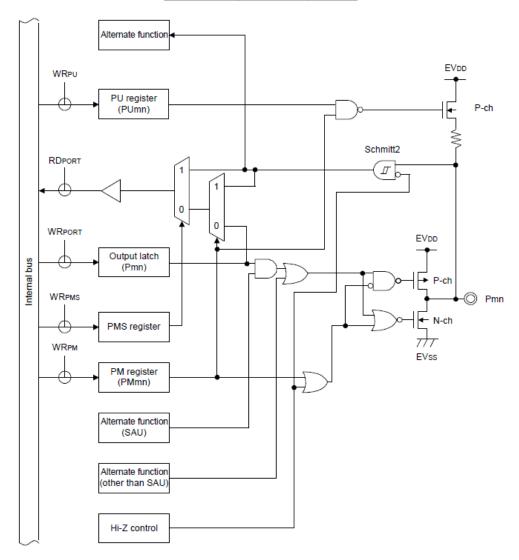

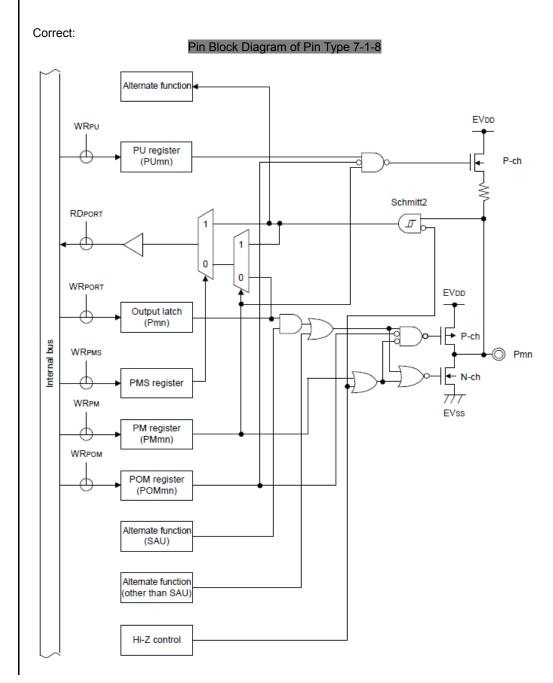

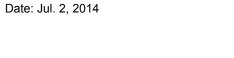

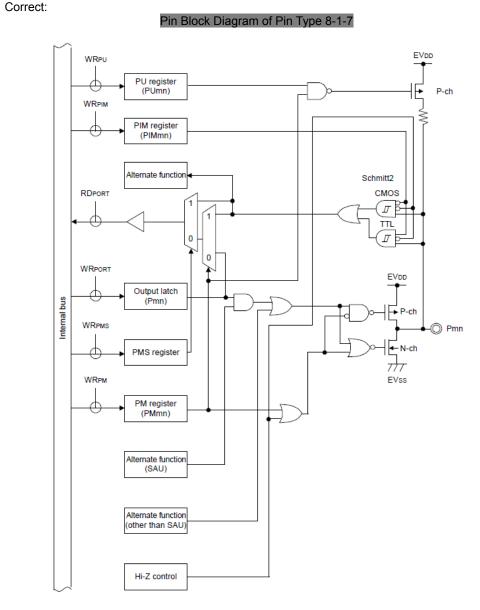

### 2. <u>2.4 Pin Block Diagrams</u>

Incorrect descriptions revised of Pin Block Diagrams (Figure2-5, Figure2-7 and addition) (Pages 94 and 96)

### Incorrect:

Correct:

### Deleted (not exist port)

Date: Jul. 2, 2014

Incorrect:

### Figure 2-7 Pin Block Diagram of Pin Type 4-6-1

Deleted (not exist port)

Incorrect:

non-existent

Date: Jul. 2, 2014

#### Correct:

Pin Block Diagram of Pin Type 7-1-7

Incorrect:

non-existent

Date: Jul. 2, 2014

Incorrect:

non-existent

Incorrect:

non-existent

### Date: Jul. 2, 2014

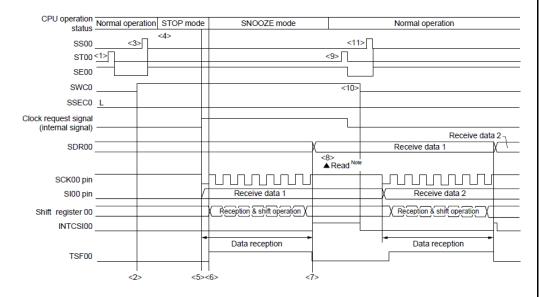

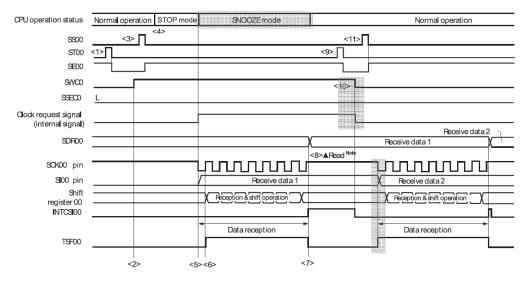

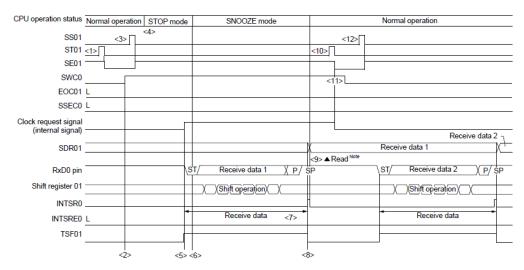

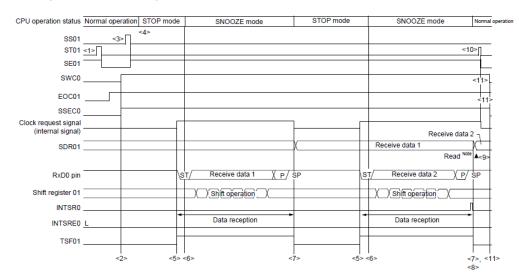

### 3. <u>17.5.7 SNOOZE mode function</u>

Timing Chart of SNOOZE Mode Operation (Figure 17-74. and Figure 17-76.) (Pages 749 and 751)

It is correction of "CPU operation status", "Clock request signal (internal signal)" and "TSF00" in this Figure.

### Incorrect:

Figure 17-74. Timing Chart of SNOOZE Mode Operation (once startup) (Type 1: DAPmn = 0, CKPmn = 0)

(omitted)

Correct: Figure 17-74. Timing Chart of SNOOZE Mode Operation (once startup) (Type 1: DAPmn = 0, CKPmn = 0)

It is correction of "CPU operation status", "Clock request signal (internal signal)" and "INTCSI00" in this Figure.

### Incorrect:

Figure 17-76. Timing Chart of SNOOZE Mode Operation (continuous startup) (Type 1: DAPmn = 0, CKPmn = 0)

(omitted)

### Correct:

Figure 17-76. Timing Chart of SNOOZE Mode Operation (continuous startup) (Type 1: DAPmn = 0, CKPmn = 0)

(omitted)

### 4. <u>17.7.3 SNOOZE mode function (Page 809)</u>

### Incorrect:

### 17.7.3 SNOOZE mode function

The SNOOZE mode makes the UART perform reception operations upon RxDq pin input detection while in the STOP mode. Normally the UART stops communication in the STOP mode. However, using the SNOOZE mode enables the UART to perform reception operations without CPU operation. Only the following UARTs can be specified when FRQSEL4 in the option byte (000C2H) = 0 in the SNOOZE mode.

### (omitted)

Cautions 1. The SNOOZE mode can only be used when the high-speed on-chip oscillator clock (fill) is selected for fcLK.

### (omitted)

Cautions 4. If a parity error, framing error, or overrun error occurs while the SSECm bit is set to 1, the PEFmn, FEFmn, or OVFmn flag is not set and an error interrupt (INTSREq) is not generated. Therefore, when the setting of SSECm = 1 is made, clear the PEFmn, FEFmn, or OVFmn flag before setting the SWC0 bit to 1 and read the value in bits 7 to 0 (RxDq register) of the SDRm1 register.

### Correct:

### 17.7.3 SNOOZE mode function

The SNOOZE mode makes the UART perform reception operations upon RxDq pin input detection while in the STOP mode. Normally the UART stops communication in the STOP mode. However, using the SNOOZE mode enables the UART to perform reception operations without CPU operation. Only the following UARTs can be specified when FRQSEL4 in the option byte (000C2H) = 0 in the SNOOZE mode.

(omitted)

Cautions 1. The SNOOZE mode can only be used when the high-speed on-chip oscillator clock (fill) is selected for fcLK.

- Cautions 4. If a parity error, framing error, or overrun error occurs while the SSECm bit is set to 1, the PEFmn, FEFmn, or OVFmn flag is not set and an error interrupt (INTSREq) is not generated. Therefore, when the setting of SSECm = 1 is made, clear the PEFmn, FEFmn, or OVFmn flag before setting the SWC0 bit to 1 and read the value in bits 7 to 0 (RxDq register) of the SDRm1 register.

- Cautions 5. The CPU shifts from the STOP mode to the SNOOZE mode on detecting the valid edge of the RxDq signal. Note, however, that transfer through the UART channel may not start and the CPU may remain in the SNOOZE mode if an input pulse on the RxDq pin is too short to be detected as a start bit. In such cases, data may not be received correctly, and this may lead to a framing error or parity error in the next UART transfer.

Correct:

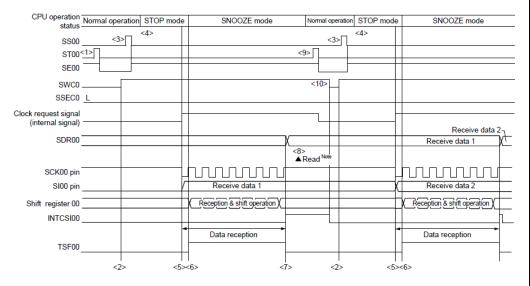

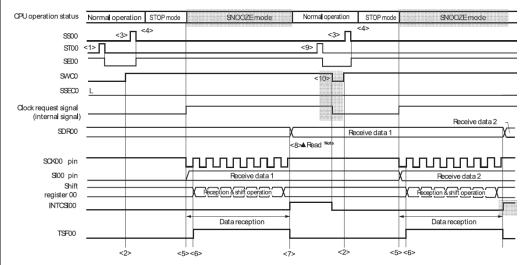

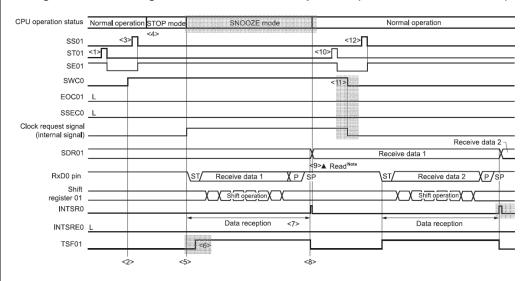

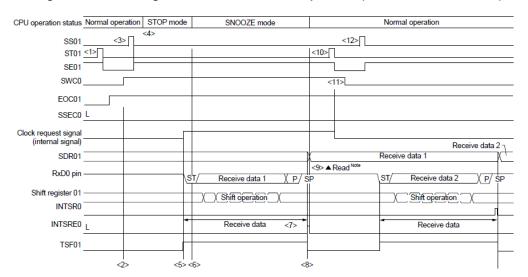

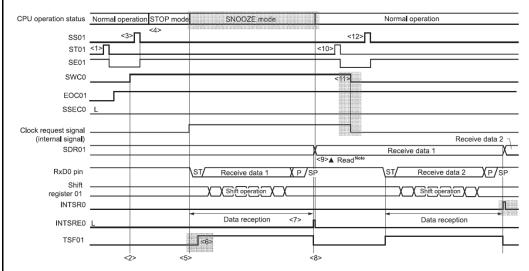

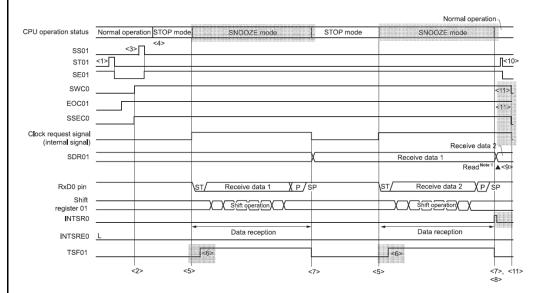

### 5. <u>17.7.3 SNOOZE mode function</u> <u>Timing Chart of SNOOZE Mode Operation (Figure 17-123., Figure 17-124. and Figure 17-126.) (Pages 811, 812 and 814)</u>

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

### Incorrect:

Figure 17-123. Timing Chart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = 0/1)

(omitted)

Figure 17-123. Timing Chart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = 0/1)

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

#### Incorrect:

Figure 17-124. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 0)

(omitted)

### Correct:

### Figure 17-124. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 0)

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

#### Incorrect:

Figure 17-126. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 1)

(omitted)

### Correct:

### Figure 17-126. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 1)

| RENESA         | S TECHNICAL UPDATE TN-RL*-A030A/E                                                                                | Date: Jul. 2, 2014                                                                                                              |      |

|----------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|

| 6. <u>19.1</u> | Alteration of Note of DTC function (Page 938)                                                                    |                                                                                                                                 |      |

| Incorrect      |                                                                                                                  | Correct:                                                                                                                        |      |

|                | Table 19-1. DTC Specifications                                                                                   | Table 19-1. DTC Specifications                                                                                                  |      |

|                | (omitted)                                                                                                        | (omitted)                                                                                                                       |      |

| Note           | In the SNOOZE mode, these areas cannot be set as the sources for DTC transfer since the flash memory is stopped. | Note In the HALT mode and SNOOZE mode, these areas cannot be se the sources for DTC transfer since the flash memory is stopped. | t as |

| Remark         | i = 0 to 4, j = 0 to 23                                                                                          | Remark i = 0 to 4, j = 0 to 23                                                                                                  |      |

|                |                                                                                                                  |                                                                                                                                 |      |

### <u>34.5.1 Serial array unit (9) Communication at different potential (1.8 V,</u> <u>2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input) (Page</u> <u>1191)</u>

Incorrect:

34.5.1 Serial array unit

(9) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

$(T_A = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{EV}_{\text{DD}0} = \text{EV}_{\text{DD}1} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{ V}_{\text{SS}} = \text{EV}_{\text{SS}0} = \text{EV}_{\text{SS}1} = 0 \text{ V})$

| Parameter  | Symbol | Conditions                                                      | HS (high-speed main) mode |      | LS (low-speed main) mode |      | LV (low-voltage main) mode |      | Unit |

|------------|--------|-----------------------------------------------------------------|---------------------------|------|--------------------------|------|----------------------------|------|------|

|            |        |                                                                 | MIN.                      | MAX. | MIN.                     | MAX. | MIN.                       | MAX. |      |

|            | -      |                                                                 | (omitte                   | d)   |                          | -    |                            |      |      |

| SIp setup  | tsik2  | $4.0~V \leq EV_{\text{DD0}} \leq 5.5~V,$                        | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

| time       |        | $2.7~V \leq V_b \leq 4.0~V$                                     | + 20                      |      | + 30                     |      | + 30                       |      |      |

| (to SCKp↑) |        | $2.7 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 4.0 \text{ V}.$ | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

| Note 3     |        | 2.3.V. <u>S.V</u> b <u>S</u> 2.7.V                              | + 20                      |      | + 30                     |      | + 30                       |      |      |

|            |        | 1.8 V ≤ EVDD0 ≤ 3.3 V.                                          | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

|            |        | 1.6.V.≤.Vb≤2.0.V.                                               | + 30                      |      | + 30                     |      | + 30                       |      |      |

|            |        | Note 2                                                          |                           |      |                          |      |                            |      |      |

|            |        |                                                                 | (omitte                   | d)   |                          |      |                            |      |      |

(omitted)

Correct:

34.5.1 Serial array unit

(9) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

$(T_{\text{A}} = -40 \text{ to } +85^{\circ}\text{C}, \text{ 1.8 V} \leq \text{EV}_{\text{DD0}} = \text{EV}_{\text{DD1}} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}, \text{ Vss} = \text{EV}_{\text{SS0}} = \text{EV}_{\text{SS1}} = 0 \text{ V})$

| Parameter  | Symbol | Conditions                                                    | HS (high-speed main) mode |      | LS (low-speed main) mode |      | LV (low-voltage main) mode |      | Unit |

|------------|--------|---------------------------------------------------------------|---------------------------|------|--------------------------|------|----------------------------|------|------|

|            |        |                                                               | MIN.                      | MAX. | MIN.                     | MAX. | MIN.                       | MAX. |      |

|            |        |                                                               | (omitte                   | ed)  |                          | -    |                            |      | -    |

| SIp setup  | tsik2  | 4.0 V $\leq$ EVDD0 $\leq$ 5.5 V,                              | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

| time       |        | $2.7~V \leq V_b \leq 4.0~V$                                   | + 20                      |      | + 30                     |      | + 30                       |      |      |

| (to SCKp↑) |        | $2.7 \text{ V} \le \text{EV}_{\text{DD0}} \le 4.0 \text{ V},$ | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

| Note 3     |        | $2.3~V \leq V_b \leq 2.7~V$                                   | + 20                      |      | + 30                     |      | + 30                       |      |      |

|            |        | $1.8 \text{ V} \le \text{EV}_{\text{DD0}} < 3.3 \text{ V},$   | 1/fмск                    |      | 1/fмск                   |      | 1/fмск                     |      | ns   |

|            |        | $1.6 \text{ V} \le \text{V}_{b} \le 2.0 \text{ V}$            | + 30                      |      | + 30                     |      | + 30                       |      |      |

|            |        | Note 2                                                        |                           |      |                          |      |                            |      |      |

(omitted)

(c) 2014. Renesas Electronics Corporation. All rights reserved.

### Date: Jul. 2, 2014

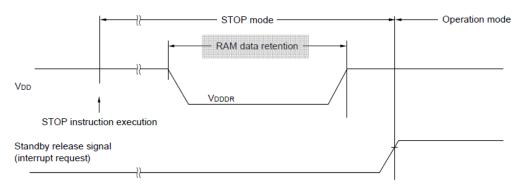

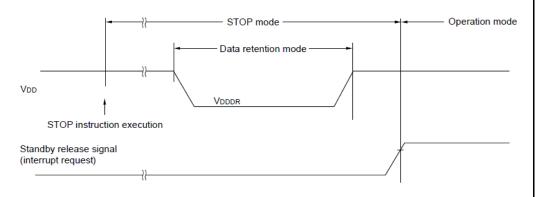

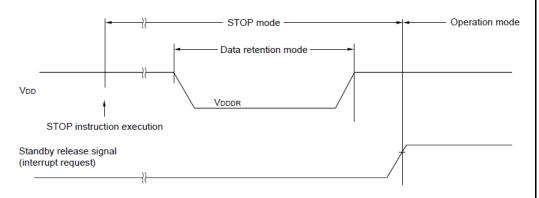

### 8. <u>34.7 Data Memory STOP Mode Low Supply Voltage Data Retention</u> <u>Characteristics (Page 1209)</u>

Old:

## 34.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{Vss} = 0 \text{ V})$

| Parameter             | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-----------------------|--------|------------|----------------------|------|------|------|

| Data retention supply | VDDDR  |            | 1.46 <sup>Note</sup> |      | 5.5  | V    |

| voltage               |        |            |                      |      |      |      |

# Note The value depends on the POR detection voltage. When the voltage drops, the data is retained before a POR reset is effected, but data is not retained when a POR reset is effected.

### New:

### 34.7 RAM Data Retention Characteristics

(T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter                     | Symbol | Conditio           | ns            | MIN.                 | TYP.     | MAX.    | Unit   |

|-------------------------------|--------|--------------------|---------------|----------------------|----------|---------|--------|

| Data retention supply voltage | Vdddr  |                    |               | 1.46 <sup>Note</sup> |          | 5.5     | V      |

| Note This depends on t        | he POR | detection voltage. | For a falling | g voltag             | ge, data | a in RA | AM are |

retained until the voltage reaches the level that triggers a POR reset but not once it

### reaches the level at which a POR reset is generated.

### 9. <u>35.5.1 Serial array unit (7) Communication at different potential (1.8 V,</u> <u>2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input) (Page</u> <u>1252)</u>

Incorrect:

35.5.1 Serial array unit

(7) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

| (omitted)                                                       | MIN.                                                                                     | MAX.                                                                                                                                                |                                                                                                      |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|                                                                 | MIN.                                                                                     | MAX.                                                                                                                                                |                                                                                                      |

|                                                                 |                                                                                          |                                                                                                                                                     |                                                                                                      |

|                                                                 |                                                                                          |                                                                                                                                                     |                                                                                                      |

| $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$   | 1/fмск + 40                                                                              |                                                                                                                                                     | ns                                                                                                   |

| $2.7~V \leq V_b \leq 4.0~V$                                     |                                                                                          |                                                                                                                                                     |                                                                                                      |

| $2.7 \text{ V} \leq \text{EV}$ DD0 $\leq 4.0 \text{ V}$ .       | 1/fмск + 40                                                                              |                                                                                                                                                     | ns                                                                                                   |

| 2.3 V ≤ Vb ≤ 2.7 V                                              |                                                                                          |                                                                                                                                                     |                                                                                                      |

| $2.4 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 3.3 \text{ V},$ | 1/fмск + 60                                                                              |                                                                                                                                                     | ns                                                                                                   |

| 1.6 V ≤ V₅ ≤ 2.0 V                                              |                                                                                          |                                                                                                                                                     |                                                                                                      |

|                                                                 | $2.7 V \le EVDD0 \le 4.0 V.$<br>$2.3 V \le Vb \le 2.7 V$<br>$2.4 V \le EVDD0 \le 3.3 V.$ | 2.7.V.≤EVDD0≤4.0.V.   1/fmck + 40     2.3.V.≤Vb≤2.7.V   2.4.V.≤EVDD0≤3.3.V.     2.4.V.≤EVDD0≤3.3.V.   1/fmck + 60     1.6.V.≤Vb≤2.0.V   1/fmck + 60 | 2.7.V ≤ EVDD0 ≤ 4.0.V. 1/fMCK + 40   2.3.V ≤ Vb ≤ 2.7.V 1/fMCK + 60   1.6.V ≤ Vb ≤ 2.0.V 1/fMCK + 60 |

(omitted)

Correct:

35.5.1 Serial array unit

(7) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{EV}_{\text{DD0}} = \text{EV}_{\text{DD1}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS0}} = \text{EV}_{\text{SS1}} = 0 \text{ V})$

| Parameter         | Symbol | Conditions                                                                                                                 |             | HS (high-speed main)<br>mode |    |  |  |  |  |

|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|----|--|--|--|--|

|                   |        |                                                                                                                            | MIN.        | MAX.                         |    |  |  |  |  |

| (omitted)         |        |                                                                                                                            |             |                              |    |  |  |  |  |

| SIp setup time    | tsıĸ2  | 4.0 V $\leq$ EVDD0 $\leq$ 5.5 V,                                                                                           | 1/fмск + 40 |                              | ns |  |  |  |  |

| (to SCKp↑) Note 2 | -      | $2.7 \text{ V} \leq V_b \leq 4.0 \text{ V}$                                                                                |             |                              |    |  |  |  |  |

|                   |        | $2.7 \text{ V} \le \text{EV}_{\text{DD0}} \le 4.0 \text{ V},$<br>$2.3 \text{ V} \le \text{V}_{\text{b}} \le 2.7 \text{ V}$ | 1/fмск + 40 |                              | ns |  |  |  |  |

|                   |        | $2.4 V \le EV_{DD0} < 3.3 V,$                                                                                              | 1/fмск + 60 |                              | ns |  |  |  |  |

|                   |        | $1.6 \text{ V} \le \text{V}_{b} \le 2.0 \text{ V}$                                                                         |             |                              |    |  |  |  |  |

### Date: Jul. 2, 2014

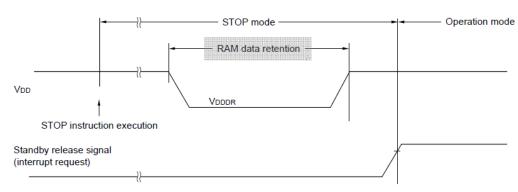

### 10. <u>35.7 Data Memory STOP Mode Low Supply Voltage Data Retention</u> <u>Characteristics (Page 1267)</u>

Old:

## 35.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics

(T<sub>A</sub> = -40 to +105°C, Vss = 0 V)

| Parameter             | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-----------------------|--------|------------|----------------------|------|------|------|

| Data retention supply | VDDDR  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

| voltage               |        |            |                      |      |      |      |

# Note The value depends on the POR detection voltage. When the voltage drops, the data is retained before a POR reset is effected, but data is not retained when a POR reset is effected.

### New:

### 35.7 RAM Data Retention Characteristics

(T<sub>A</sub> = -40 to +105°C, Vss = 0 V)

| Parameter              | Symbol | Conditions                 | MIN.                 | TYP.     | MAX.    | Unit   |

|------------------------|--------|----------------------------|----------------------|----------|---------|--------|

| Data retention supply  | VDDDR  |                            | 1.44 <sup>Note</sup> |          | 5.5     | V      |

| voltage                |        |                            |                      |          |         |        |

| Note This depends on t | he POR | detection voltage. For a f | alling voltag        | ne, data | a in RA | AM are |

retained until the voltage reaches the level that triggers a POR reset but not once it

### reaches the level at which a POR reset is generated.