# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU&MCU                                               | Document<br>No.         | TN-H8*-A405A/E                                       | Rev. | 1.00   |  |

|-----------------------|-------------------------------------------------------|-------------------------|------------------------------------------------------|------|--------|--|

| Title                 | Correction of errors in the H8SX/1653 Group<br>Manual | Information<br>Category | Technical Notification                               |      |        |  |

| Applicable<br>Product |                                                       | Lot No.                 |                                                      |      |        |  |

|                       | H8SX/1653 Group                                       | Reference<br>Document   | H8SX/1653 Group Hardware Manual<br>(REJ09B0219-0100) |      | Manual |  |

We would like to inform you of the correction of errors in the above hardware manuals. Please refer to the following for details.

<Corrections>

Section 5 Interrupt Controller

Deletion of DTCERF, DTCERG, and DTCERH (1) Page 117, 5.6.5 DTC and DMAC Activation by Interrupt

#### [Before Change]

(1) Selection of Interrupt Sources

The activation source for each DMAC channel is selected by DMRSR. The selected activation source is input to the DMAC through the select circuit. When transfer by an on-chip module interrupt is enabled (DTF1 = 1, DTF0 = 0, and DTE = 1 in DMDR) and the DTA bit in DMDR is set to 1, the interrupt source selected for the DMAC activation source is controlled by the DMAC and cannot be used as a DTC activation source or CPU interrupt source.

Interrupt sources that are not controlled by the DMAC are set for DTC activation sources or CPU interrupt sources by the DTCE bit in DTCERA to DTCERH of the DTC.

- Description omitted (no changes) -

[After Change]

(1) Selection of Interrupt Sources

The activation source for each DMAC channel is selected by DMRSR. The selected activation source is input to the DMAC through the select circuit. When transfer by an on-chip module interrupt is enabled (DTF1 = 1, DTF0 = 0, and DTE = 1 in DMDR) and the DTA bit in DMDR is set to 1, the interrupt source selected for the DMAC activation source is controlled by the DMAC and cannot be used as a DTC activation source or CPU interrupt source.

Interrupt sources that are not controlled by the DMAC are set for DTC activation sources or CPU interrupt sources by the DTCE bit in DTCERA to **DTCERE** of the DTC.

- Description omitted (no changes) -

(2) Page 118, 5.6.5 DTC and DMAC Activation by Interrupt [Before Change]

(3) Operation Order

- Description omitted (no changes) -

Table 5.6 lists the selection of interrupt sources and interrupt source clear control by setting the DTA bit in DMDR of the DMAC, the DTCE bit in DTCERA to DTCERH of the DTC, and the DISEL bit in MRB of the DTC.

[After Change]

(3) Operation Order

- Description omitted (no changes) -

Table 5.6 lists the selection of interrupt sources and interrupt source clear control by setting the DTA bit in DMDR of the DMAC, the DTCE bit in DTCERA to **DTCERE** of the DTC, and the DISEL bit in MRB of the DTC.

Section 8 Data Transfer Controller

Deletion of DTCERG, and DTCERH in DTCER

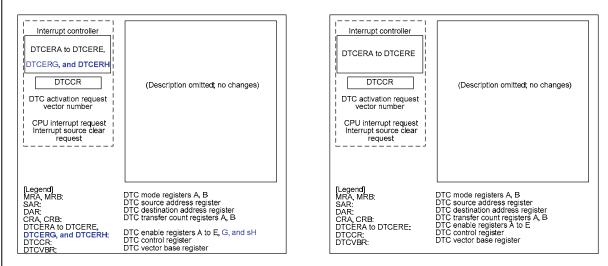

(1) Page 308, DTCER description in figure 8.1, Block Diagram of DTC

[Before Change]

#### [After Change]

(2) Page 309, section 8.2, Register Descriptions

Deletion of DTCERG, and DTCERH in DTCER

[Before Change]

• DTC enable registers A to E, G, and H (DTCERA to DTCERE, DTCERG, and DTCERH)

[After Change]

• DTC enable registers A to E (DTCERA to DTCERE)

# (3) Page 314, section 8.2.7, DTC Enable Register

Deletion of DTCERG, and DTCERH in DTCER

# [Before Change]

8.2.7 DTC enable registers A to E, G, and H (DTCERA to DTCERE, DTCERG, and DTCERH)

DTCER, which is comprised of eight registers, DTCERA to DTCERE, **DTCERG**, and **DTCERH**, is a register that specifies DTC activation interrupt sources.

#### [After Change]

8.2.7 DTC Enable Register A to E (DTCERA to DTCERE)

DTCER, which is comprised of five registers, DTCERA to DTCERE, is a register that specifies DTC activation interrupt sources.

#### Section 9 I/O Ports

(1) Page 380, table 9.5, Available Output Signald and Settings in Each Port

#### [Before Change]

| Port | Output<br>Specification<br>Signal Name | Output Signal<br>Name | Signal Selection<br>Register Settings | Peripheral Module Settings                              |

|------|----------------------------------------|-----------------------|---------------------------------------|---------------------------------------------------------|

| PA   | 1                                      | BACK_OE               | BACK                                  | SYSCRE.EXPE = 1, BCR1.BRLE = 1                          |

|      |                                        | (RD/WR)_OE            | RD/WR                                 | SYSCR.EXPE = 1, PFCR2.REWRE = 1 or<br>SRAMCR.BCSELn = 1 |

#### [After Change]

| Port | Output<br>Specification<br>Signal Name | Output Signal<br>Name | Signal Selection<br>Register Settings | Peripheral Module Settings                                      |

|------|----------------------------------------|-----------------------|---------------------------------------|-----------------------------------------------------------------|

| PA   | 1                                      | BACK_OE               | BACK                                  | SYSCRE.EXPE = 1, BCR1.BRLE = 1                                  |

|      |                                        | (RD/WR)_OE            | RD/WR                                 | SYSCR.EXPE = 1, PFCR2. <b>RDWRE</b> = 1 or<br>SRAMCR.BCSELn = 1 |

#### Section 12 8-Bit Timers (TMR)

(1) Description in section 12.7.2, A/D Converter Activation on page 525.

[Before Change]

The A/D converter can be activated only by TMR\_0 compare match A. \*

If the ADTE bit in TCSR\_0 is set to 1 when the CMFA flag in TCSR\_0 is set to 1 by the occurrence of TMR\_0 compare match A,

a request to start A/D conversion is sent to the A/D converter. If the 8-bit timer conversion start trigger has been selected on the

A/D converter side at this time, A/D conversion is started.

Note: \* Available only in unit 0 and unit 1.

#### [After Change]

The A/D converter can be activated only by TMR\_0 or TMR\_2 compare match A. \*

If the ADTE bit in TCSR\_0 is set to 1 when the CMFA flag in TCSR\_0 is set to 1 by the occurrence of compare match A, a

request to start A/D conversion is sent to the A/D converter. If the 8-bit timer conversion start trigger has been selected on the

A/D converter side at this time, A/D conversion is started.

Note: \* Available only in unit 0 and unit 1.

Γ

| efore Change]<br>erial Status Reg<br>• When SMI<br>Bit<br>Bit Name<br>Initial Value                                               |                                    |                                                                                                                  |                                                                                                                                    |                                      |        |      |             |                                 |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------|------|-------------|---------------------------------|

| When SMI Bit Bit Name Initial Value                                                                                               | IF in SCMR =                       |                                                                                                                  |                                                                                                                                    |                                      |        |      |             |                                 |

| Bit<br>Bit Name<br>Initial Value                                                                                                  |                                    |                                                                                                                  |                                                                                                                                    |                                      |        |      |             |                                 |

| Bit Name<br>Initial Value                                                                                                         | 7                                  | = 0                                                                                                              |                                                                                                                                    |                                      |        |      |             |                                 |

| Initial Value                                                                                                                     |                                    | 6                                                                                                                | 5                                                                                                                                  | 4                                    | 3      | 2    | 1           | 0                               |

|                                                                                                                                   | TDRE                               | RDRF                                                                                                             | ORER                                                                                                                               | FRE                                  | PER    | TEND | MPB         | MPBT                            |

|                                                                                                                                   | e 1                                | 0                                                                                                                | 0                                                                                                                                  | 0                                    | 0      | 1    | 0           | 0                               |

| R/W                                                                                                                               | R/(W)*                             | R/(W)*                                                                                                           | R/(W)*                                                                                                                             | R/(W)*                               | R/(W)* | R    | R           | R/W                             |

| Note: * On                                                                                                                        | lly 0 can be w                     | vritten, to cle                                                                                                  | ear the flag.                                                                                                                      |                                      |        |      |             |                                 |

|                                                                                                                                   |                                    |                                                                                                                  |                                                                                                                                    |                                      |        |      |             |                                 |

| fter Change]                                                                                                                      |                                    |                                                                                                                  |                                                                                                                                    |                                      |        |      |             |                                 |

| <ul> <li>When SMI</li> </ul>                                                                                                      | IF in SCMR <del>-</del>            | = 0                                                                                                              |                                                                                                                                    |                                      |        |      |             |                                 |

| Bit                                                                                                                               | 7                                  | 6                                                                                                                | 5                                                                                                                                  | 4                                    | 3      | 2    | 1           | 0                               |

| Bit Name                                                                                                                          | TDRE                               | RDRF                                                                                                             | ORER                                                                                                                               | FER                                  | PER    | TEND | MPB         | MPBT                            |

| Initial Value                                                                                                                     | 1                                  | 0                                                                                                                | 0                                                                                                                                  | 0                                    | 0      | 1    | 0           | 0                               |

| R/W                                                                                                                               | R/(W)*                             | R/(W)*                                                                                                           | R/(W)*                                                                                                                             | R/(W)*                               | R/(W)* | R    | R           | R/W                             |

| efore Change]<br>ble 14.3, Relat                                                                                                  | tionships be                       | etween N Se                                                                                                      |                                                                                                                                    |                                      |        | te B |             |                                 |

| synchronous (                                                                                                                     |                                    | etween N Se<br>Bit Rate<br>F                                                                                     | etween N Se                                                                                                                        |                                      |        | te B | D           | r <b>ror</b><br>escription omit |

| efore Change]<br><b>ible 14.3, Relat</b><br><b>ode</b><br>synchronous<br>ode                                                      | tionships be<br>ABCS Bit<br>0      | etween N Se<br>Bit Rate<br>B =                                                                                   | etting in BR                                                                                                                       | R and Bit F                          |        | te B | D           |                                 |

| efore Change]<br><b>ible 14.3, Relat</b><br><b>ode</b><br>synchronous<br>ode                                                      | tionships be<br>ABCS Bit           | etween N Se<br>Bit Rate<br>B = F<br>64 ×                                                                         | etween N Se<br>etting in BR<br>$P\phi \times 10^6$<br>$2^{2n-1} \times B$<br>$P\phi \times 10^6$                                   | R and Bit F                          |        | te B | D           | escription omit                 |

| efore Change]<br><b>ible 14.3, Relat</b><br><b>ode</b><br>synchronous<br>ode                                                      | tionships be<br>ABCS Bit<br>0      | etween N Se<br>Bit Rate<br>B = F<br>64 ×                                                                         | etting in BR                                                                                                                       | R and Bit F                          |        | te B | D           | escription omit                 |

| efore Change]<br>ble 14.3, Relat<br>ode<br>synchronous (<br>ode<br>fter Change]<br>ble 14.3, Relat<br>ode<br>synchronous (<br>ode | tionships be<br>ABCS Bit<br>0<br>1 | etween N Se<br>Bit Rate<br>$B = \frac{F}{64 \times R}$<br>$B = \frac{R}{32 \times R}$<br>etween N Se<br>Bit Rate | etween N Se<br>etting in BR<br>$p_{\phi} \times 10^{6}$<br>$\frac{2^{2n-1} \times B}{P \phi \times 10^{6}}$<br>$2^{2n-1} \times B$ | R and Bit F<br>1<br>1<br>R and Bit F | Rate B | te B | D<br>(n<br> | escription omit                 |

# Section 23 List of Registers

(1) Page 885, section 23.1 Register Addresses (Address Order)

# Deletion of DTCERG and DTCERH in DTCER

#### [Before Change]

| Register Name         | Abbreviation | Number<br>of Bits | Address        | Module | Data<br>Width | Access Cycles<br>(Read/Write) |

|-----------------------|--------------|-------------------|----------------|--------|---------------|-------------------------------|

|                       | – Desc       | ription omi       | tted (no chang | ges) – |               |                               |

| DTC enable register E | DTCERE       | 16                | H'FFF28        | INTC   | 16            | 2Ιφ/3Ιφ                       |

| DTC enable register G | DTCERG       | 16                | H'FFF2C        | INTC   | 16            | 2Ιφ/3Ιφ                       |

| DTC enable register H | DTCERH       | 16                | H'FFF2E        | INTC   | 16            | 2Ιφ/3Ιφ                       |

| DTC control register  | DTCCR        | 8                 | H'FFF30        | INTC   | 16            | 2Ιφ/3Ιφ                       |

|                       | – Desc       | ription omi       | tted (no chan  | ges) – |               |                               |

# [After Change]

| Register Name         | Abbreviation                                         | Number<br>of Bits | Address       | Module | Data<br>Width | Access Cycles<br>(Read/Write) |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------|-------------------|---------------|--------|---------------|-------------------------------|--|--|--|--|--|--|

|                       | – Desc                                               | ription omi       | tted (no chan | ges) – |               |                               |  |  |  |  |  |  |

| DTC enable register E | DTCERE                                               | 16                | H'FFF28       | INTC   | 16            | 2Ιφ/3Ιφ                       |  |  |  |  |  |  |

| DTC control register  | DTC control register DTCCR 8 H'FFF30 INTC 16 2lφ/3lφ |                   |               |        |               |                               |  |  |  |  |  |  |

|                       | – Desc                                               | ription omi       | tted (no chan | ges) – |               |                               |  |  |  |  |  |  |

(2) Page 899, section 23.2, Register Bits

Deletion of DTCERG, and DTCERH in INTC

# [Before Change]

| Register<br>Abbreviation                               | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module   |

|--------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|----------|

|                                                        |                   |                   | — C               | Description on    | nitted (no cha    | nges) –           |                  |                  | TPU_5    |

| DTCERA to<br>DTCERD                                    |                   |                   | – D               | escription om     | itted (no char    | nges) –           |                  |                  | INTC     |

| DTCERE                                                 | _                 | _                 | DTCEE13           | DTCEE12           | -                 | -                 | -                | -                | _        |

|                                                        | _                 | -                 | -                 | -                 | _                 | -                 | -                | _                | _        |

| DTCERG                                                 | -                 | -                 | -                 | -                 | DTCEG11           | DTCEG10           | -                | -                | _        |

|                                                        | DTCEG7            | DTCEG6            | -                 | -                 | -                 | -                 | -                | -                | _        |

| DTCERH                                                 | DTCEH15           | DTCEH14           | -                 | -                 | -                 | -                 | -                | -                | _        |

|                                                        | -                 | -                 | -                 | -                 | -                 | -                 | -                | -                | _        |

| DTCCR                                                  | -                 | -                 | -                 | RRS               | RCHNE             | -                 | -                | ERR              | _        |

| INTCR to ISR                                           |                   |                   | – D               | escription om     | itted (no char    | nges) –           |                  |                  | _        |

| <ul> <li>Description omitted (no changes) –</li> </ul> |                   |                   |                   |                   |                   |                   |                  |                  | I/O port |

| Register<br>Abbreviation                       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module   |

|------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|----------|

| — Description omitted (no changes) –           |                   |                   |                   |                   |                   |                   |                  |                  |          |

| DTCERA to – Description omitted (no changes) – |                   |                   |                   |                   |                   |                   |                  |                  | INTC     |

| DTCERE                                         | -                 | -                 | DTCEE13           | DTCEE12           | -                 | -                 | -                | -                |          |

|                                                | -                 | -                 | -                 | -                 | -                 | -                 | -                | -                |          |

| DTCCR                                          | -                 | -                 | -                 | RRS               | RCHNE             | -                 | -                | ERR              | -        |

| INTCR to ISR                                   |                   |                   | – D               | escription om     | itted (no chan    | iges) –           |                  |                  |          |

|                                                |                   |                   | – [               | Description or    | nitted (no cha    | nges) –           |                  |                  | I/O port |

(3) Page 912, section 23.3, Register States in Each Operating Mode

Deletion of DTCERG and DTCERH in INTC

# [Before Chenage]

| Register<br>Abbreviation | Reset       | Sleep | Module Stop                          | All-Module-<br>Clock-Stop            | Software<br>Standby | Hardware<br>Standby | Module   |  |  |  |  |

|--------------------------|-------------|-------|--------------------------------------|--------------------------------------|---------------------|---------------------|----------|--|--|--|--|

|                          |             |       | <ul> <li>Description of</li> </ul>   | mitted (no chang                     | es) –               |                     | TPU_5    |  |  |  |  |

| DTCERA to<br>DTCERD      |             |       | - Description omitted (no changes) - |                                      |                     |                     |          |  |  |  |  |

| DTCERE                   | Initialized | -     | _                                    | -                                    | _                   | Initialized         | _        |  |  |  |  |

| DTCERG                   | Initialized | -     | -                                    | -                                    | -                   | Initialized         | _        |  |  |  |  |

| DTCERH                   | Initialized | -     | -                                    | -                                    | -                   | Initialized         | _        |  |  |  |  |

| DTCCR                    | Initialized | -     | _                                    | -                                    | _                   | Initialized         | _        |  |  |  |  |

| INTCR to ISR             |             |       | <ul> <li>Description of</li> </ul>   | - Description omitted (no changes) - |                     |                     |          |  |  |  |  |

|                          |             |       | <ul> <li>Description of</li> </ul>   | mitted (no chang                     | es) –               |                     | I/O port |  |  |  |  |

# [After Change]

| Register<br>Abbreviation | Reset       | Sleep | Module Stop                        | Module                                                 |        |             |          |  |  |  |  |

|--------------------------|-------------|-------|------------------------------------|--------------------------------------------------------|--------|-------------|----------|--|--|--|--|

|                          |             |       | <ul> <li>Description of</li> </ul> | <ul> <li>Description omitted (no changes) –</li> </ul> |        |             |          |  |  |  |  |

| DTCERA to<br>DTCERD      |             |       | - Description of                   | <ul> <li>Description omitted (no changes) –</li> </ul> |        |             |          |  |  |  |  |

| DTCERE                   | Initialized | -     | -                                  | -                                                      | -      | Initialized | _        |  |  |  |  |

| DTCCR                    | Initialized | -     | -                                  | – – – Initialized                                      |        |             |          |  |  |  |  |

| INTCR to ISR             |             |       | <ul> <li>Description of</li> </ul> | <ul> <li>Description omitted (no changes) –</li> </ul> |        |             |          |  |  |  |  |

|                          |             |       | <ul> <li>Description of</li> </ul> | omitted (no chang                                      | ies) – |             | I/O port |  |  |  |  |