Date: May. 22, 2015

## RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                        |          | Document<br>No.         | TN-SH7-A899A/E         | Rev. | 1.00 |

|-----------------------|------------------------------------------------|----------|-------------------------|------------------------|------|------|

| Title                 | Clearing of flags upon DTC transfer in RCAN-ET |          | Information<br>Category | Technical Notification |      |      |

| Applicable<br>Product | See below.                                     | Lot No.  |                         | See below.             |      |      |

|                       |                                                | All lots | Reference<br>Document   |                        |      |      |

We would like to inform you of the correction of errors in the user's manuals listed below. Please refer to the following for details.

[Corrections in the User's Manuals]

The corrections of the user's manuals are described below using the SH7214 Group, SH7216 Group User's Manual: Hardware as an example.

## 21.6 DTC Interface

[Before correction (p. 1121)]

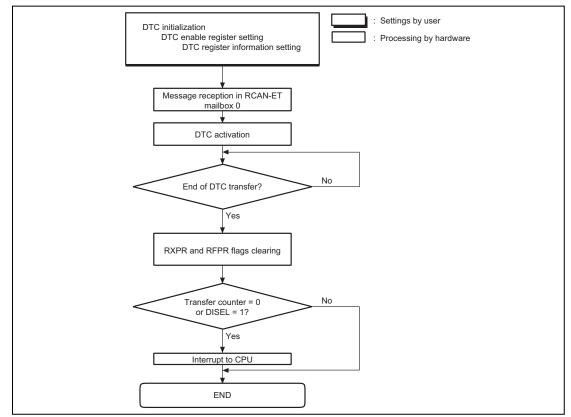

The DTC can be activated by the reception of a message in RCAN-ET mailbox 0. When DTC transfer ends after DTC activation has been set, flags of RXPR0 and RFPR0 are cleared automatically. An interrupt request due to a receive interrupt from the RCAN-ET cannot be sent to the CPU in this case. Figure 21.14 shows a DTC transfer flowchart.

Figure 21.14 DTC Transfer Flowchart

[After correction (p. 1121)]

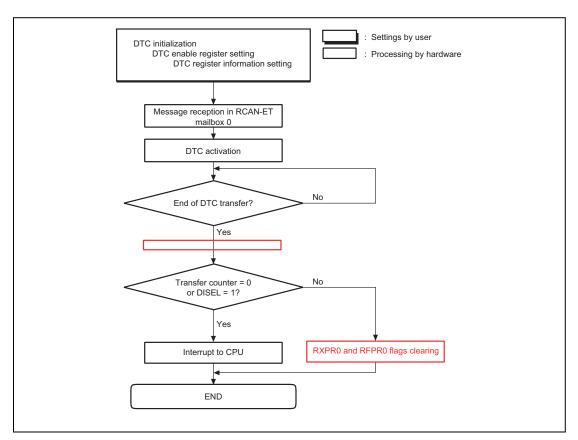

The DTC can be activated by the reception of a message in RCAN-ET mailbox 0. When DTC transfer ends after DTC activation has been set, flags of RXPR0 and RFPR0 are cleared automatically (except when the transfer counter = 0 or DISEL = 1). An interrupt request due to a receive interrupt from the RCAN-ET cannot be sent to the CPU in this case. However, when the transfer counter = 0 or DISEL = 1, an interrupt is sent to the CPU. Figure 21.14 shows a DTC transfer flowchart.

Figure 21.14 DTC Transfer Flowchart

[Applicable Products and Reference Documents]

| Series | Group           | Reference Document                                 | Rev. | Ref. No.        |

|--------|-----------------|----------------------------------------------------|------|-----------------|

| SH7216 | SH7214, SH7216  | SH7214 Group, SH7216 Group User's Manual: Hardware | 4.00 | R01UH0230EJ0400 |

| SH7231 | SH7231          | SH7231 Group User's Manual: Hardware               | 2.00 | R01UH0073EJ0200 |

| SH7239 | SH7237, SH7239  | SH7239 Group, SH7237 Group User's Manual: Hardware | 2.00 | R01UH0086EJ0200 |

| SH7280 | SH7286          | SH7280 Group, SH7243 Group User's Manual: Hardware | 3.00 | R01UH0229EJ0300 |

| SH7137 | SH7131, SH7132, | SH7137 Group Hardware Manual                       | 3.00 | REJ09B0402-0300 |

|        | SH7136, SH7137  |                                                    |      |                 |

**End of Document**

Date: May 22, 2015