Date: Mar. 27, 2014

# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category    | MPU/MCU                                                   |         | Document<br>No.         | TN-R8C-A040A/E         | Rev. | 1.00 |

|------------------------|-----------------------------------------------------------|---------|-------------------------|------------------------|------|------|

| Title                  | Changes in the Voltage Monitor 2 Interrupt Specifications |         | Information<br>Category | Technical Notification |      |      |

| Applicable<br>Products | See below                                                 | Lot No. | Reference<br>Document   |                        |      |      |

Specifications for the voltage monitor 2 interrupt have been partially modified in the products below.

## 1. Applicable products:

R8C/11 Group, R8C/13 Group,

R8C/14 Group, R8C/15 Group, R8C/16 Group, R8C/17 Group

R8C/18 Group, R8C/19 Group, R8C/1A Group, R8C/1B Group

## 2. Change:

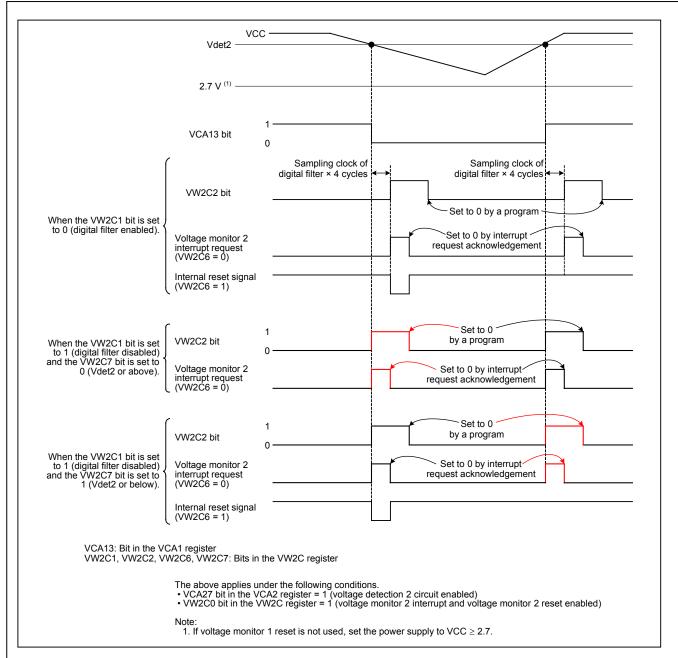

When in voltage monitor 2 interrupt mode (VW2C6 bit in the VW2C register is 0), regardless of the setting of the VW2C1 bit in the VW2C register (voltage monitor 2 digital filter disabled mode select bit), an interrupt request is generated when Vdet2 > VCC and when VCC > Vdet2.

Date: Mar. 27, 2014

3. Examples of changes to the hardware manual (R8C/1A Group, R8C/1B Group (REJ09B0252-0130)).

Table 7.1 Specifications of Voltage Detection Circuit

| Ite                     | em                 | Voltage Detection 1        | Voltage Detection 2        |  |  |

|-------------------------|--------------------|----------------------------|----------------------------|--|--|

| VCC monitor             | Voltage to monitor | Vdet1                      | Vdet2                      |  |  |

|                         | Detection target   | Passing through Vdet1      | Passing through Vdet2      |  |  |

|                         |                    | by rising or falling       | by rising or falling       |  |  |

|                         | Monitor            | None                       | VCA13 bit in VCA1          |  |  |

|                         |                    |                            | register                   |  |  |

|                         |                    |                            | Whether VCC is higher      |  |  |

|                         |                    |                            | or lower than Vdet2        |  |  |

| Process when voltage is | Reset              | Voltage monitor 1 reset    | Voltage monitor 2 reset    |  |  |

| detected                |                    | Reset at Vdet1 > VCC;      | Reset at Vdet2 > VCC;      |  |  |

|                         |                    | restart CPU operation at   | restart CPU operation      |  |  |

|                         |                    | VCC > Vdet1                | after a specified time     |  |  |

|                         | Interrupt          | None                       | Voltage monitor 2          |  |  |

|                         |                    |                            | interrupt                  |  |  |

|                         |                    |                            | Interrupt request at       |  |  |

|                         |                    |                            | Vdet2 > VCC and VCC >      |  |  |

|                         |                    |                            | Vdet2 when digital filter  |  |  |

|                         |                    |                            | is enabled;                |  |  |

|                         |                    |                            | interrupt request at       |  |  |

|                         |                    |                            | Vdet2 > VCC or VCC >       |  |  |

|                         |                    |                            | Vdet2 when digital filter  |  |  |

| D::t-1 6:t              | O it - I.          | A !! - ! - ! -             | is disabled                |  |  |

| Digital filter          | Switch             | Available                  | Available                  |  |  |

|                         | enabled/disabled   | (Divide less est (DINIO O) | (Distribution of (DINIO O) |  |  |

|                         | Sampling time      | (Divide-by-n of fRING-S)   | (Divide-by-n of fRING-S)   |  |  |

|                         |                    | x 4                        | x 4                        |  |  |

|                         |                    | n: 1, 2, 4, and 8          | n: 1, 2, 4, and 8          |  |  |

Interrupt request at Vdet2 > VCC and VCC > Vdet2

#### NOTES:

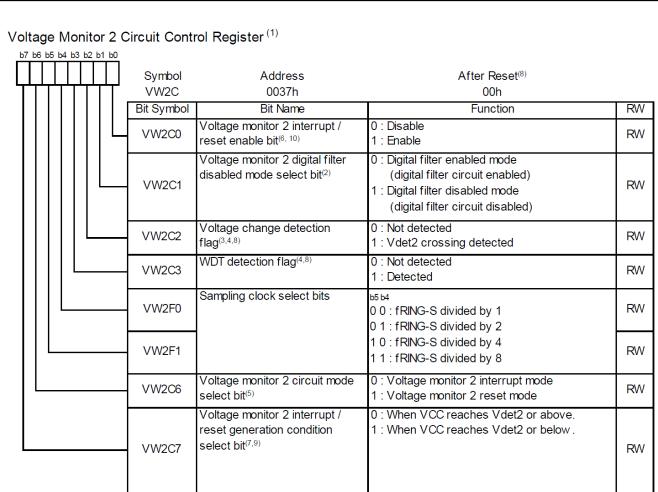

- 1. Set the PRC3 bit in the PRCR register to 1 (rew rite enable) before w riting to this register. When rew riting the VW2C register, the VW2C2 bit may be set to 1. Set the VW2C2 bit to 0 after rew riting the VW2C

- 2. When the voltage monitor 2 interrupt is used to exit stop mode and to return again, write 0 to the VW2C1 bit before writing 1.

- 3. This bit is enabled when the VCA27 bit in the VCA2 register is set to 1 (voltage detection 2 circuit enabled).

- 4. Set this bit to 0 by a program. When 0 is written by a program, it is set to 0 (and remains unchanged even if 1 is w ritten to it).

- This bit is enabled when the VW2C0 bit is set to 1 (voltage monitor 2 interrupt/reset enabled).

- 6. The VW2C0 bit is enabled when the VCA27 bit in the VCA2 register is set to 1 (voltage detection 2 circuit enabled). Set the VW2C0 bit to 0 (disable) when the VCA27 bit is set to 0 (voltage detection 2 circuit disabled).

- 7. The VW2C7 bit is enabled when the VW2C1 bit is set to 1 (digital filter disabled mode).

- Bits VW2C2 and VW2C3 remain unchanged after a software reset, watchdog timer reset, or voltage monitor 2 reset.

- 9. When the VW2C6 bit is set to 1 (voltage monitor 2 reset mode), set the VW2C7 bit to 1 (when VCC reaches Vdet2 or below). (Do not set to 0.)

- 10. Set the VW2C0 bit to 0 (disabled) when the VCA13 bit in the VCA1 register is set to 1 (VCC ≥ Vdet2 or voltage detection 2 circuit disabled), the VW2C1 bit is set to 1 (digital filter disabled mode), and the VW2C7 bit is set to 0 (when VCC reaches Vdet2 or above).

- Set the VW2C0 bit to 0 (disabled) when the VCA13 bit is set to 0 (VCC < Vdet2), the VW2C1 bit is set to 1 (digital filter disabled mode), and the VW2C7 bit is set to 1 (when VCC reaches Vdet2 or below).

Figure 7.6 VW2C Register

The VW2C7 bit is disabled when the VW2C6 bit is 0 (voltage monitor 2 interrupt mode).

Figure 7.9 Operating Example of Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset

Date: Mar. 27, 2014

Table 7.3 Setting Procedure of Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset

Associated Bits

|      | When Using Digital Filter                                                                    |                   | When Not Using Digital Filter                                                                               |                                                                             |  |  |

|------|----------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Step | Voltage Monitor 2                                                                            | Voltage Monitor 2 | Voltage Monitor 2                                                                                           | Voltage Monitor 2                                                           |  |  |

|      | Interrupt                                                                                    | Reset             | Interrupt                                                                                                   | Reset                                                                       |  |  |

| 1    | Set the VCA27 bit in the VCA2 register to 1 (voltage detection 2 circuit enabled).           |                   |                                                                                                             |                                                                             |  |  |

| 2    | Wait for td(E-A)                                                                             |                   |                                                                                                             |                                                                             |  |  |

| 3(2) | Select the sampling clock of the digital filter by bits VW2F0 to VW2F1 in the VW2C register. |                   | Select the timing of the interrupt and reset request by the VW2C7 bit in the VW2C register <sup>(1)</sup> . |                                                                             |  |  |

| 4(2) | Set the VW2C1 bit in the VW2C register to 0 (digital filter enabled).                        |                   | Set the VW2C1 bit in the VW2C register to 1 (digital filter disabled).                                      |                                                                             |  |  |

| 5(2) | Set the VW2C6 bit in the VW2C register to 0 (voltage monitor 2 interrupt mode).              |                   | Set the VW2C6 bit in<br>the VW2C register to<br>0 (voltage monitor 2<br>interrupt mode).                    | Set the VW2C6 bit in the VW2C register to 1 (voltage monitor 2 reset mode). |  |  |

| 6    | Set the VW2C2 bit in the VW2C register to 0 (passing of Vdet2 is not detected).              |                   |                                                                                                             |                                                                             |  |  |

| 7    | Set the CM14 bit in the CM1 register to 0 (low-speed on-chip oscillator on).                 |                   | _                                                                                                           |                                                                             |  |  |

| 8    | Wait for 4 cycles of the sampling clock of the digital filter                                |                   | - (No wait time)                                                                                            |                                                                             |  |  |

| 9    | Set the VW2C0 bit in the VW2C register to 1 (voltage monitor 2 interrupt/reset enabled).     |                   |                                                                                                             |                                                                             |  |  |

#### NOTES:

- 1. Set the VW2C7 bit to 1 (when VCC reaches Vdet2 or below) for the voltage monitor 2 reset.

- 2. When the VW2C0 bit is set to 0 (disabled), steps 3, 4 and 5 can be executed simultaneously (with 1 instruction).