## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Sep. 28, 2009

## **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category                    | MPU/MCU                                                                                         |               | Docu<br>No     |               | TN-SH7-A739A/E Rev.    |                                                | 1.00               |            |       |

|----------------------------------------|-------------------------------------------------------------------------------------------------|---------------|----------------|---------------|------------------------|------------------------------------------------|--------------------|------------|-------|

| Title                                  | Additional specs concerning SH7265 electric characteristic tRDH3                                |               | Inform<br>Cate |               | Technical Notification |                                                |                    |            |       |

|                                        |                                                                                                 |               | Lot No.        |               |                        |                                                |                    |            |       |

| Applicable<br>Product                  | SH7265 Group                                                                                    | All           |                | Refer<br>Docu |                        | SH7265 Group Hardware Manual (REJ09B0351-0100) |                    |            |       |

| 1) Addition t                          | ify you of the addition of the boot of the Table 36.8 Bus Timing ents before manual correction] |               | data hold t    | ime 3 (tF     | RDH3) o                | f electric cha                                 | aracteristic c     | of SH7265  | i.    |

| Table 36.8 Bus Timing                  |                                                                                                 |               |                | Bφ=66.66MHz * |                        |                                                |                    |            |       |

| Item                                   |                                                                                                 | Symbo I       |                | Min. Max.     |                        | Unit                                           | Figure             |            |       |

|                                        |                                                                                                 |               |                |               |                        |                                                |                    |            |       |

|                                        |                                                                                                 |               |                |               |                        |                                                |                    |            |       |

| Read data hold time 2<br>(SDRAM space) |                                                                                                 | tRDH2         |                | 2             | -                      | ns                                             | Figures 3<br>36.20 | 6. 16, 36. | 18,   |

| Read/writ                              | te mode delay time                                                                              | trwm          |                | 1             | 13                     | ns                                             | Figures 3          | 6.11 to 3  | 6. 15 |

|                                        |                                                                                                 |               |                |               |                        |                                                |                    |            |       |

|                                        |                                                                                                 |               |                |               |                        |                                                |                    |            |       |

| [The conte                             | nts after manual correction]                                                                    |               |                | D.4 -60       | ccuu-                  |                                                |                    |            |       |

| [The conte                             | nts after manual correction]                                                                    | Symbol        | _              |               | . 66MHz                | *Unit                                          | Figure             |            |       |

|                                        | nts after manual correction]                                                                    | Symbol        | _              | Bφ=66<br>Min. | . 66MHz<br>Max.        |                                                | Figure             |            |       |

|                                        | nts after manual correction]                                                                    | Symbol        | _              |               |                        |                                                | Figure             |            |       |

| Item                                   | a hold time 2                                                                                   | Symbol  TRDH2 |                |               |                        |                                                | Figure Figures 3   | 6. 16, 36. | 18,   |

| Read data<br>(SDRAM sp                 | a hold time 2 pace)                                                                             |               |                | Min.          |                        | Unit                                           | Figures 3          | -          |       |

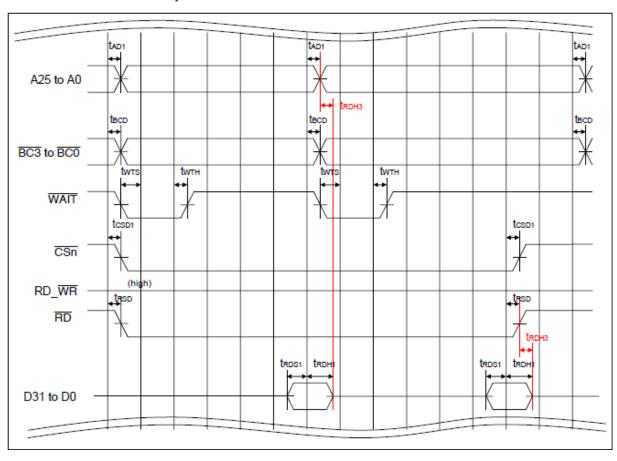

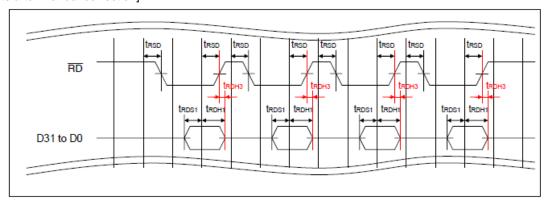

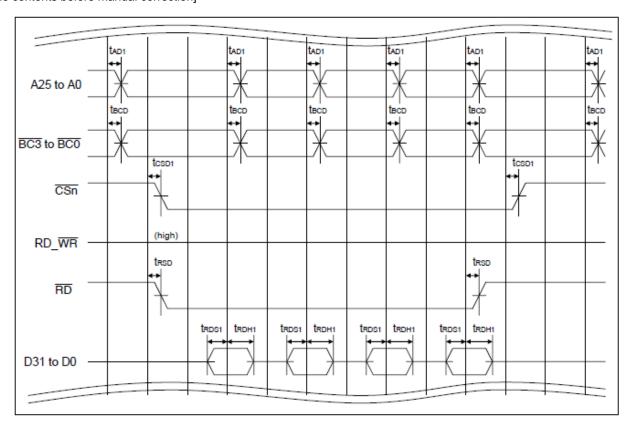

(2) Figure 36.11 External Address Space: Basic Bus Timing (Normal Access, Cycle Wait Control, CS Extended Cycle)

[The contents before manual correction]

[The contents after manual correction]

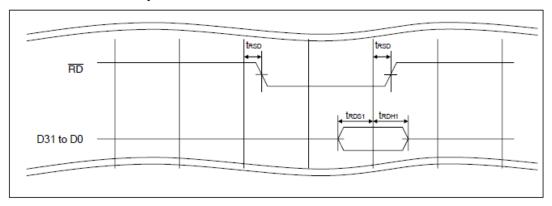

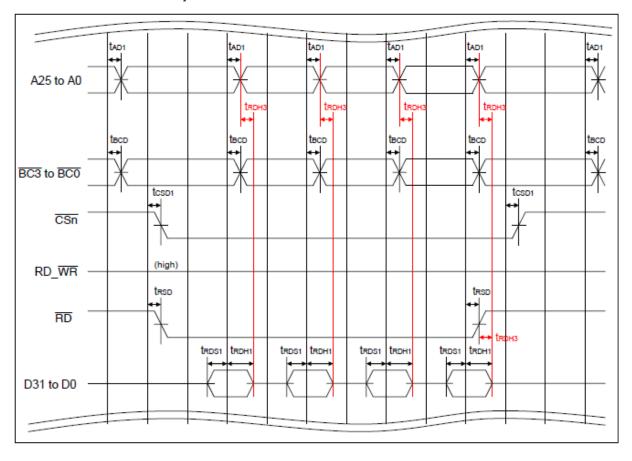

(3) Figure 36.12 External Address Space: Basic Bus Timing (Page Read Access, Normal Access Compatible Mode)

[The contents before manual correction]

[The contents after manual correction]

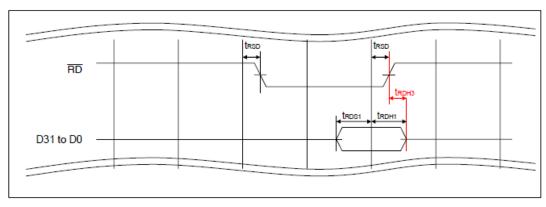

(4) Figure 36.13 External Address Space: Basic Bus Timing (Page Read Access, External Read Data Continuous Assert Mode)

[The contents before manual correction]

[The contents after manual correction]

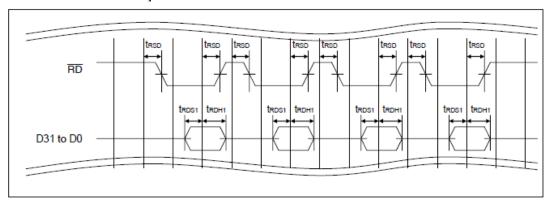

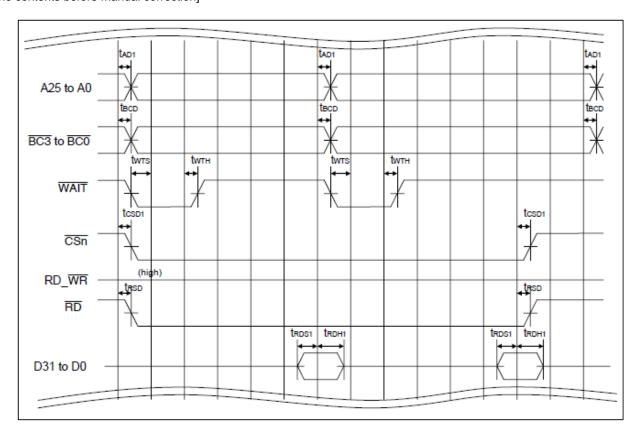

(5) Figure 36.15 External Address Space: Timing with External Wait (Page Read Access to 16-bit Width Channel, External Read Data Continuous Asser Mode)

[The contents before manual correction]

[The contents after manual correction]