# RC32504A (FemtoClock®2)

ITU-T G.8262 and G.8262.1 Compliance

#### **Overview**

This report describes the results for the compliance testing of Renesas' RC32504A PLL as per the standard ITU-T G.8262 and G.8262.1 for wander generation, wander transfer, phase transient tolerance, phase transient due to synchronization rearrangement operations, and holdover.

#### **Contents**

| 1.  | Description of Tests and Setup                         |                                                                    |    |  |

|-----|--------------------------------------------------------|--------------------------------------------------------------------|----|--|

| 2.  | PLL:                                                   | LL Settings Information4                                           |    |  |

| 3.  | Frequency Accuracy                                     |                                                                    |    |  |

|     | 3.1                                                    | Option 1                                                           |    |  |

|     | 3.2                                                    | Option 2                                                           | 4  |  |

|     | 3.3                                                    | Enhanced or for Both Options 1/2                                   | 4  |  |

| 4.  | Pull-                                                  | in, Hold-in, and Pull-out Ranges                                   | 4  |  |

| 5.  | Noise (Wander) Generation and Holdover Performance     |                                                                    |    |  |

|     | 5.1                                                    | Wander in Locked Mode – G8262_EEC1_1Hz                             | 6  |  |

|     | 5.2                                                    | Long-term Phase Transient Response – G8262_EEC1_1Hz                | 8  |  |

|     | 5.3                                                    | Wander in Locked Mode – G8262_EEC1_10Hz                            | 10 |  |

|     | 5.4                                                    | Long-term Phase Transient Response – G8262_EEC1_10Hz <sup>[]</sup> | 12 |  |

|     | 5.5                                                    | Wander in Locked Mode – G8262_EEC2                                 | 14 |  |

|     | 5.6                                                    | Long-term Phase Transient Response – G8262_EEC2 <sup>[]</sup>      | 16 |  |

|     | 5.7                                                    | Wander in Locked Mode – G8262_eEEC_3Hz                             | 18 |  |

|     | 5.8                                                    | Long-term Phase Transient Response - G8262_eEEC_3Hz []             | 20 |  |

| 6.  | Noise                                                  | e Tolerance                                                        | 22 |  |

| 7.  | Jitte                                                  | Tolerance                                                          | 22 |  |

| 8.  | Noise                                                  | e (Wander) Transfer                                                | 22 |  |

|     | 8.1                                                    | Noise Transfer – G8262_EEC1_1Hz                                    | 23 |  |

|     | 8.2                                                    | Noise Transfer – G8262_EEC1_10Hz                                   | 24 |  |

|     | 8.3                                                    | Noise Transfer – G8262_EEC1_10Hz                                   | 25 |  |

| 9.  | (Pha                                                   | se) Transient Response – Short-term                                | 26 |  |

|     | 9.1                                                    | Short-term Phase Transient – G8262_EEC1_1Hz                        | 27 |  |

|     | 9.2                                                    | Short-term Phase Transient – G8262_EEC1_10Hz                       | 29 |  |

|     | 9.3                                                    | Short-term Phase Transient – G8262_EEC2                            | 31 |  |

|     | 9.4                                                    | Short-term Phase Transient – G8262_eEEC1_3Hz                       | 33 |  |

| 10. | (Phase) Transient Response - Input Signal Interruption |                                                                    |    |  |

|     | 10.1                                                   | Phase Response to Input Signal Interruptions – G8262_EEC1_1Hz      | 36 |  |

|     | 10.2                                                   | Phase Response to Input Signal Interruptions – G8262_EEC1_10Hz     | 38 |  |

|     | 10.3                                                   | Phase Response to Input Signal Interruptions – G8262_EEC2          | 40 |  |

### RC32504A ITU-T G.8262 and G.8262.1 Compliance Test Report

| 13. | Revision History                                                    | 53 |

|-----|---------------------------------------------------------------------|----|

| 12. | Interfaces                                                          | 53 |

|     | 11.4 Phase Discontinuity – G8262_eEEC1_3Hz                          | 51 |

|     | 11.3 Phase Discontinuity – G8262_EEC2                               |    |

|     | 11.2 Phase Discontinuity – G8262_EEC1_10Hz                          |    |

|     | 11.1 Phase Discontinuity – G8262_EEC1_1Hz                           | 45 |

| 11. | (Phase) Transient Response - Phase Discontinuity                    | 44 |

|     | 10.4 Phase Response to Input Signal Interruptions – G8262_eEEC1_3Hz | 42 |

|     |                                                                     |    |

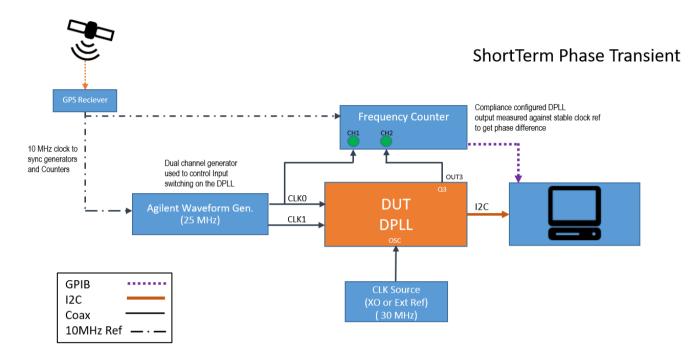

### 1. Description of Tests and Setup

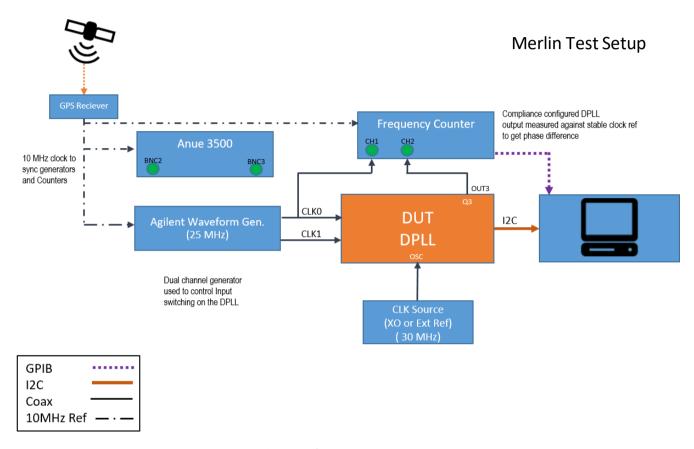

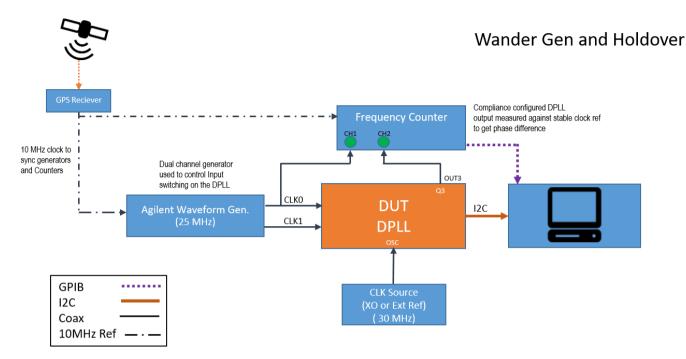

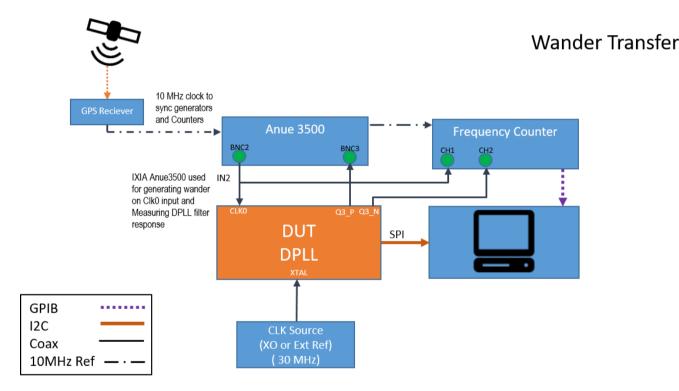

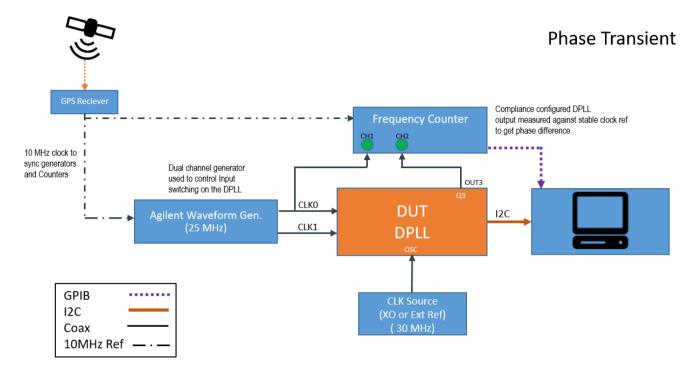

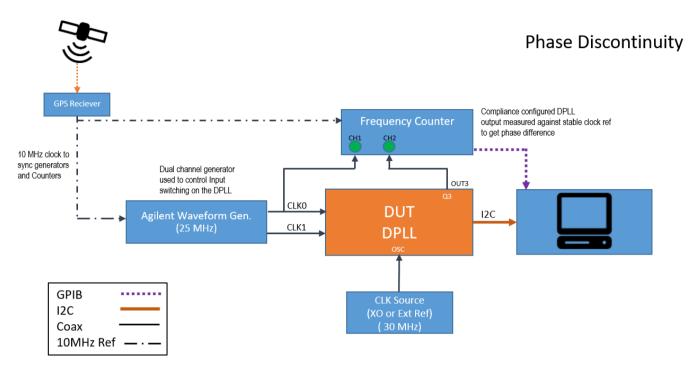

The synchronization rearrangement of the network is introduced through automatic reference switching between two clock inputs or through disconnecting the qualified reference clock input. Calnex Paragon-X is used to introduce and measure wander to and from the system while an Agilent frequency generator introduces phase transients. The measurement of phase transients is handled by a Keysight frequency counter.

The test setup is illustrated in the following diagram.

Figure 1. Complete Test setup

The Symmetricom TimeProvider acts as a stable and accurate clock source locked to GPS. Its 10MHz clock output serves as the 10MHz reference clock for the Agilent 33250A function generator, 53230A frequency counter, and Paragon-X. The DUT will lock to the reference clock input generated either through 33250A Function Generator or Paragon-X. The Renesas PLL can lock to virtually any frequency from 1MHz to 1GHz and produce virtually any output frequency from 1MHz to 1GHz. The Renesas PLL supports digital Low-pass filter whose bandwidth and Phase slope limit is set based on the standard ITU-T G.8262 Opt1/Opt2 or ITU-T G.8262.1 to test their compliances. Fractional Frequency Offset (FFO) and Maximum Time Interval Error (MTIE) plots are calculated from the measurements taken from 53230A frequency counter. The objective maximum FFO and the MTIE plots throughout each test have the mask specified in the standard.

### 2. PLL Settings Information

Table 1. PLL Settings based on Compliance Standard Table

| Compliance<br>Standard No. | Input/Output<br>Frequency<br>(MHz) | PLL<br>Bandwidth<br>(Hz) | Phase Slope<br>Limit (us/s) | Max Phase<br>Lock Error<br>(ns) | Phase<br>Monitor<br>Duration (s) | Gain Peaking<br>Control |

|----------------------------|------------------------------------|--------------------------|-----------------------------|---------------------------------|----------------------------------|-------------------------|

| ITUT-G.8262 Option 1       | 25.00                              | 1.2/3.0/10.0             | 7.500                       | 250                             | 10                               | < 0.2 dB                |

| ITUT-G.8262 Option 2       | 25.00                              | 0.1                      | 0.885                       | 250                             | 10                               | < 0.2 dB                |

| ITUT-G.8262.1 eEEC         | 25.00                              | 1.2/3.0                  | 7.500                       | 250                             | 10                               | < 0.2 dB                |

### 3. Frequency Accuracy

Frequency accuracy at free-run is determined by the system oscillator used. For more information, see <u>AN-807</u> Recommended Crystal Oscillator for Network Synchronization.

#### **3.1** Option 1

Refer to section G.813 Option 1 / G.8262 Option 1 (Table 8).

#### 3.2 **Option 2**

Refer to section GR-1244-CORE and GR-253-CORE Stratum 3 / G.812 Type IV / G.8262 Option 2 (Table 7).

#### 3.3 Enhanced or for Both Options 1/2

Refer to section G.8262.1 Enhanced Synchronous Ethernet/OTN Equipment Clock (Table 6).

# 4. Pull-in, Hold-in, and Pull-out Ranges

The RC32504A PLL supports a pull-range of ±244ppm. Per-input activity monitors can be used to define a pull-in/hold-in range with accuracy 0.926ppm. Thus, to support a ±4.6ppm pull-in/hold-in with a standard 4.6ppm XO, you can set the activity monitor to 9.26ppm.

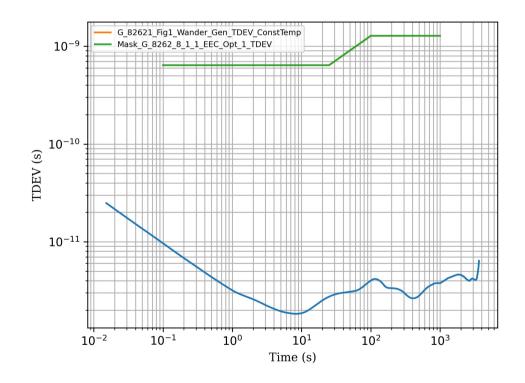

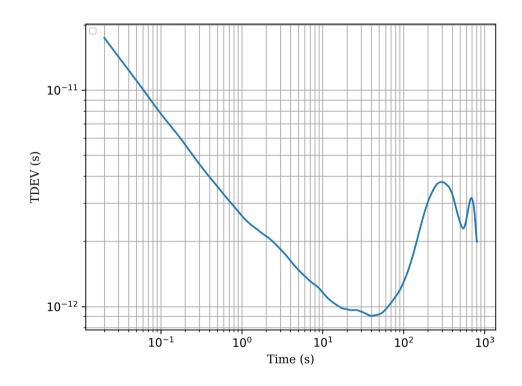

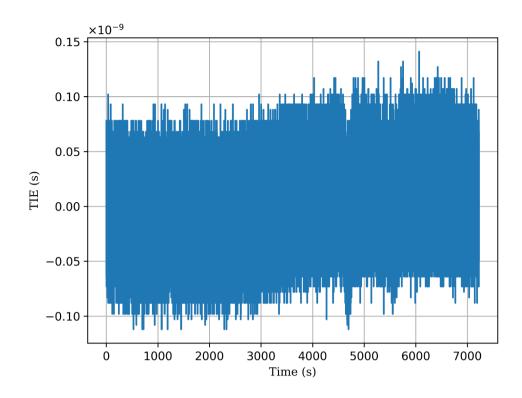

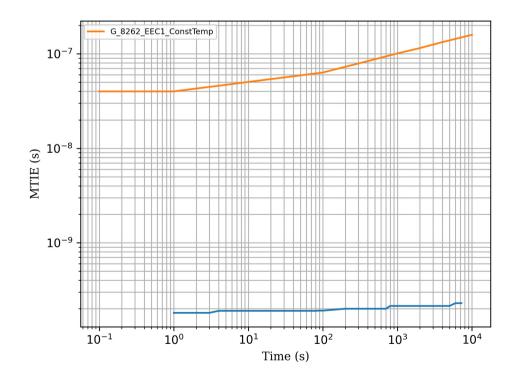

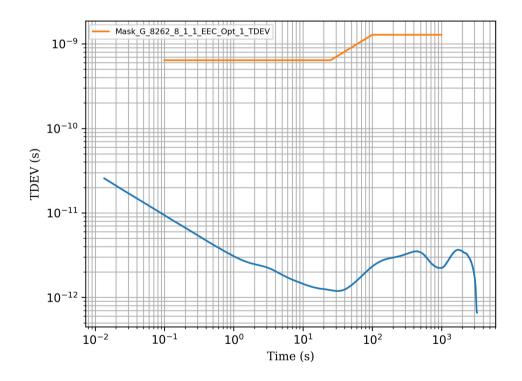

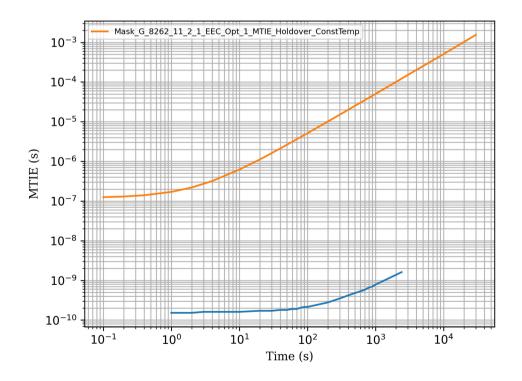

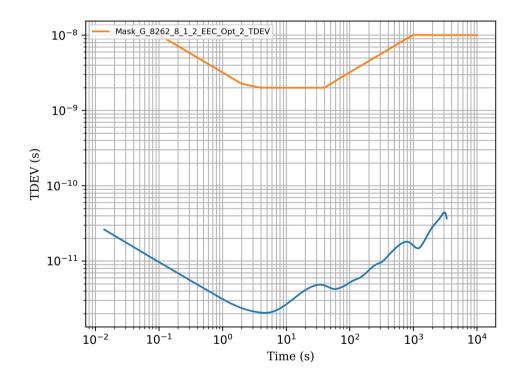

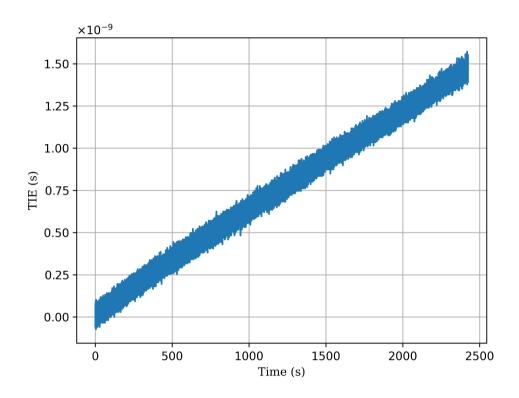

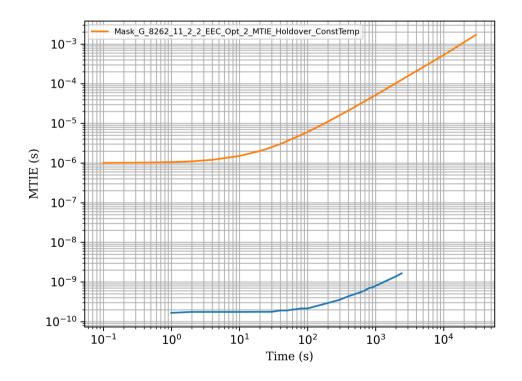

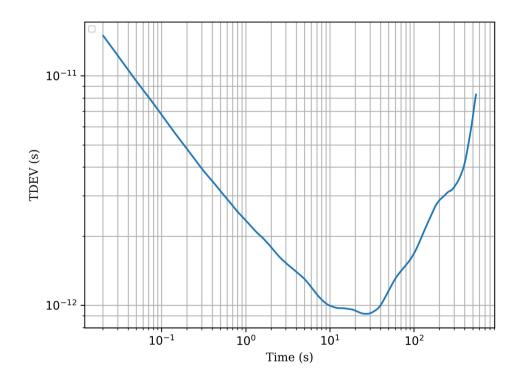

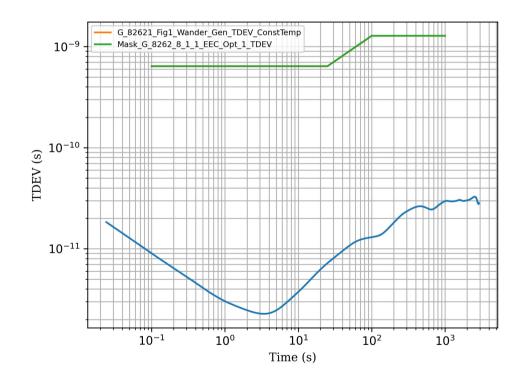

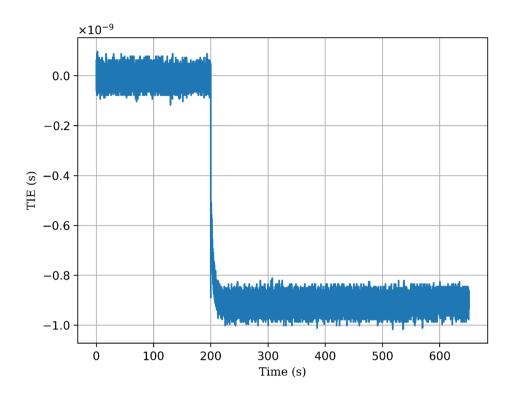

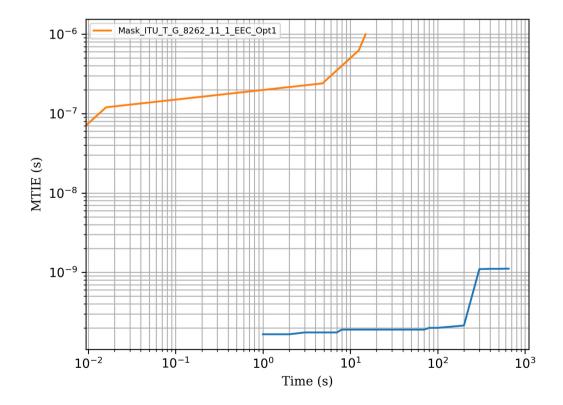

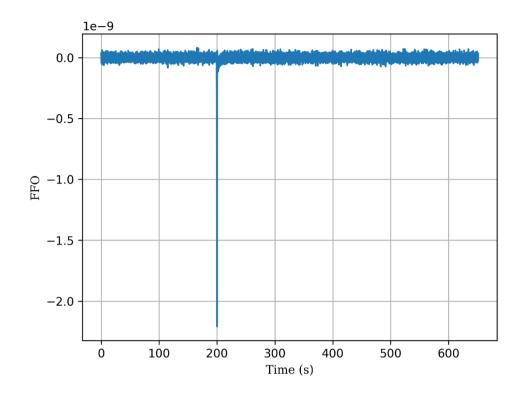

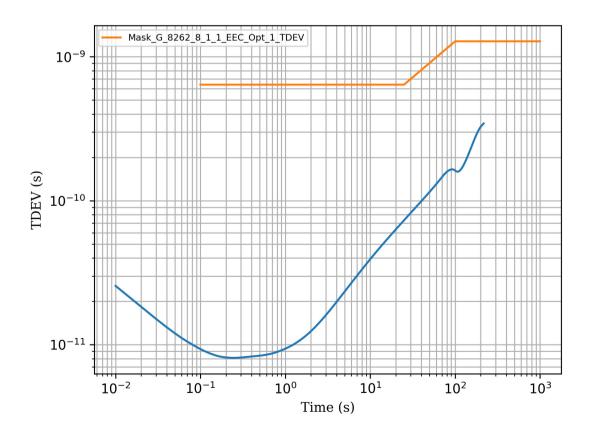

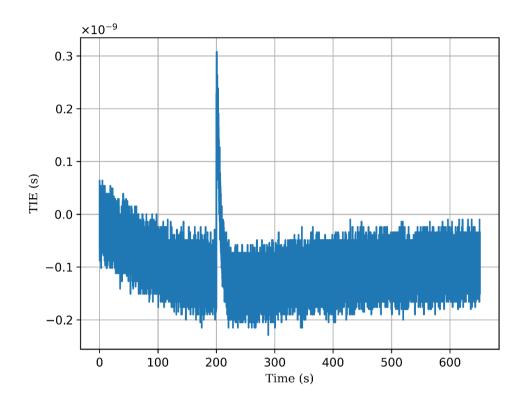

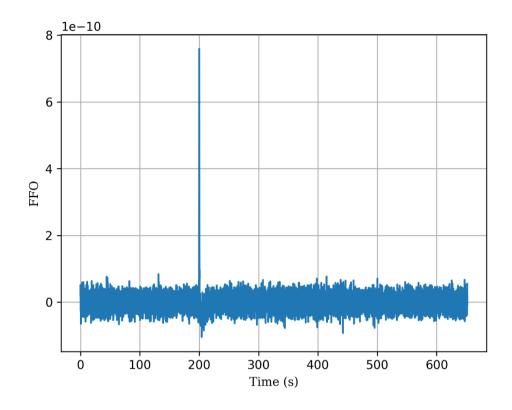

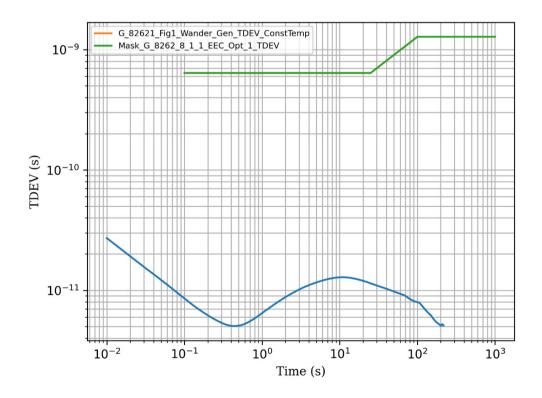

### 5. Noise (Wander) Generation and Holdover Performance

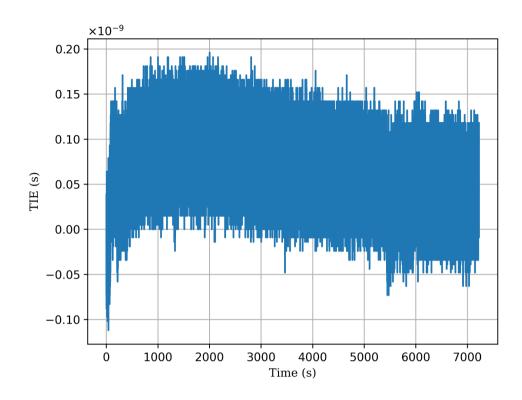

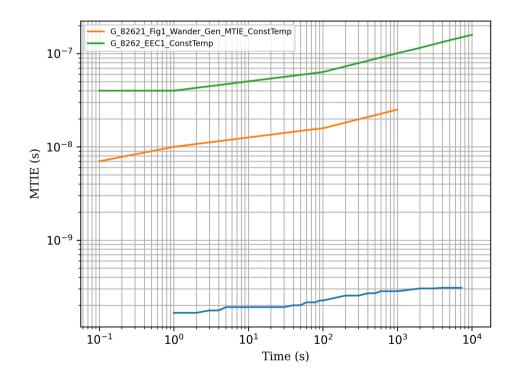

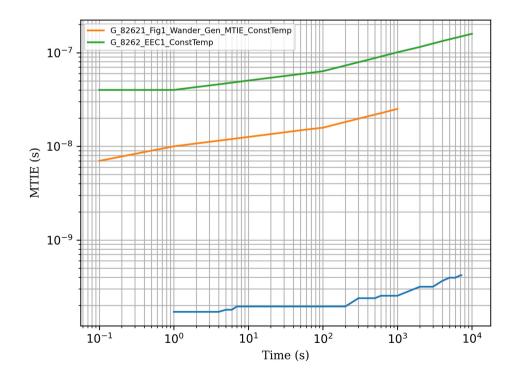

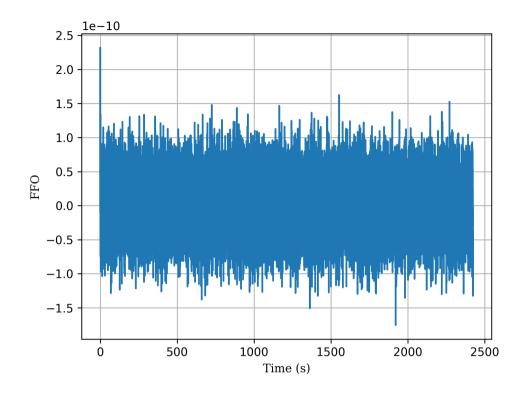

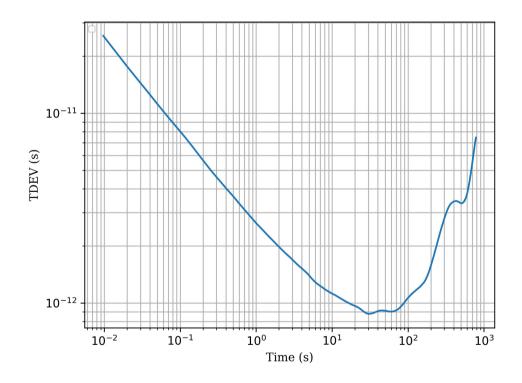

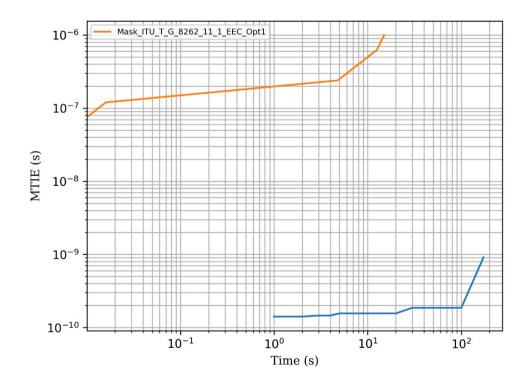

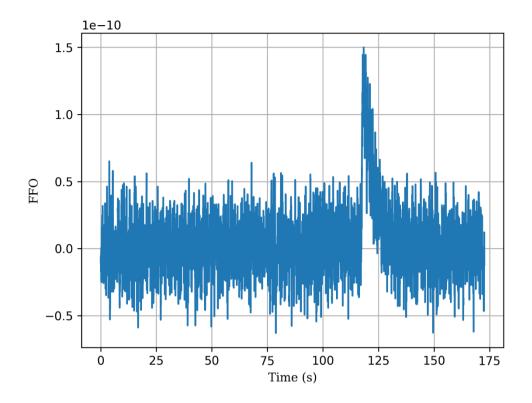

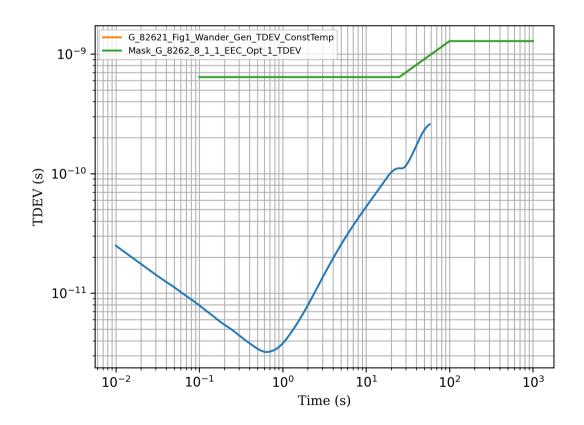

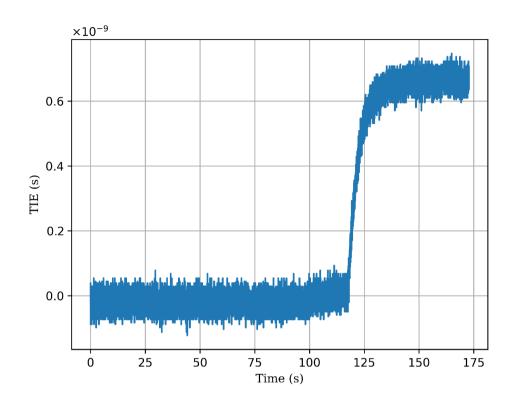

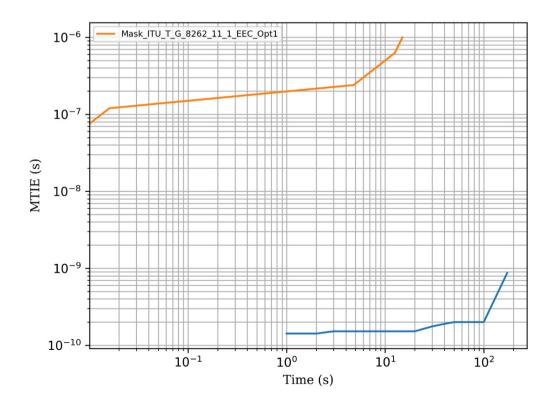

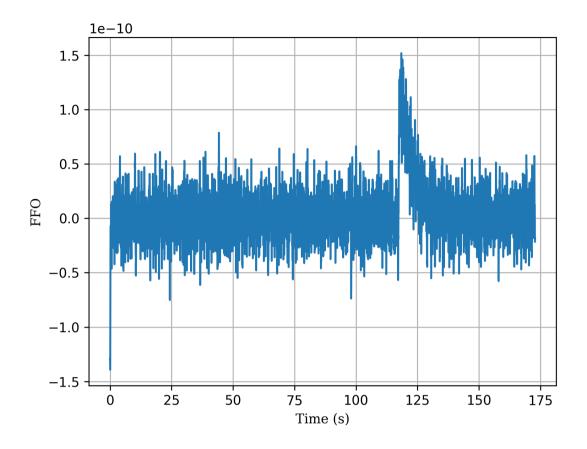

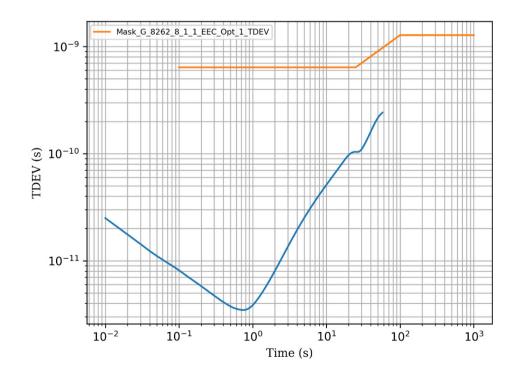

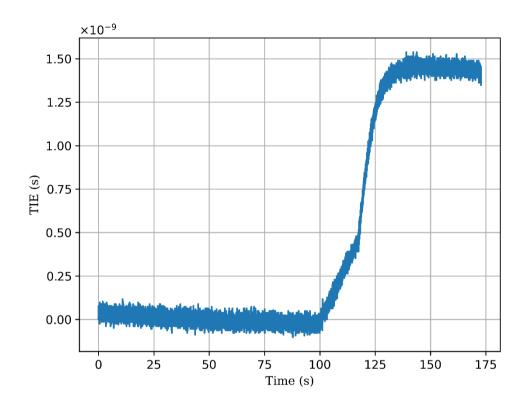

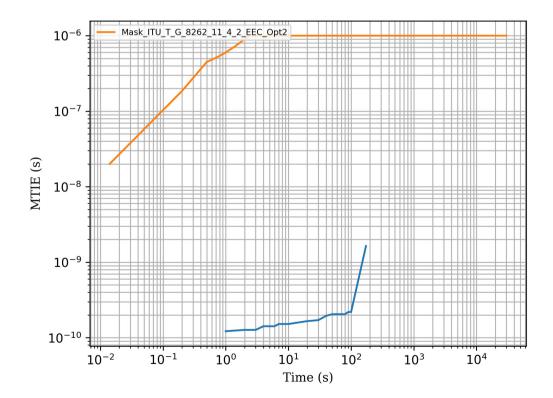

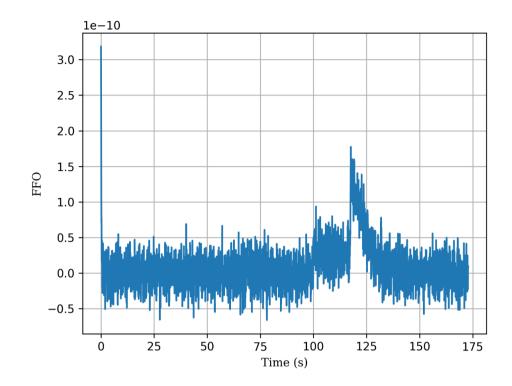

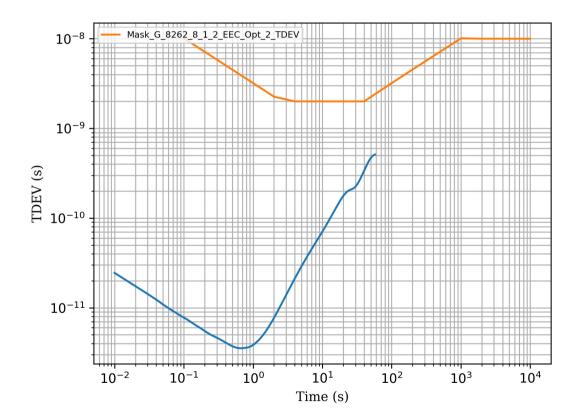

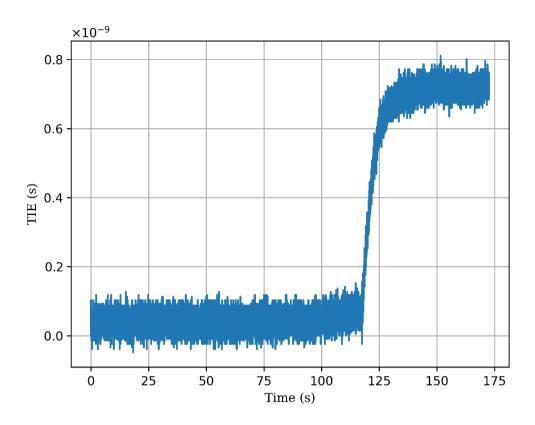

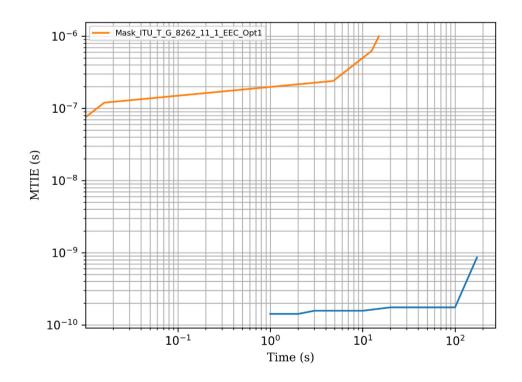

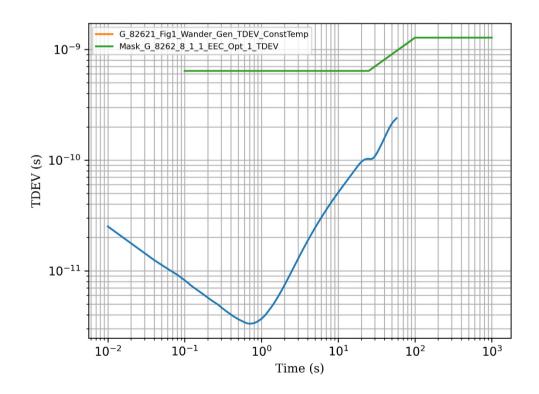

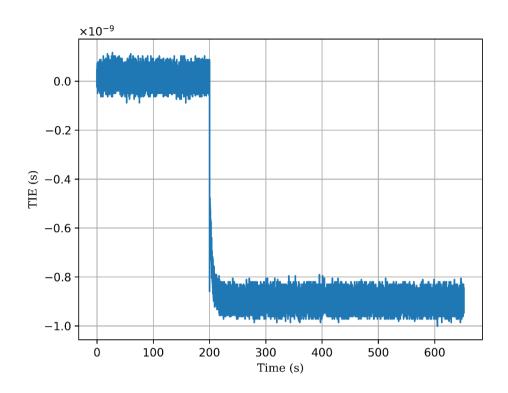

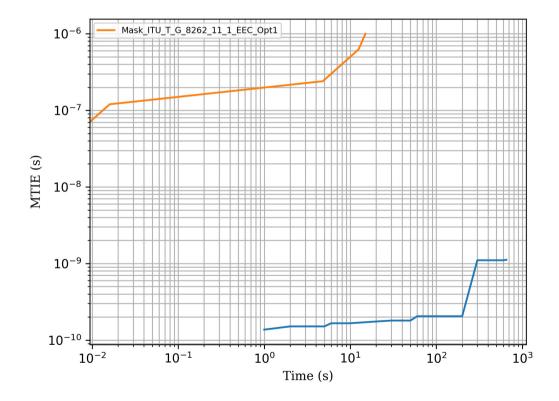

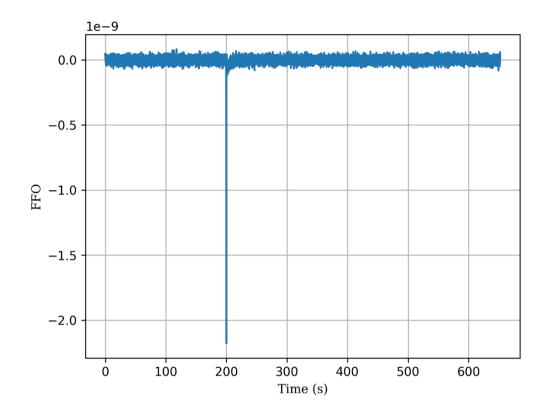

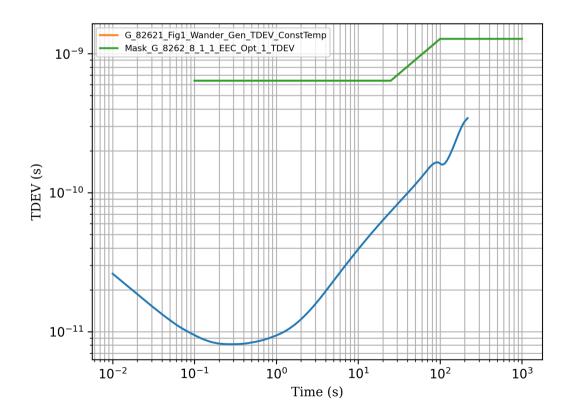

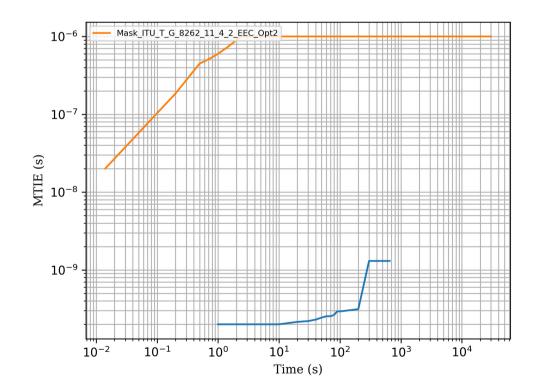

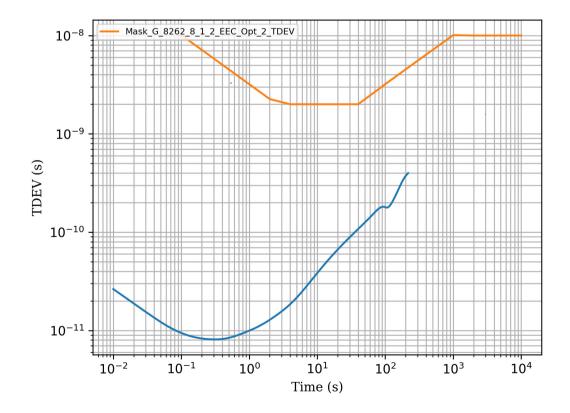

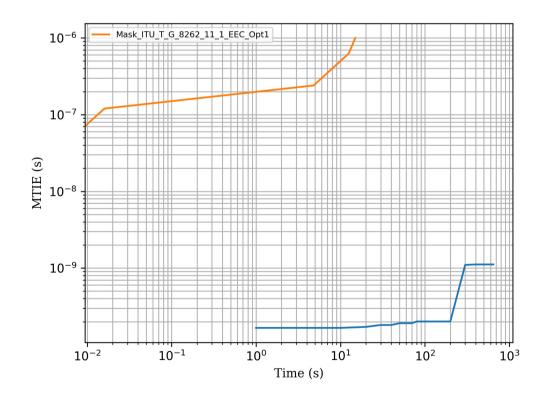

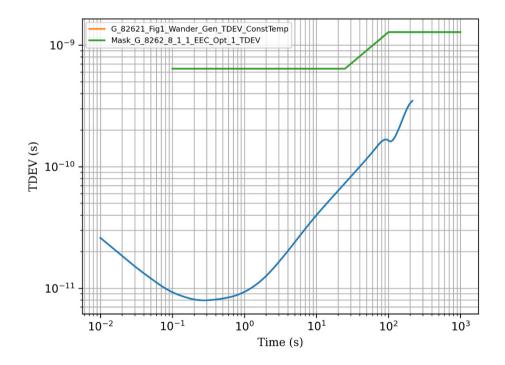

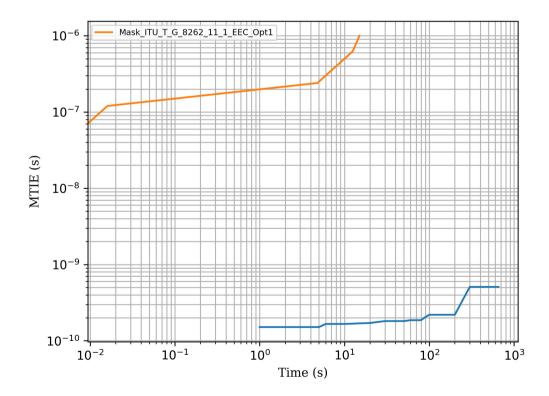

The wander generation requirement checks for the noise generated by the DUT, while the PLL is locked to an input clock signal that is wander free, it should not generate any wander that exceeds the MTIE mask as given by the standard being tested.

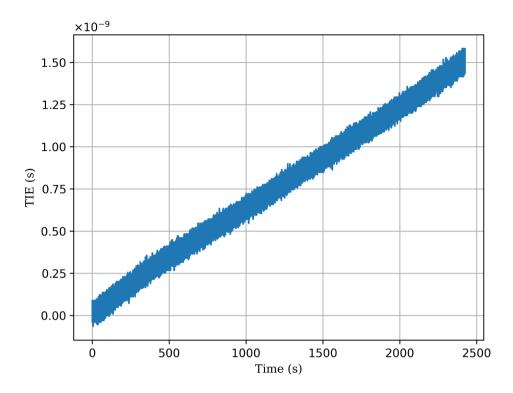

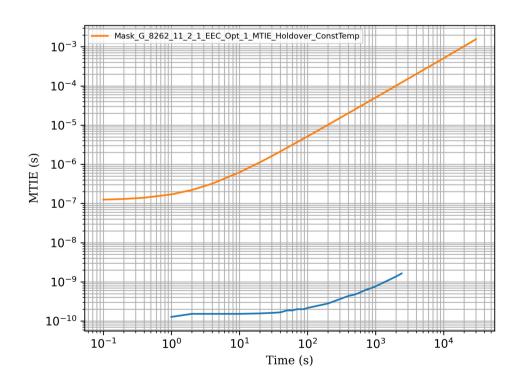

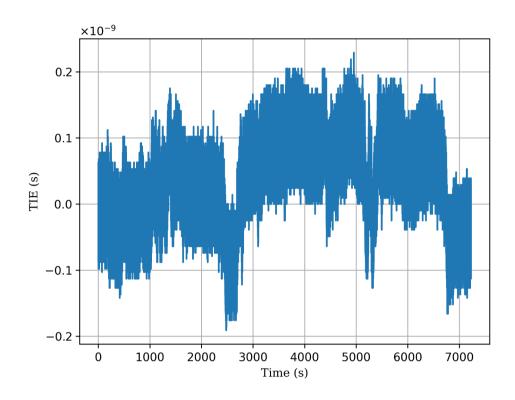

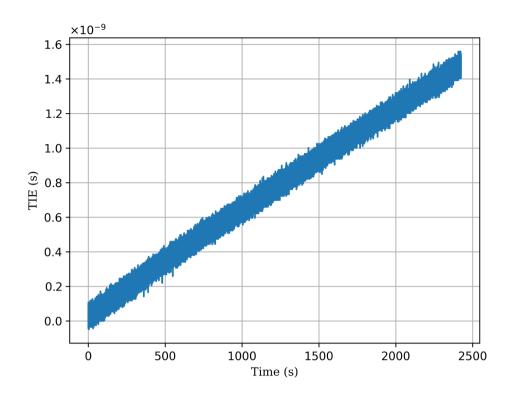

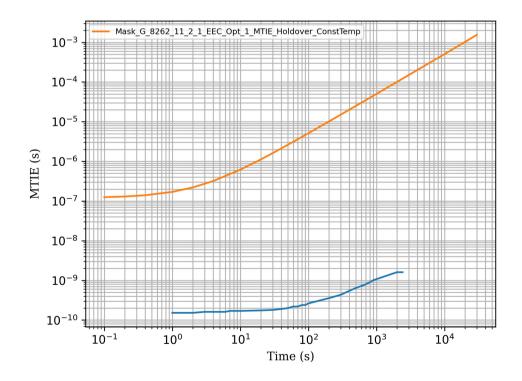

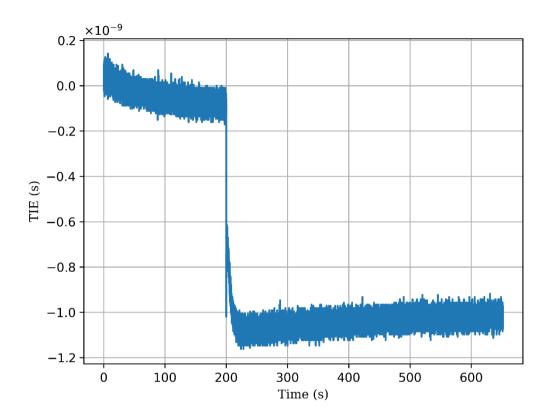

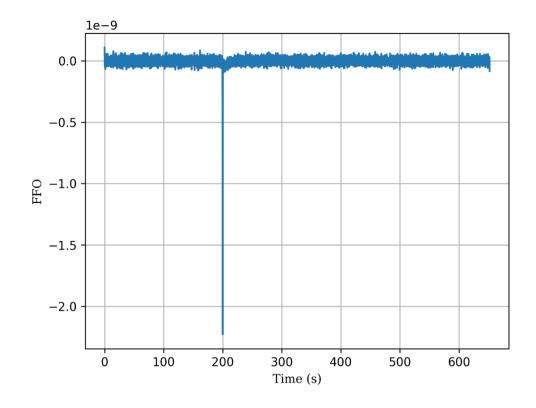

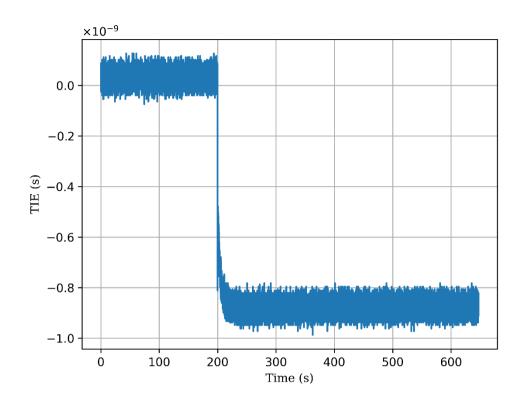

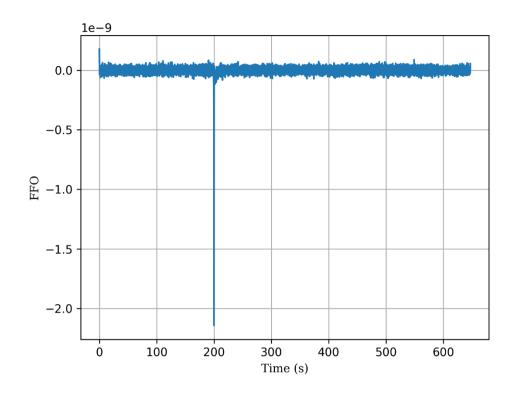

The wander generation and holdover test is carried out by providing a reference clock from the Agilent waveform generator on CLK0. The PLL should not produce/add any wander to the output beyond the standard allowed value. The test is run for 3 hours with a stable no wander input, and the output from OUT\_3 is monitored for phase error on the frequency counter. The generator connected to CLK0 is then turned OFF for a duration of time and the PLL goes into holdover state once the input is removed. The phase error between the output OUT\_3 and a second signal (reference signal from same source) is measured on the counter. The TIE and MTIE plots show the response of DUT in these conditions.

The holdover portion of this test is carried out with "Advanced Holdover".

Advanced holdover bandwidth is set to 1.5mHz.

Advanced holdover history is set to 30 seconds.

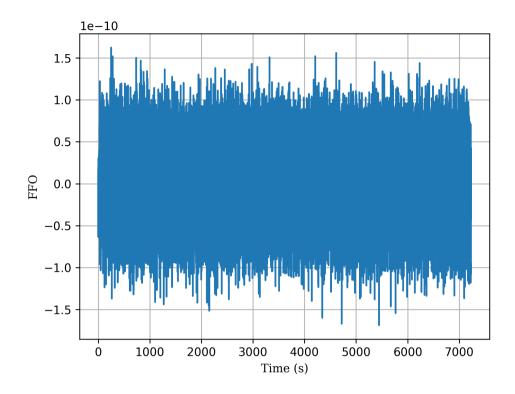

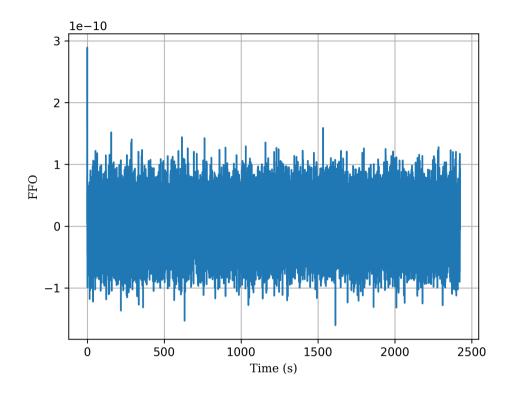

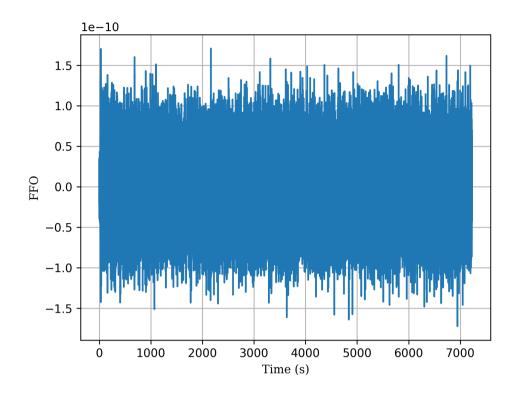

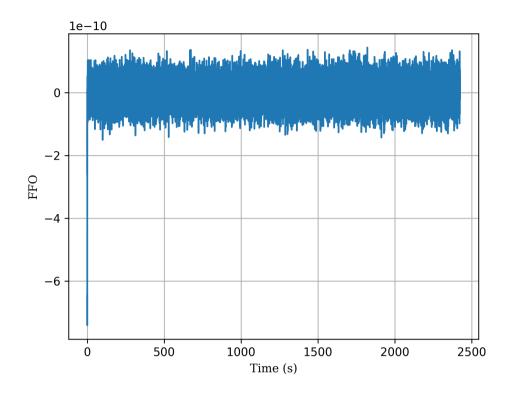

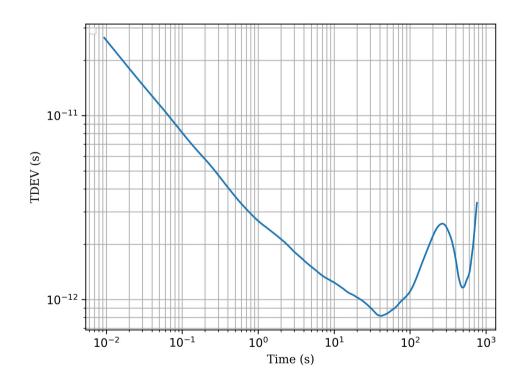

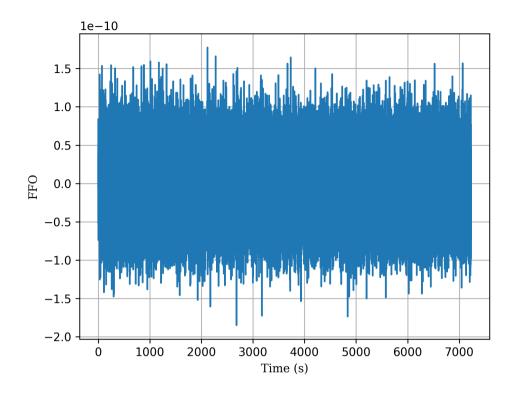

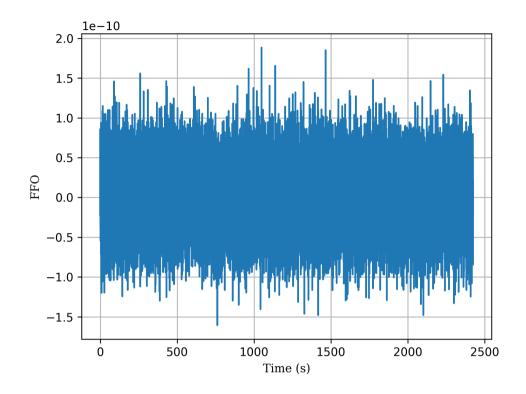

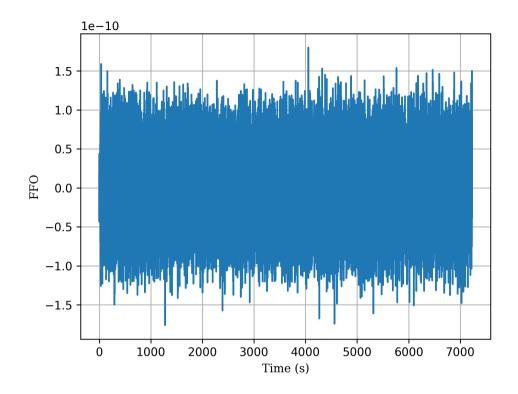

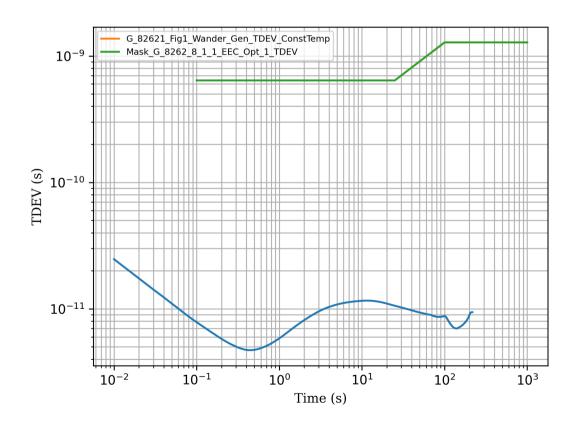

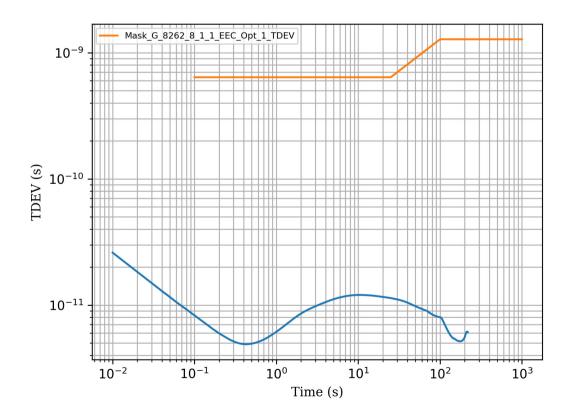

## 5.1 Wander in Locked Mode - G8262\_EEC1\_1Hz

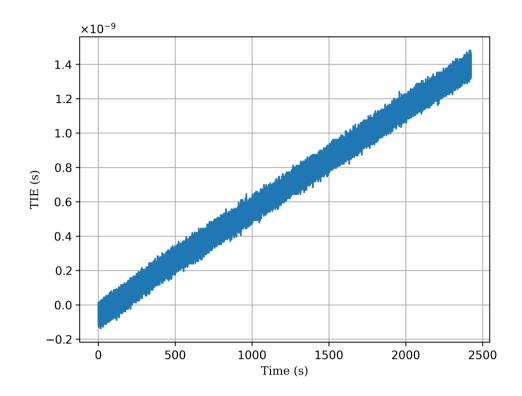

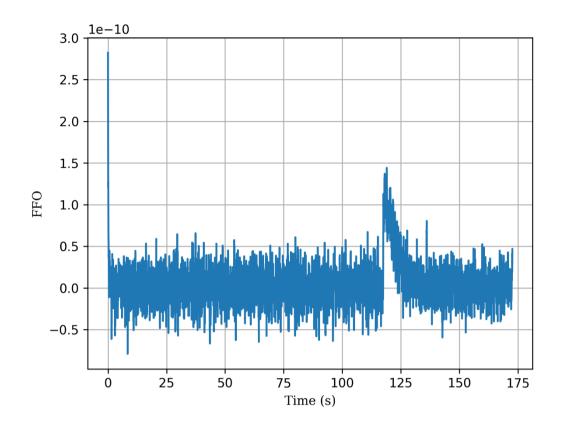

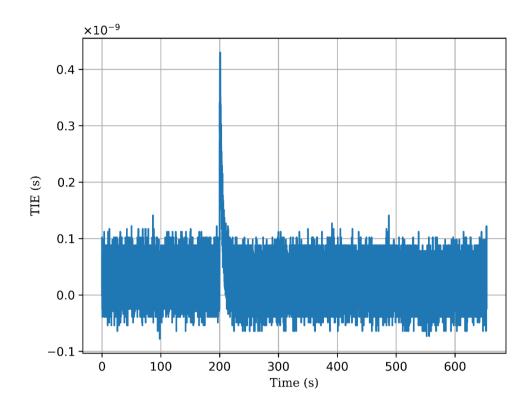

# 5.2 Long-term Phase Transient Response – G8262\_EEC1\_1Hz

FFO is 0.625 ppt (625 ppq)

# 5.3 Wander in Locked Mode – G8262\_EEC1\_10Hz

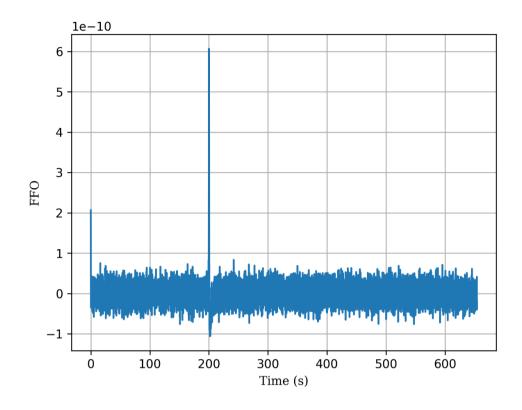

# 5.4 Long-term Phase Transient Response – G8262\_EEC1\_10Hz [1]

<sup>&</sup>lt;sup>1</sup> FFO is 0.583 ppt (583 ppq).

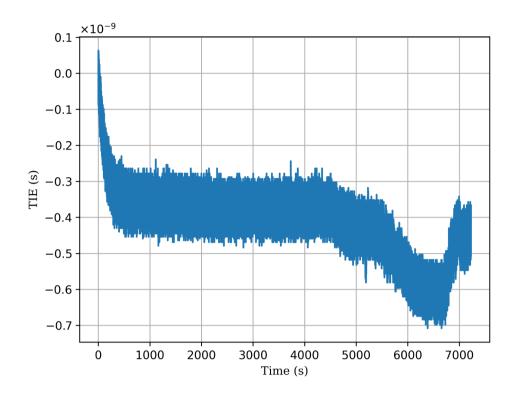

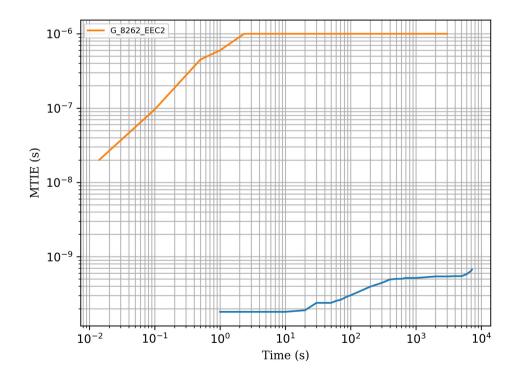

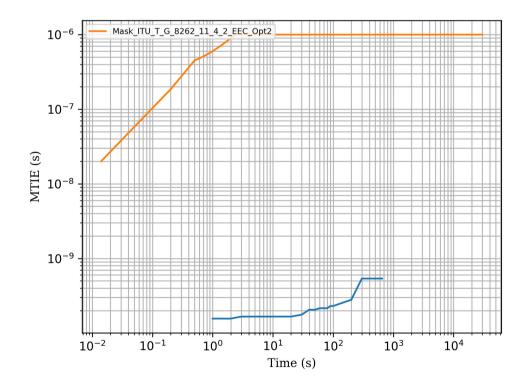

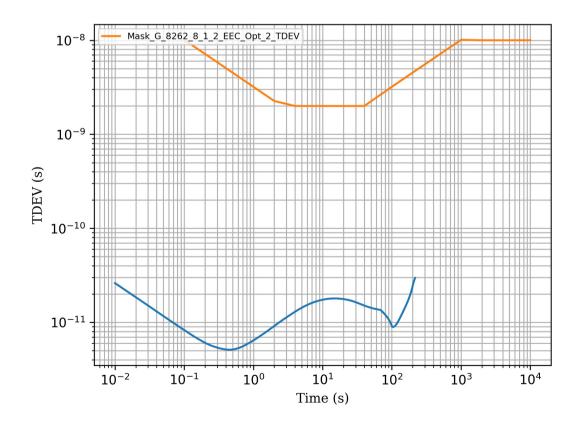

# 5.5 Wander in Locked Mode – G8262\_EEC2

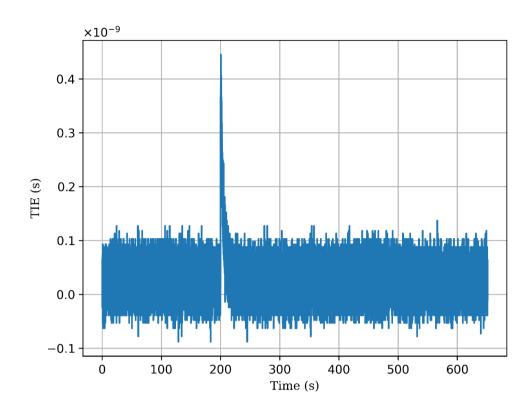

# 5.6 Long-term Phase Transient Response - G8262\_EEC2 [2]

<sup>&</sup>lt;sup>2</sup> FFO is 0.625 ppt (625 ppq).

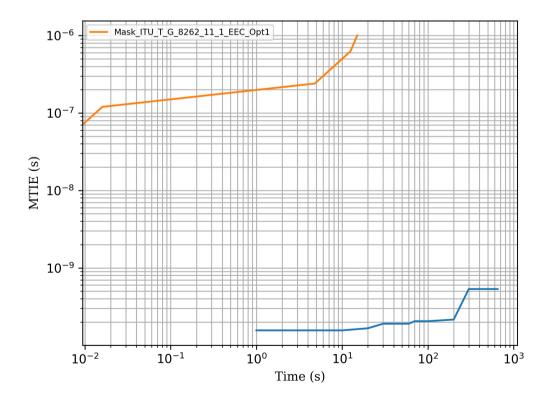

## 5.7 Wander in Locked Mode - G8262\_eEEC\_3Hz

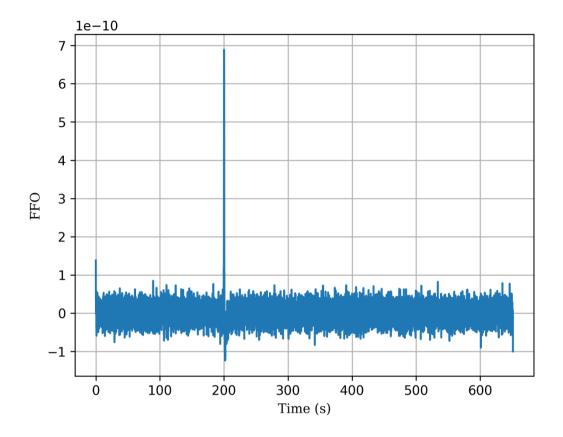

# 5.8 Long-term Phase Transient Response - G8262\_eEEC\_3Hz [3]

<sup>&</sup>lt;sup>3</sup> FFO is 0.625 ppt (625 ppq).

#### 6. Noise Tolerance

This is part of noise transfer testing. The RC32504A PLL is monitored so that it does not leave the LOCK state during noise transfer testing.

#### 7. Jitter Tolerance

The RC32504A PLL has a programmable lock threshold to tolerate large amounts of jitter at the input. To meet the jitter tolerance for EEC for any peak-peak jitter amplitude (UI), it is recommended to set the lock threshold to 250ns.

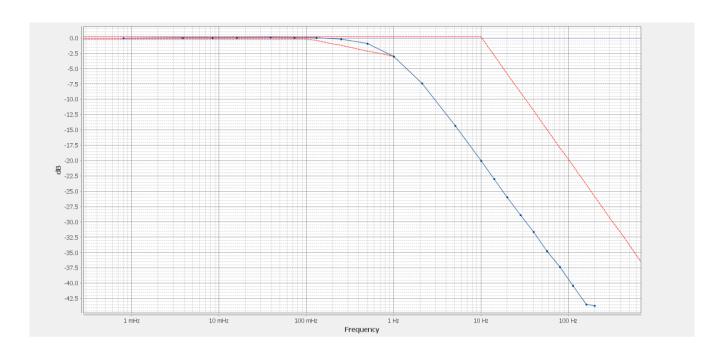

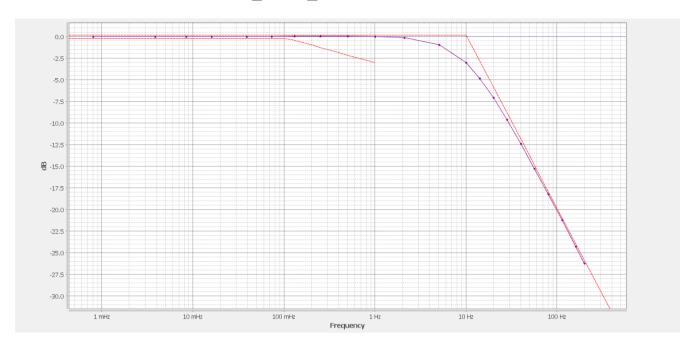

### 8. Noise (Wander) Transfer

Wander Transfer is a test that requires a PLL to receive a clock containing varying amounts of wander and suppressing that wander based on the damping factor of the PLL. Wander begins at Paragon-X, a device that can place sinusoidal wander at varying frequencies and amplitudes through an Ethernet port. A proprietary PHY recovers the clock on this Ethernet line and sends the signal to an external Renesas RC32504A PLL. The RC32504A PLL acts as a transparent device to pass the wander to the DUT at the frequency specified by the standard. The DUT then cleans up the signal and returns it through the RC32504A PLL and the proprietary PHY where it is measured by Paragon-Xto determine the phase gain present in the signal.

*Note*: Paragon-X does not natively create a Gain (dB) vs. Frequency (Hz) graph when running wander transfer with a table of sinusoidal frequencies. The graphs in this report requiring that type of test are created by parsing the data that Paragon-X calculates during the test and plotting it. Results for the TDEV style of wander transfer used for ITU-T G.8262 EEC Option 2, however, are generated and plotted by Paragon-X

## 8.1 Noise Transfer - G8262\_EEC1\_1Hz

Table 2. Wander Transfer Gain Peaking for Standard - G8262\_EEC1\_1 Hz

| Frequency (Hz) | Noise Amplitude (nsec) | Gain Peaking(dB) |

|----------------|------------------------|------------------|

| 0.00384        | 2000.0                 | 0.01             |

| 0.0084         | 2000.0                 | 0.04             |

| 0.016          | 2000.0                 | 0.07             |

| 0.0388         | 825.0                  | 0.09             |

| 0.073          | 438.0                  | 0.08             |

| 0.13           | 250.0                  | 0.03             |

| 0.25           | 250.0                  | -0.16            |

| 0.5            | 250.0                  | -0.89            |

| 1.0            | 250.0                  | -2.98            |

| 2.104          | 250.0                  | -7.36            |

| 5.065          | 250.0                  | -14.29           |

| 10.0           | 250.0                  | -20.03           |

| 14.14          | 250.0                  | -22.98           |

| 20.0           | 250.0                  | -25.95           |

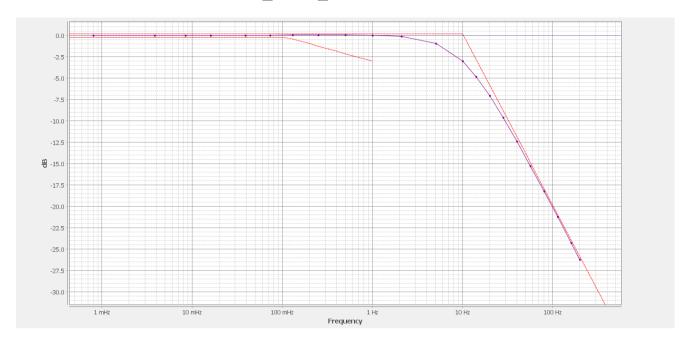

# 8.2 Noise Transfer - G8262\_EEC1\_10Hz

Table 3. Wander Transfer Gain Peaking for Standard - G8262\_EEC1\_10Hz

| Frequency (Hz) | Noise Amplitude (nsec) | Gain Peaking(dB) |

|----------------|------------------------|------------------|

| 0.00384        | 2000.0                 | 0                |

| 0.0084         | 2000.0                 | 0                |

| 0.016          | 2000.0                 | 0                |

| 0.0388         | 825.0                  | 0.01             |

| 0.073          | 438.0                  | 0.03             |

| 0.13           | 250.0                  | 0.06             |

| 0.25           | 250.0                  | 0.07             |

| 0.5            | 250.0                  | 0.07             |

| 1.0            | 250.0                  | 0.04             |

| 2.104          | 250.0                  | -0.11            |

| 5.065          | 250.0                  | -0.94            |

| 10.0           | 250.0                  | -3               |

| 14.14          | 250.0                  | -4.78            |

| 20.0           | 250.0                  | -7.02            |

| 28.284         | 250.0                  | -9.59            |

| 40.0           | 250.0                  | -12.35           |

| 56.569         | 250.0                  | -15.25           |

## 8.3 Noise Transfer - G8262\_EEC1\_10Hz

Table 4. Wander Transfer Gain Peaking for Standard - G8262\_EEC1\_10 Hz

| Frequency (Hz) | Noise Amplitude (nsec) | Gain Peaking(dB) |

|----------------|------------------------|------------------|

| 0.00384        | 2000.0                 | 0.15             |

| 0.0084         | 2000.0                 | 0.17             |

| 0.016          | 2000.0                 | 0.09             |

| 0.0388         | 825.0                  | -0.51            |

| 0.073          | 438.0                  | -1.87            |

| 0.13           | 250.0                  | -4.62            |

| 0.25           | 250.0                  | -9.11            |

| 0.5            | 250.0                  | -14.7            |

| 1.0            | 250.0                  | -20.64           |

| 2.104          | 250.0                  | -26.98           |

| 5.065          | 250.0                  | -34.4            |

| 10.0           | 250.0                  | -40.35           |

| 14.14          | 250.0                  | -43.65           |

| 20.0           | 250.0                  | -46.37           |

| 28.284         | 250.0                  | -49.83           |

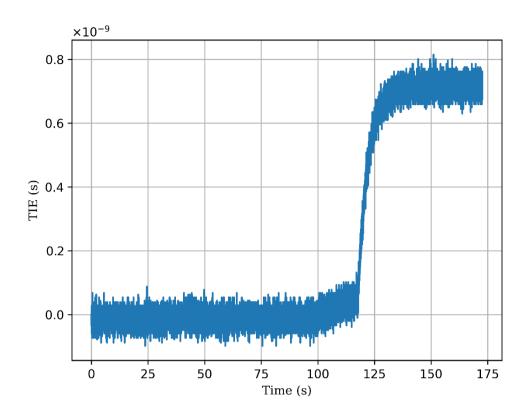

### 9. (Phase) Transient Response – Short-term

Short-term phase transient response requirement reflects the performance of the DUT in cases when the (selected) input reference is lost due to a failure in the reference path and a second reference input signal, traceable to the same reference clock, is available simultaneously, or shortly after the detection of the failure.

The test was carried out by providing reference clock inputs on CLK0 and CLK1 from the Agilent waveform generator, which are 180° out of phase from each other. The PLL is locked to the clock signal from CLK0 for a given period of time before producing a phase transient by turning off the input reference signal for 11 seconds, during this time the clock on CLK1 is unavailable. The DPLL goes into holdover during the 11 second period because no other reference is available. After 11 seconds the reference signal on IN\_B is turned ON and PLL locks to the newly available reference signal. The switching during the two transients Locked (CLK0)  $\rightarrow$  holdover  $\rightarrow$  Locked (CLK1) is carried out. The output from the DUT is available on the OUT\_3 and the phase time error is captured using the frequency counter. The results of the given transient are plotted against the mentioned standard profiles.

For reference clocks, < 1MHz it is recommended to enable Hitless switching to absorb phase offset.

# 9.1 Short-term Phase Transient - G8262\_EEC1\_1Hz

# 9.2 Short-term Phase Transient - G8262\_EEC1\_10Hz

# 9.3 Short-term Phase Transient - G8262\_EEC2

# 9.4 Short-term Phase Transient - G8262\_eEEC1\_3Hz

### 10. (Phase) Transient Response - Input Signal Interruption

Transient response compliance checks the system response in situations where the input signal is affected by disturbances or transmission failures, which would result in phase transients at the synchronous EEC (Ethernet Equipment Clock) output. Short interruptions, switching between different reference clock signals, loss of reference etc., are categorized as transients, which would result in phase transients at the EEC output.

In this test the reference clock inputs are provided on CLK0 and CLK1 from the Agilent waveform generator, the PLL is locked to the clock signal from CLK0 for a given period of time before producing a phase transient by turning off the clock signal. The DPLL goes into holdover and tries to lock to any other qualified clocks. CLK1 is available from the Agilent waveform generator, and the DPLL switches to this clock which is very close in phase alignment to the original clock. The results of the given transient are plotted against the mentioned standard profiles.

Hitless switching is disabled during this test.

# 10.1 Phase Response to Input Signal Interruptions - G8262\_EEC1\_1Hz

### 10.2 Phase Response to Input Signal Interruptions - G8262\_EEC1\_10Hz

### 10.3 Phase Response to Input Signal Interruptions - G8262\_EEC2

### 10.4 Phase Response to Input Signal Interruptions - G8262\_eEEC1\_3Hz

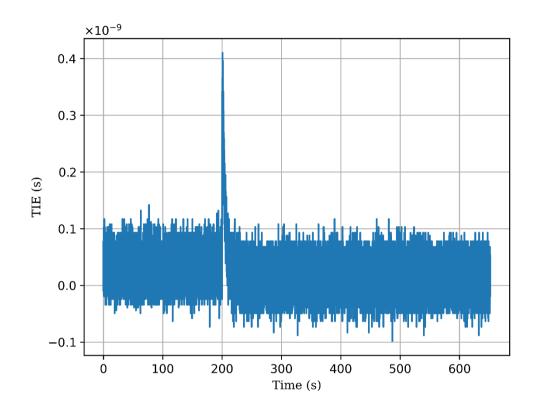

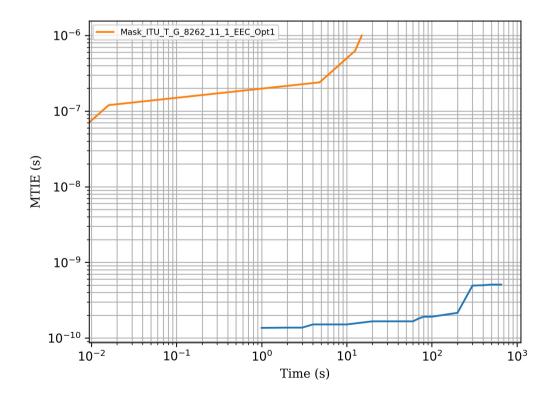

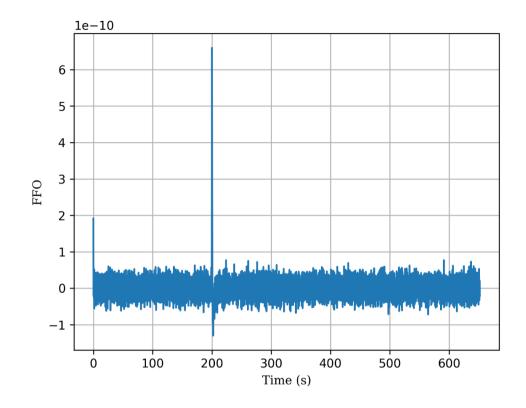

## 11. (Phase) Transient Response - Phase Discontinuity

Phase discontinuity requirement reflects the performance of the DUT in cases when there are internal disturbances within the equipment clock.

The test was carried out by providing reference clock inputs on CLK0 and CLK1 from the Agilent waveform generator which are 180° out of phase from each other. The PLL is locked to the clock signal from CLK0 for a given period of time before producing a phase transient by turning off the signal to CLK0 from the waveform generator while the signal at CLK1 is simultaneously available to the DUT. The DPLL will try to lock to the reference signal on CLK1. The output from the DUT is made available on the OUT\_3 output and the phase time error is captured using the frequency counter. The results of the given transient are plotted against the mentioned standard profiles.

Hitless switching is enabled during this test.

### 11.1 Phase Discontinuity - G8262\_EEC1\_1Hz

### 11.2 Phase Discontinuity - G8262\_EEC1\_10Hz

# 11.3 Phase Discontinuity - G8262\_EEC2

### 11.4 Phase Discontinuity - G8262\_eEEC1\_3Hz

#### 12. Interfaces

The RC32504A PLL can lock to virtually any frequency from 1MHz to 1GHz and produce virtually any output frequency from 1MHz to 1GHz, supporting a wide range of synchronization input and output interfaces.

### 13. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.0      | Mar 22, 2021 | Initial release. |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.