## ISL70020SEH, ISL73020SEH

**Total Dose Test Report**

### Introduction

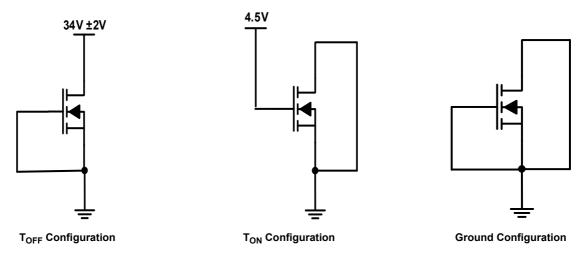

This report documents the results of Low Dose Rate (LDR) and High Dose Rate (HDR) total dose testing and subsequent high temperature biased annealing of the <u>ISL70020SEH</u> and <u>ISL73020SEH</u> 40V, 65A N-Channel enhancement mode GaN transistors. The tests were conducted to provide an assessment of the total dose hardness of the part and to provide an estimate of dose rate, bias, or anneal sensitivity. Parts were irradiated under three different bias conditions:

- T<sub>OFF</sub> gate and source grounded; drain connected to 34V ±2V

- T<sub>ON</sub> gate connected to 4.5V ±10%; drain and source connected to ground

- · With all pins grounded at LDR and at HDR (See Figure 1).

The ISL70020SEH is rated at 100krad(Si) at HDR (50 – 300rad(Si)/s) and at 75krad(Si) at LDR (0.01rad(Si)/s). The ISL73020SEH is rated at 75krad(Si) at LDR (0.01rad(Si)/s). Both part types are acceptance tested on a lot-by-lot basis to these limits.

### Related Literature

For a full list of related documents, visit our website:

- ISL70020SEH, ISL73020SEH device pages

- MIL-STD-883 Test Method 1019

### 3. Part Description

The ISL7x020SEH is a 40V N-channel enhancement mode GaN power transistor. Applications for these devices include commercial aerospace, medical, and nuclear power generation. The exceptionally high electron mobility and low temperature coefficient of the GaN allows for very low  $r_{DS(ON)}$  of  $3.5m\Omega$ , (typical), while its lateral device structure and majority carrier diode provide exceptionally low  $Q_G$  and zero  $Q_{RR}$ . This results in a device that can operate at a higher switching frequency with more efficiency while reducing the overall solution size.

The ISL7x020SEH operates across the -55°C to +125°C temperature range and is offered in a hermetically sealed Surface Mount Device (SMD) 4-pin package. Manufacturing in a MIL-PRF-38535 like flow results in best-in-class power transistors that are ideally suited for high reliability applications.

The pin numbers and descriptions for the ISL7x020SEH are shown in <u>Table 1</u>.

Table 1. ISL7x020SEH Pin Number and Descriptions

| Pin Number | Pin Name | Description                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------------|

| 1          | S        | Source connection for GaN FET.                                                                            |

| 2          | SUB      | Substrate connection for GaN FET which is internally shorted in to source. Tie this pin to source on PCB. |

| 3          | D        | Drain connection for GaN FET.                                                                             |

| 4          | G        | Gate connection for GaN FET. Minimize trace inductance from driver to reduce over-stressing the gate.     |

| NA         | Lid      | Internally tied to the source pin.                                                                        |

## 1. Test Description

### 1.1 Irradiation Facilities

HDR testing was performed at 167.5rad(Si)/s using a Gammacell 220 irradiator located in the Palm Bay, Florida Renesas facility. LDR testing was performed at 0.01rad(Si)/s using the Renesas Palm Bay Hopewell Designs N40 panoramic irradiator. Both irradiators use PbAl spectrum hardening filters to shield the test board and devices under test against low energy secondary gamma radiation. Biased irradiation and annealing were performed on all samples following irradiation, at 100°C for 168 hours in a small temperature chamber.

### 1.2 Test Fixturing

Figure 1 shows the configurations used for biased irradiation at both dose rates.

Figure 1. ISL7x020SEH TID Bias Schematics

## 1.3 Characterization Equipment and Procedures

All electrical testing was performed at room temperature outside the irradiator, using production Automated Test Equipment (ATE) with datalogging at each downpoint.

### 1.4 Experimental Matrix

Irradiation was performed in accordance with the guidelines of MIL-STD-883 Test Method 1019. The experimental matrix consisted of 24 samples irradiated at LDR under  $T_{OFF}$  bias, 24 samples irradiated at LDR under  $T_{OFF}$  bias, 24 samples irradiated at LDR under  $T_{OFF}$  bias, 24 samples irradiated at HDR under  $T_{OFF}$  bias, 24 samples irradiated at HDR under  $T_{ON}$  bias, and 24 samples irradiated at HDR with all pins grounded. At anneal, the parts irradiated with all leads grounded were split, with half of units biased in the  $T_{OFF}$  configuration and the other half biased in the  $T_{ON}$  configuration. Five control units were used.

The ISL7x020SEH samples were drawn equally from three wafer lots: RR9KB188, RR9KB349, and RRF1T164. All samples were packaged in the hermetic 42mm<sup>2</sup> 4-pin surface mount package (PKG code J4.A). Samples were processed through the standard burn-in cycle before irradiation.

### 1.5 Downpoints

Downpoints for the LDR tests were 0, 30, 50, 75, and 100krad(Si). Downpoints for the HDR tests were 0, 30, 50, 100 and 150krad(Si). All irradiations were followed by a 168 hour high temperature anneal at 100°C under bias, as described in <a href="Experimental Matrix">Experimental Matrix</a>.

# 2. Test Results

## 2.1 Attributes Data

Total dose testing of the ISL7x020SEH is complete. <u>Table 2</u> summarizes the results.

Table 2. ISL7x020SEH Total Dose Test Attributes Data

| Dose Rate (rad(Si)/s) | Bias                                      | Sample Size | Downpoint       | Pass ( <u>Note 1</u> ) | Fail |

|-----------------------|-------------------------------------------|-------------|-----------------|------------------------|------|

| 0.01                  | T <sub>OFF</sub>                          | 20          | Pre-irradiation | 24                     | 0    |

|                       | (T <sub>OFF</sub> Configuration)          |             | 30krad(Si)      | 24                     | 0    |

|                       |                                           |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 75krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

| 0.01                  | T <sub>ON</sub>                           | 20          | Pre-irradiation | 24                     |      |

|                       | (T <sub>ON</sub> Configuration)           |             | 30krad(Si)      | 24                     | 0    |

|                       |                                           |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 75krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

| 0.01                  | GND                                       | 20          | Pre-irradiation | 24                     |      |

|                       | ( <u>Ground</u><br><u>Configuration</u> ) |             | 30krad(Si)      | 24                     | 0    |

|                       | <u>oomigaration</u> )                     |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 75krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

| 167.5                 | T <sub>OFF</sub>                          | 16          | Pre-irradiation | 24                     |      |

|                       | (T <sub>OFF</sub> Configuration))         |             | 30krad(Si)      | 24                     | 0    |

|                       |                                           |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | 150krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

| 167.5                 | T <sub>ON</sub>                           | 16          | Pre-irradiation | 24                     |      |

|                       | (T <sub>ON</sub> Configuration)           |             | 30krad(Si)      | 24                     | 0    |

|                       |                                           |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | 150krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

| 167.5                 | GND                                       | 16          | Pre-irradiation | 24                     |      |

|                       | ( <u>Ground</u><br><u>Configuration</u> ) |             | 30krad(Si)      | 24                     | 0    |

|                       | <u>comgaration</u> )                      |             | 50krad(Si)      | 24                     | 0    |

|                       |                                           |             | 100krad(Si)     | 24                     | 0    |

|                       |                                           |             | 150krad(Si)     | 24                     | 0    |

|                       |                                           |             | Anneal          | 24                     | 0    |

Note:

<sup>1.</sup> Pass indicates a sample that passes all datasheet limits.

## 2.2 Key Parameter Listing

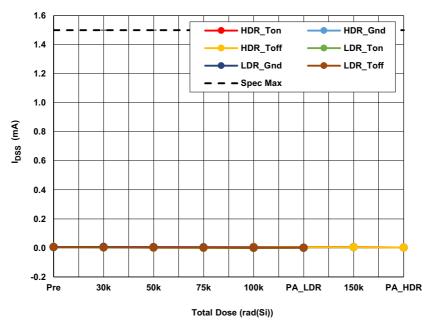

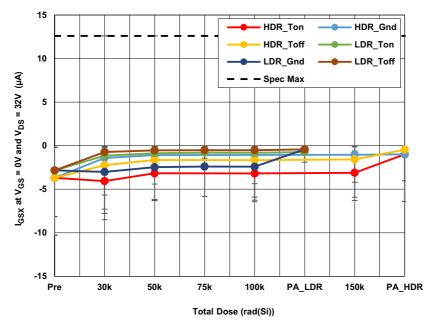

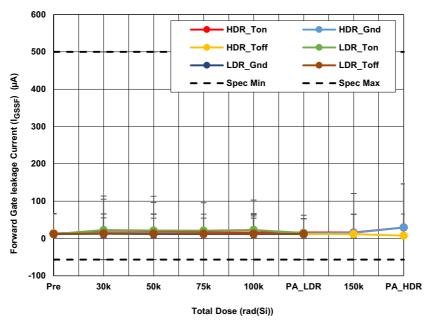

<u>Table 3</u> lists 12 key parameters that are considered indicative of part performance. These parameters are plotted in <u>Figure 2</u> through <u>Figure 12</u>. All limits are taken from the <u>ISL7x020SEH</u> datasheet.

Table 3. ISL7x020SEH Key Total Dose Datasheet Parameters ( $T_A = 25$ °C)

| Figure    | Parameter                       | Symbol              | Limit<br>(Low) | Limit<br>(High) | Unit | Conditions                                                        |

|-----------|---------------------------------|---------------------|----------------|-----------------|------|-------------------------------------------------------------------|

| <u>2</u>  | Drain-to-Source Leakage Current | I <sub>DSS</sub>    | -              | 1.5             | mA   | V <sub>DS</sub> = 32V, V <sub>GS</sub> = 0V                       |

| <u>3</u>  | Drain-to-Gate Leakage Current   | I <sub>GSX</sub>    | -              | 12.6            | μΑ   | V <sub>DS</sub> = 32V, V <sub>GS</sub> = 0V                       |

| <u>4</u>  | Gate-to-Source Forward Leakage  | I <sub>GSSF</sub>   | -              | 500             | μΑ   | V <sub>GS</sub> = 5V                                              |

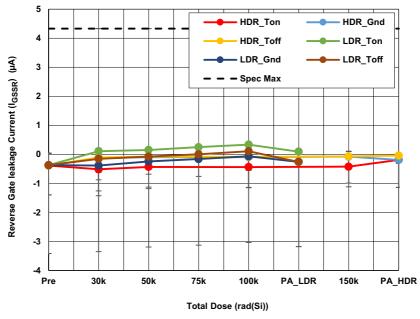

| <u>5</u>  | Gate-to-Source Reverse Leakage  | I <sub>GSSR</sub>   | -              | 4.33            | μΑ   | V <sub>GS</sub> = -4V                                             |

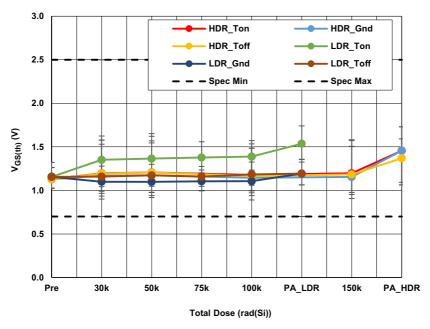

| <u>6</u>  | Gate Threshold Voltage          | V <sub>GS(th)</sub> | 0.7            | 2.5             | V    | $V_{DS} = V_{GS}$ , $I_D = 12mA$                                  |

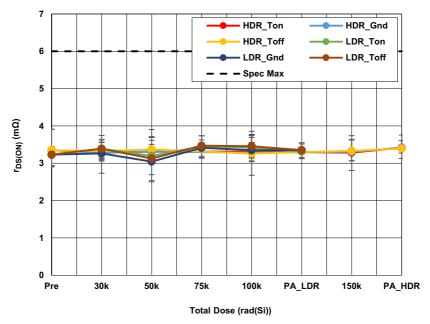

| <u>7</u>  | Drain-to-Source On-Resistance   | r <sub>DS(ON)</sub> | -              | 6               | mΩ   | V <sub>GS</sub> = 5V, I <sub>D</sub> = 35A                        |

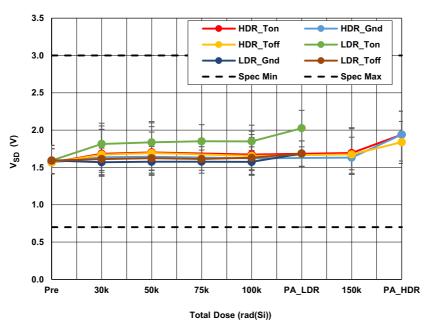

| <u>8</u>  | Source-to-Drain Forward Voltage | $V_{SD}$            | 0.7            | 3.0             | V    | $I_S = 0.5A, V_{GS} = 0V$                                         |

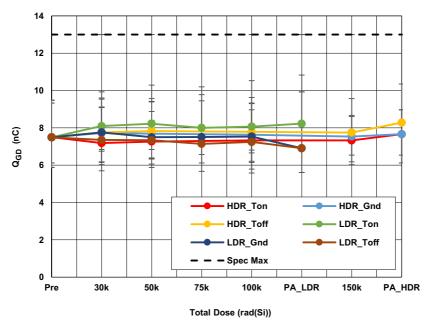

| 9         | Gate-to-Drain Charge            | $Q_{GD}$            | -              | 13              | nC   | V <sub>DS</sub> = 20V, I <sub>D</sub> = 35A                       |

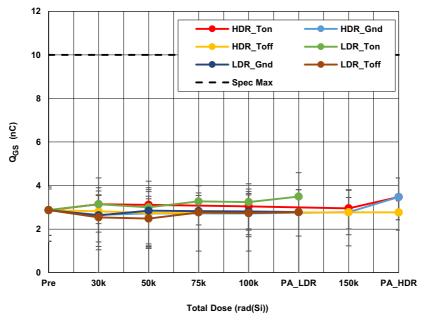

| <u>10</u> | Gate-to-Source Charge           | Q <sub>GS</sub>     | -              | 10              | nC   | V <sub>DS</sub> = 20V, I <sub>D</sub> = 35A                       |

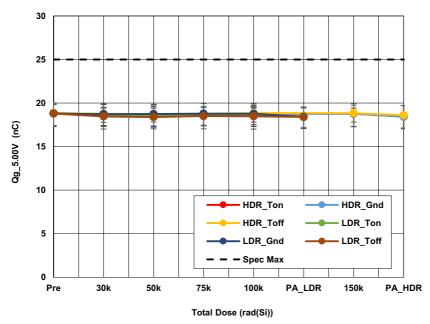

| <u>11</u> | Total Gate Charge               | $Q_{G}$             | -              | 25              | nC   | V <sub>DS</sub> = 20V, I <sub>D</sub> = 35A, V <sub>GS</sub> = 5V |

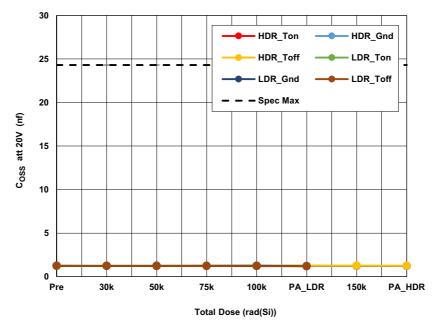

| <u>12</u> | Output Capacitance              | C <sub>OSS</sub>    | -              | 24.3            | nF   | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 0V                       |

## 2.3 Key Parameter Variables Data

The plots in <u>Figure 2</u> through <u>Figure 12</u> show the TID response of the key datasheet parameters outlined in <u>Key Parameter Listing</u>. The plots show the average tested values of the key parameters shown in <u>Table 3</u> as a function of total dose for each of the three irradiation conditions, T<sub>OFF</sub>, T<sub>ON</sub>, and GND at HDR and LDR. For example, the legend LDR\_TOFF indicates the average LDR response for parts biased in the TOFF configuration. PA\_LDR on the graphs stands for Post-Anneal Low Dose and PA\_HDR represents the Post-Anneal High Dose results. As described in <u>"Experimental Matrix" on page 2</u>, the worst case value of the two anneal bias configurations of the samples that were irradiated with all terminals grounded is plotted. The plots also include error bars at each downpoint, representing the minimum and maximum measured values of the samples, although in some plots the error bars are not visible due to their values compared to the scale of the graph.

Figure 2. ISL7x020SEH drain-to-source leakage current,  $I_{DSS}$ , with  $V_{DS}$  = 32V and  $V_{GS}$  = 0V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit, which is set by temperature, is 1.5mA maximum.

Figure 3. ISL7x020SEH drain-to-gate leakage current,  $I_{GSX}$ , with  $V_{DS}$  = 32V and  $V_{GS}$  = 0V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit, which is set by temperature, is 12.6 $\mu$ A maximum.

Figure 4. ISL7x020SEH gate-to-source forward leakage current,  $I_{GSSF}$  with  $V_{GS}$  = 5V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit, which is set by temperature, is 500 $\mu$ A maximum.

Figure 5. ISL7x020SEH gate-to-source reverse leakage current,  $I_{GSSR}$ , with  $V_{GS}$  = -4V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit, which is set by temperature, is 4.33µA minimum.

Figure 6. ISL7x020SEH gate threshold voltage,  $V_{GS(th)}$ , with  $V_{DS} = V_{GS}$ ,  $I_{DS} = 12mA$ , as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limits are 0.7V minimum and 2.5V maximum.

Figure 7. ISL7x020SEH drain-to-source on-resistance,  $r_{DS(ON)}$ , with  $V_{GS}$  = 5V,  $I_D$  = 35A, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit is  $6m\Omega$  maximum.

Figure 8. ISL7x020SEH source-to-drain forward voltage,  $V_{SD}$ , with  $I_{S}$  = 0.5A,  $V_{GS}$  = 0V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limits are 0.7V minimum and 3.0V maximum.

Figure 9. ISL7x020SEH gate-to-drain charge,  $Q_{GD}$ , with  $V_{DS}$  = 20V,  $I_D$  = 35A, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit is 13nC maximum.

Figure 10. ISL7x020SEH gate-to-source charge,  $Q_{GS}$ , with  $V_{DS}$  = 20V,  $I_D$  = 35A, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit is 10nC maximum.

Figure 11. ISL7x020SEH total gate charge,  $Q_G$  with  $V_{DS}$  = 20V,  $I_D$  = 35A, VGS = 5V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit is 25nC maximum.

Figure 12. ISL7x020SEH output capacitance,  $C_{OSS}$ , with  $V_{DS}$  = 20V,  $V_{GS}$  = 0V, as a function of total dose irradiation at LDR and at HDR for all three bias cases. The datasheet limit is 24.3nF maximum.

## 3. Discussion and Conclusion

We reported the results of a LDR and HDR total dose test of the ISL7x020SEH 40V, 65A N-Channel enhancement mode GaN transistor. All irradiations were followed by a 168-hour anneal at 100°C under bias. "Attributes Data" on page 3 summarizes the attributes data for the test. "Key Parameter Listing" on page 4 summarizes the critical parameters for the part. Finally, "Key Parameter Variables Data" on page 4 provides plots of the total dose and anneal response for the critical parameters.

All parameters remained well within the datasheet limits at all downpoints and only showed slight differences in total dose response between LDR and HDR irradiations and bias conditions. The only parameters that bear mentioning are the slightly different responses for the LDR\_Ton samples for the  $V_{GS(TH)}$  and  $V_{SD}$  measurements, as can be seen in Figure 6 and Figure 8, respectively, but they were only about 200mV different than the HDR Ton response at 100krad(Si), and still well within specifications.

# 4. Revision History

| Rev. | Date      | Description     |  |  |

|------|-----------|-----------------|--|--|

| 1.00 | Oct.29.19 | Initial release |  |  |

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/