# intersil

### ISL70003SEH

Single Event Effects Testing

# Introduction

The intense heavy ion environment encountered in space applications can cause a variety of destructive and non destructive effects in analog circuits, including single event latch-up (SEL), single event gate rupture (SEGR), single event burnout (SEB), single event transients (SET) and single event functional interrupt (SEFI). These effects can lead to system-level failures including disruption and/or permanent damage. For predictable and reliable system operation, these components have to be formally designed and fabricated for SEE hardness, followed by detailed SEE testing to validate the design. This report discusses the results of SEE testing of Intersil's ISL70003SEH, a wide input voltage range (3V to 13.2V) 6A synchronous buck regulator.

# **Related Documents**

- ISL70003SEH Datasheet

- ISL70003SEH Radiation Report

- <u>AN1897</u> Radiation Hardened and SEE Hardened 3V to 12V, 6A Synchronous Buck Regulator Evaluation Board User's Guide

- AN1915 ISL70003SEH iSim: PE Mode

- <u>AN1924</u> Total Dose Testing of the ISL70003SEH Radiation Hardened Point Of Load Regulator

# **Product Description**

The ISL70003SEH is a radiation and SEE hardened synchronous buck regulator capable of operating over an input voltage range of 3V to 13.2V. The part is hardened for the total dose and single event effects environments through hardened by design methods and uses a commercial submicron BiCMOS power management process.

With integrated MOSFETs and external loop compensation, this highly efficient single chip power solution provides a tightly regulated output voltage that is externally adjustable from 0.6V to ~85% of the input voltage. Continuous output load current capability is 6A for  $T_J \leq +125^{\circ}C$  and 3A for  $T_J \leq +150^{\circ}C$ .

The ISL70003SEH uses voltage mode architecture with feed-forward and switches at a fixed frequency of 500kHz or 300kHz. Loop compensation is externally adjustable to allow for an optimum balance between stability and output dynamic performance. The internal synchronous power MOSFETs are optimized for high efficiency and excellent thermal performance.

The chip features two logic-level disable inputs that can be used to inhibit pulses on the phase (LXx) pins in order to maximize efficiency based on the load current. The ISL70003SEH also supports DDR power applications. It can sink 4A of continuous load current and contains a buffer amplifier for the generating the V<sub>REF</sub> voltage. High integration, best in class radiation performance and a feature filled design

# TEST REPORT

AN1913 Rev 1.00 March 2, 2015

make the ISL70003SEH an ideal choice for a POL solution for space applications.

### **SEE Summary**

A few of the key SEE results are summarized as follows:

- No destructive SEE at LET = 86.4MeV cm<sup>2</sup>/mg

- Max  $V_{IN}$  = 14.7V with 7A load

- Max  $V_{IN}$  = 13.7V with negative inductor valley current

- No SEFIs at LET = 86.4 MeV cm<sup>2</sup>/mg with V<sub>IN</sub> > 5.5 V

- + No SETs >3% of V<sub>OUT</sub>, for 13.2V V<sub>IN</sub> to 3.3V V<sub>OUT</sub> at 3A load

# **SEE Test Objective**

The ISL70003SEH was tested to determine its susceptibility to destructive effects including single event latch-up (SEL), single event burnout (SEB) and single event gate rupture (SEGR) and to nondestructive effects including single event transient (SET) and single event functional interrupt (SEFI). We will discuss the results in that order. The sample sizes reflected the requirements of MIL-PRF-38535 (QML) and used final version of production parts.

# **SEE Test Facility**

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility. This facility is coupled to a K500 superconducting cyclotron, which is capable of generating a wide range of test particles with the various energy, flux and fluence levels needed for advanced radiation testing.

# **SEE Test Procedure**

The part was tested for SEL/SEB/SEGR, using Au ions at zero degree incidence (LET = 86.4MeV  $\cdot$  cm<sup>2</sup>/mg) with a case temperature of +125 °C and single event transient characterized using Au ions with a case temperature of +25 °C with the samples at zero degree incident beam angle. Single event functional interrupt testing was done using Au ions and Pr ions with a case temperature of +25 °C. SEFI tests conducted with Au ions were done with the samples at zero degree incident beam angle and tests with Pr ions were done with a 15° incident beam angle to achieve an LET of 60MeV  $\cdot$  cm<sup>2</sup>/mg.

The device under test (DUT) was mounted in the beam line and irradiated with heavy ions of the appropriate species. The parts were assembled in 64 Ld quad flatpack packages with the metal lid removed for beam exposure. The beam was directed onto the exposed die and the beam flux, beam fluence and errors in the device outputs were measured.

The tests were controlled remotely from the control room. All input power was supplied from portable power supplies connected via cable to the DUT. The supply currents were

monitored along with the device outputs. All currents were measured with digital ammeters, while all the output waveforms were monitored on a digital oscilloscope for ease of identifying the different types of SEE displayed by the part. Events were captured by triggering on changes in the output **1**.

### **SEE Test Set-Up Diagrams**

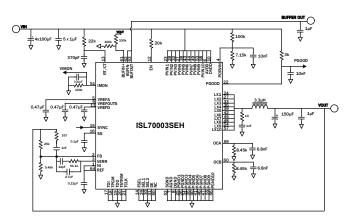

A schematic of the SEE engineering board used during testing is shown in Figure 1.

FIGURE 1. ISL70003SEH SEE TEST BOARD SCHEMATIC

### **Cross-section Calculation**

Cross sections (CS) are calculated as shown by Equation 1:

CS(LET) = N/F

Where:

- CS is the SET cross section (cm<sup>2</sup>), expressed as a function of the heavy ion LET

- LET is the linear energy transfer in MeV cm<sup>2</sup>/mg, corrected according to the incident angle, if any.

- N is the total number of SET events

- F is fluence in particles/cm<sup>2</sup>

A value of 1/F is the assumed cross section when no event is observed.

### **Destructive SEE Results**

The first testing sequence looked at destructive effects due to burnout, latch-up or gate rupture. A burnout condition is indicated by a permanent change in the device supply current (in any condition) after application of the beam. A permanent change in the supply current of the device may also be indicative of single event gate rupture, as the damaged gate insulator can no longer control the current through integrated MOSFETs. If the increased current can be reset by cycling power, it is termed a non-destructive latch-up.

Destructive SEE test were done with the input voltage set to 13.7V or 14.7V, depending on whether the DUT is sourcing current or sinking current. The samples were irradiated in three configurations: disabled (zero output current but power applied), output current set at +7.0A (sourcing) and output current set at -4.0A (sinking). In all three cases the output voltage was set at 3.3V and the case temperature was maintained at +125°C using an external heater. The failure criterion used for defining destructive SEE was a 5% increase in operating current or a 5% shift in the DC overcurrent protection (OCP) trip point. Failed devices were not further irradiated.

Subsequently, four additional samples, (identified as 1A, 2A, 3A, 4A) were irradiated at 14.7V with an output current of 7A. These samples were then irradiated with the output current set at -4.0A (sinking) at 13.7V. Again these samples were irradiated with the output current set at 0A (open) at 14.7V with 1 of the 4 samples having a significant change in shut down current at this point.

<u>Tables 1</u> through <u>4</u>, summarize the results of the destructive SEE testing. The results demonstrate that the device passes the objective maximum in-beam supply voltage specification of 14.7V at the specified LET of 86MeV  $\cdot$  cm<sup>2</sup>/mg for the disabled and sourcing current with no negative valley inductor current, and of 13.7V in sourcing with negative valley inductor current or in sinking configurations.

### **Output Voltage SET Results**

### **Test Setup**

(EQ. 1)

Single event transient (SET) testing of the ISL70003SEH was carried out with the samples configured as a single-phase converter operating at 3.0A output current. The samples were irradiated using Au ions at a zero degree incident beam angle for an effective LET of 86MeV  $\cdot$  cm<sup>2</sup>/mg. Two different I/O conditions were tested. The first configuration was a 3V input to 1.8V output and the second was a 13.2V input to 3.3V output. The samples were tested at two different switching frequencies. The first switching frequency was 300kHz generated by the internal oscillator of the ISL70003SEH. The second frequency was 500kHz and was generated by an arbitrary waveform generator whose output was to connect to the SYNC pin of the DUT. The flux for each run was  $5.0 \times 10^4$  ions/cm<sup>2</sup> • s. An SET was defined as an output voltage perturbation of ±40mV, with an objective of not exceeding ±3% of the output voltage. The output LC filter of the buck regulator during testing for a 3V input was a  $3.3\mu H$  inductor with a single  $150\mu F$  tantalum capacitor in parallel with a 1µF ceramic capacitor for high frequency filtering of the output voltage (see Figure 1). In the high voltage SET testing the inductor was changed to 6.8µH.

### **Oscilloscope Setup**

An oscilloscope was used to capture the deviations of the output. The connections for the scope are described as follows:

Oscilloscope Channel Connections and Settings:

- CH1 =  $V_{OUT}$  50mV/div, trigger on ±40mV window

- CH2 = LX 680mV/div for 3V, 5V/div for 13.2V

- CH3 =  $V_{ERR}$  50mV/div

- CH4 =  $V_{REF}$  50mV/div

- Time scale = 20µs/div

#### **Cross Section Results**

Table 5 details the cross section results of the SET testing of the ISL70003SEH. The table is divided into two sections. The top section shows the cross section results with the input to the DUT at 3V. The bottom section shows the results for a 13.2V input to the DUT. Each section compares the results of the cross section due to the use of the internal oscillator versus an external synchronization signal. A total of 8 devices were used for SET testing. Four devices were allocated for the 3V input test and 4 devices for the 13.2V input test. Each device had two runs, each consisting of using the internal versus external oscillator.

#### TABLE 1. ISL70003SEH DETAILS OF SEB/L TESTS FOR VIN = 14.7V AND DUT DISABLED

| TEMP<br>(°C) | V <sub>IN</sub><br>(V) | I <sub>OUT</sub><br>(A) | LET<br>(MeV • cm <sup>2</sup> /mg) | SUPPLY<br>CURRENT<br>PRE-<br>EXPOSURE<br>(mA) | SUPPLY<br>CURRENT<br>POST-<br>EXPOSURE<br>(mA) | DESTRUCTIVE<br>EVENTS | CUMULATIVE<br>FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | CUMULATIVE<br>CROSS<br>SECTION<br>(cm <sup>2</sup> ) | DEVICE<br>ID | SEB  |

|--------------|------------------------|-------------------------|------------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------|-------------------------------------------------------|------------------------------------------------------|--------------|------|

| 125          | 14.7                   | N/A                     | 86.4                               | 97.1                                          | 97.3                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 1            | PASS |

| 125          | 14.7                   | N/A                     | 86.4                               | 98.5                                          | 98.2                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 2            | PASS |

| 125          | 14.7                   | N/A                     | 86.4                               | 96.8                                          | 97.1                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 3            | PASS |

| 125          | 14.7                   | N/A                     | 86.4                               | 99.3                                          | 99.1                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 4            | PASS |

|              |                        | P.                      | 1                                  |                                               | TOTAL EVENTS                                   | 0                     |                                                       |                                                      |              |      |

|              |                        |                         |                                    |                                               | OV                                             | ERALL FLUENCE         | 2.0 x 10 <sup>7</sup>                                 |                                                      |              |      |

|              |                        |                         |                                    |                                               |                                                |                       | OVERALL CS                                            | 5.0 x 10 <sup>-8</sup>                               |              |      |

|              |                        |                         |                                    |                                               |                                                |                       | L. L              | TOTAL UNITS                                          | 4            |      |

#### TABLE 2. ISL70003SEH DETAILS OF SEB/L TESTS FOR V<sub>IN</sub> = 14.7V SOURCING 7A

| TEMP<br>(°C) | V <sub>IN</sub><br>(V) | lout<br>(A) | LET<br>(MeV∙cm <sup>2</sup> ∕mg) | SUPPLY<br>CURRENT<br>PRE-<br>EXPOSURE<br>(mA) | SUPPLY<br>CURRENT<br>POST-<br>EXPOSURE<br>(mA) | DESTRUCTIVE<br>EVENTS | CUMULATIVE<br>FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | CUMULATIVE<br>CROSS<br>SECTION<br>(cm <sup>2</sup> ) | DEVICE<br>ID | SEB  |

|--------------|------------------------|-------------|----------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------|-------------------------------------------------------|------------------------------------------------------|--------------|------|

| 125          | 14.7                   | N/A         | 86.4                             | 97.1                                          | 97.1                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 1            | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 98.6                                          | 98.5                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 2            | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 97.1                                          | 97.7                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 3            | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 99.1                                          | 99.1                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 4            | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 93.6                                          | 93.5                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 1A           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 94.2                                          | 94.6                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 2A           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 91.2                                          | 92.2                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | ЗA           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 94.1                                          | 93.9                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 4A           | PASS |

|              |                        |             |                                  |                                               | TOTAL EVENTS                                   | 0                     |                                                       |                                                      |              |      |

|              |                        |             |                                  |                                               | OV                                             | ERALL FLUENCE         | 4.0 x 10 <sup>7</sup>                                 |                                                      |              |      |

|              |                        |             |                                  |                                               |                                                |                       | OVERALL CS                                            | 2.5 x 10 <sup>-8</sup>                               |              |      |

|              |                        |             |                                  |                                               |                                                |                       |                                                       | TOTAL UNITS                                          | 8            |      |

| TEMP<br>(°C) | V <sub>IN</sub><br>(V) | lout<br>(A) | LET<br>(MeV•cm <sup>2</sup> /mg) | SUPPLY<br>CURRENT<br>PRE-<br>EXPOSURE<br>(mA) | SUPPLY<br>CURRENT<br>POST-<br>EXPOSURE<br>(mA) | DESTRUCTIVE<br>EVENTS | CUMULATIVE<br>FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | CUMULATIVE<br>CROSS<br>SECTION<br>(cm <sup>2</sup> ) | DEVICE<br>ID | SEB  |

|--------------|------------------------|-------------|----------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------|-------------------------------------------------------|------------------------------------------------------|--------------|------|

| 125          | 13.7                   | N/A         | 86.4                             | 93.9                                          | 93.9                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 5            | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 94.8                                          | 94.3                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 6            | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 94.4                                          | 94.5                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 7            | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 94.9                                          | 95.2                                           | 0                     | 5.0 x 10 <sup>6</sup>                                 | 2.0 x 10 <sup>-7</sup>                               | 8            | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 91.1                                          | 90.8                                           | 0                     | 1.0 x 10 <sup>7</sup>                                 | 1.0 x 10 <sup>-7</sup>                               | 1A           | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 91.9                                          | 92.5                                           | 0                     | <b>1</b> .0 x <b>1</b> 0 <sup>7</sup>                 | 1.0 x 10 <sup>-7</sup>                               | 2A           | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 89.2                                          | 89.8                                           | 0                     | 1.0 x 10 <sup>7</sup>                                 | 1.0 x 10 <sup>-7</sup>                               | ЗA           | PASS |

| 125          | 13.7                   | N/A         | 86.4                             | 91.8                                          | 91.8                                           | 0                     | 1.0 x 10 <sup>7</sup>                                 | 1.0 x 10 <sup>-7</sup>                               | 4A           | PASS |

|              | 1                      | ł           |                                  |                                               | TOTAL EVENTS                                   | 0                     |                                                       |                                                      |              |      |

|              |                        |             |                                  |                                               | ov                                             | ERALL FLUENCE         | 6.0 x 10 <sup>7</sup>                                 |                                                      |              |      |

|              |                        |             |                                  |                                               |                                                |                       | OVERALL CS                                            | 1.7 x 10 <sup>-8</sup>                               |              |      |

|              |                        |             |                                  |                                               |                                                |                       |                                                       | TOTAL UNITS                                          | 8            |      |

TABLE 3. ISL70003SEH DETAILS OF SEB/L TESTS FOR  $\rm V_{IN}$  = 13.7V SINKING 4A

### TABLE 4. ISL70003SEH DETAILS OF SEB/L TESTS FOR $\rm V_{IN}$ = 14.7V, OUTPUT OPEN

| TEMP<br>(°C) | V <sub>IN</sub><br>(V) | lout<br>(A) | LET<br>(MeV•cm <sup>2</sup> /mg) | SUPPLY<br>CURRENT<br>PRE-<br>EXPOSURE<br>(mA) | SUPPLY<br>CURRENT<br>POST-<br>EXPOSURE<br>(mA) | DESTRUCTIVE<br>EVENTS | CUMULATIVE<br>FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | CUMULATIVE<br>CROSS<br>SECTION<br>(cm <sup>2</sup> ) | DEVICE<br>ID | SEB  |

|--------------|------------------------|-------------|----------------------------------|-----------------------------------------------|------------------------------------------------|-----------------------|-------------------------------------------------------|------------------------------------------------------|--------------|------|

| 125          | 14.7                   | N/A         | 86.4                             | 92.2                                          | 92.3                                           | 0                     | 1.5 x 10 <sup>7</sup>                                 | 6.7 x 10 <sup>-8</sup>                               | 1A           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 94.6                                          | 94.6                                           | 0                     | 1.5 x 10 <sup>7</sup>                                 | 6.7 x 10 <sup>-8</sup>                               | 2A           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 92.1                                          | 91.6                                           | 0                     | 1.5 x 10 <sup>7</sup>                                 | 6.7 x 10 <sup>-8</sup>                               | ЗA           | PASS |

| 125          | 14.7                   | N/A         | 86.4                             | 94.2                                          | 95.5                                           | 1                     | 1.5 x 10 <sup>7</sup>                                 | 6.7 x 10 <sup>-8</sup>                               | 4A           | FAIL |

|              |                        |             |                                  |                                               |                                                |                       |                                                       |                                                      |              |      |

|              |                        |             | 6.0 x 10 <sup>7</sup>            |                                               |                                                |                       |                                                       |                                                      |              |      |

|              |                        |             | OVERALL CS                       | 1.7 x 10 <sup>-8</sup>                        |                                                |                       |                                                       |                                                      |              |      |

|              | TOTAL UNITS            |             |                                  |                                               |                                                |                       |                                                       |                                                      | 4            |      |

| V <sub>IN</sub> (V) | V <sub>OUT</sub><br>(V) | NUMBER OF<br>DEVICES | FSW (kHz)      | EFFECTIVE LET<br>(MeV·cm <sup>2</sup> /mg) | FLUENCE PER RUN<br>(PARTICLES/cm <sup>2</sup> ) | NUMBER OF<br>RUNS | TOTAL SET<br>EVENTS | EVENT CS<br>(cm <sup>2</sup> ) |

|---------------------|-------------------------|----------------------|----------------|--------------------------------------------|-------------------------------------------------|-------------------|---------------------|--------------------------------|

|                     |                         |                      |                |                                            |                                                 |                   |                     |                                |

| 3.0                 | 1.8                     | 4                    | 300 (internal) | 86                                         | 1.0 x 10 <sup>7</sup>                           | 4                 | 1534                | 3.84 x 10 <sup>-5</sup>        |

| 3.0                 | 1.8                     | 4                    | 500 (external) | 86                                         | 1.0 x 10 <sup>7</sup>                           | 4                 | 1359                | 3.40 x 10 <sup>-5</sup>        |

|                     |                         |                      | Tota           | I Fluence per run                          | 2.0 x 10 <sup>7</sup>                           |                   |                     |                                |

|                     |                         |                      |                |                                            | Total Runs                                      | 8                 |                     |                                |

|                     |                         |                      |                |                                            | Тс                                              | otal SET Events   | 2893                |                                |

|                     |                         |                      |                |                                            |                                                 |                   | Total Cross Section | 7.23 x 10 <sup>-5</sup>        |

| 13.2                | 3.3                     | 4                    | 300 (internal) | 86                                         | 1.0 x 10 <sup>7</sup>                           | 4                 | 1216                | 3.04 x 10 <sup>-5</sup>        |

| 13.2                | 3.3                     | 4                    | 500 (external) | 86                                         | 1.0 x 10 <sup>7</sup>                           | 4                 | 1889                | 4.72 x 10 <sup>-5</sup>        |

|                     |                         | I                    | Tota           | I Fluence per run                          | 2.0 x 10 <sup>7</sup>                           |                   |                     |                                |

|                     |                         |                      |                |                                            | Total Runs                                      | 8                 |                     |                                |

|                     |                         |                      |                |                                            | Total SET Events                                |                   | 3105                |                                |

|                     |                         |                      |                |                                            |                                                 |                   | Total Cross Section | 7.76 x 10 <sup>-5</sup>        |

#### TABLE 5. ISL70003SEH DETAILS OF THE SET CROSS SECTION

### **Voltage Deviation Results**

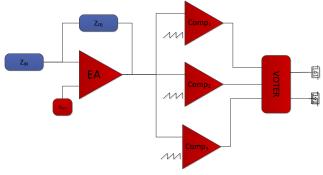

Compared to other Intersil point of load (POL) regulators, the ISL70003SEH employs a quasi-triple redundant control loop to give system designers the ability to achieve an optimal balance between stability and dynamic response. The quasi redundant loop employs only one error amplifier in the control loop of the regulator. This was needed for external compensation of the error amplifier. There is still however redundancy in the PWM circuitry, as the output of the error amplifier is connected to three comparators and then its output goes through a voter circuitry to drive the internal MOSFETs, (see Figure 2).

\* Blue fill indicates external compensation

FIGURE 2. ISL70003SEH QUASI REDUNDANT CONTROL LOOP

Due to the lack of three independent error amplifiers, the ISL70003SEH is expected to have larger voltage deviations due to SETs than its predecessors. However, it is still expected that the LX pulse train would only have a single pulse perturbation due to an SET since the voter logic is still employed in the PWM circuitry.

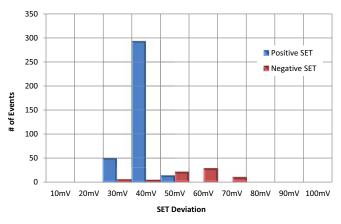

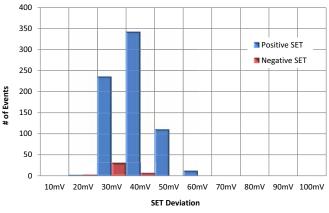

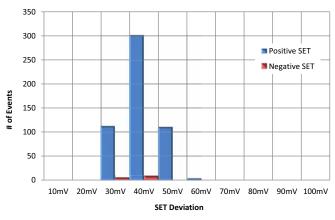

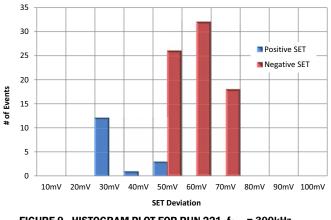

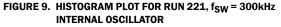

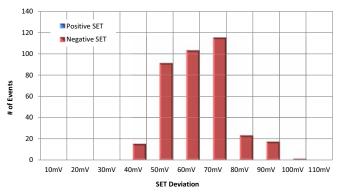

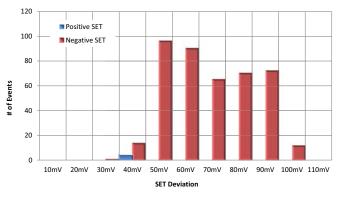

#### HISTROGRAM PLOTS

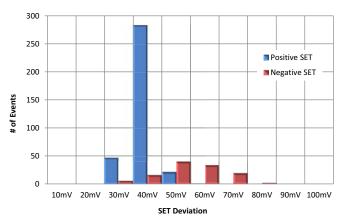

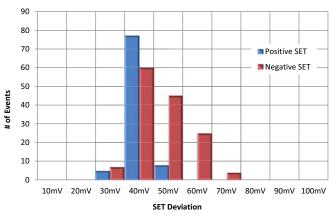

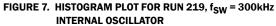

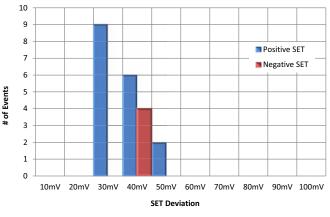

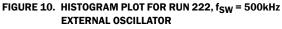

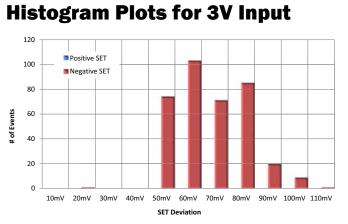

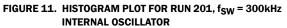

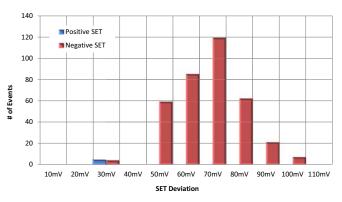

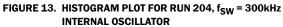

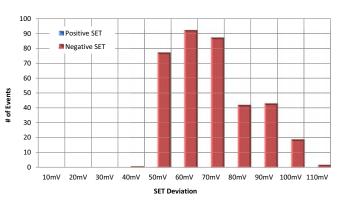

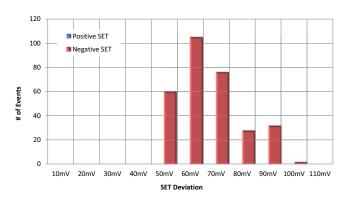

Figures 3 through 10 show histograms of the magnitude of the voltage deviation for each run of SET testing for 13.2V input test. They plot both the negative and positive transients counts and are binned in 10mV increments up to 100mV, which represents 3% of the nominal 3.3V output voltage.

A count that falls into the bin represents an SET whose deviation is equal to or larger than the previous bin but less than that bin. For example, in Figure 3 there are approximately 300 positive SET counts that are classified in the 40mV bin. This means that there were ~300 positive SETs that were equal to or larger than 30mV but less than 40mV.

For the 13.2V input to 3.3V output configuration the SET data shows that majority of the SETs were positive and between 30mV and 40mV, which translates to 0.9% to 1.2% of the output voltage. The max deviation was a negative transient with 80mV in magnitude found in run 217 with a count of 2. Total deviation of 80mV translates to 2.4% of the output voltage.

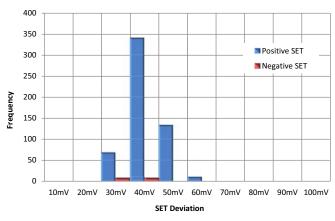

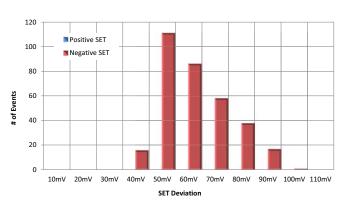

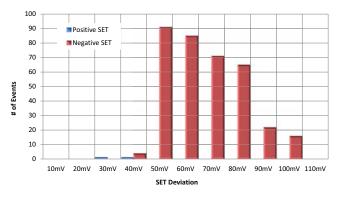

Figures 11 through 18 show the histogram of the magnitude of the voltage deviation for the 3V input to 1.8V output configuration. The binning is done the same way as the high voltage tests, except the max bin is now 110mV. The SET data shows the majority of the SETs were in the negative direction and between 50mV to 60mV, which is 2.7% to 3.3% of the output voltage. There were three captures that fell under the 110mV bin, one in run 201 and two in run 202. The maximum deviation was 105mV in run 201 and the ones in run 202 were 100.2mV and 100.4mV deviations. The maximum deviation of 105mV is 5.8% of the output voltage. To minimize SETs for low input voltages, it is recommended to add more output capacitance, which is typical for a low output voltage that needs to meet tight regulation. All of the SEE testing was done with a single 150µF tantalum capacitor on the output.

### **Histogram Plots for 13.2V Input**

FIGURE 5. HISTOGRAM PLOT FOR RUN 217, f<sub>SW</sub> = 300kHz INTERNAL OSCILLATOR

FIGURE 4. HISTOGRAM PLOT FOR RUN 216, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

FIGURE 6. HISTOGRAM PLOT FOR RUN 218, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

FIGURE 8. HISTOGRAM PLOT FOR RUN 220, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

### Histogram Plots for 13.2V Input (Continued)

FIGURE 12. HISTOGRAM PLOT FOR RUN 202, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

FIGURE 14. HISTOGRAM PLOT FOR RUN 205, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

# Histogram Plots for 3V Input (Continued)

FIGURE 15. HISTOGRAM PLOT FOR RUN 207,  $f_{SW}$  = 300kHz INTERNAL OSCILLATOR

FIGURE 17. HISTOGRAM PLOT FOR RUN 210, f<sub>SW</sub> = 300kHz INTERNAL OSCILLATOR

FIGURE 16. HISTOGRAM PLOT FOR RUN 208, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

FIGURE 18. HISTOGRAM PLOT FOR RUN 211, f<sub>SW</sub> = 500kHz EXTERNAL OSCILLATOR

#### SINGLE EVENT TRANSIENT RESPONSE

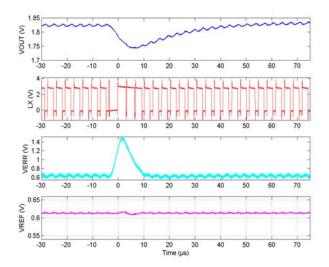

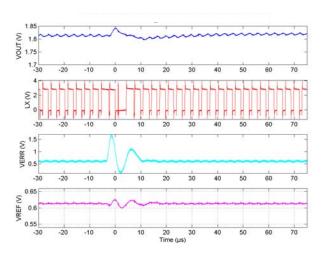

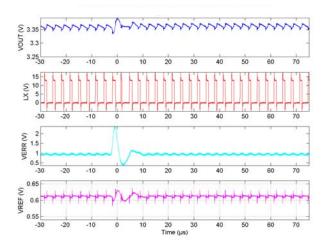

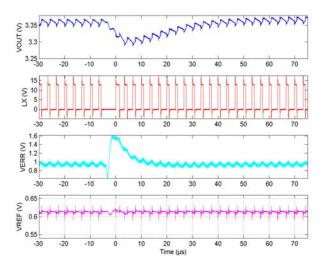

The previous section provided data on the peak magnitude of the deviation on the output voltage due to a SET. This section provides example captures of the transient seen during SEE testing. Figures 19 and 20 are positive and negative SET captures for the 3V input to 1.8V output configurations. Figures 21 and 22 show similar SET captures for 13.2V input to 3.3V output operation.

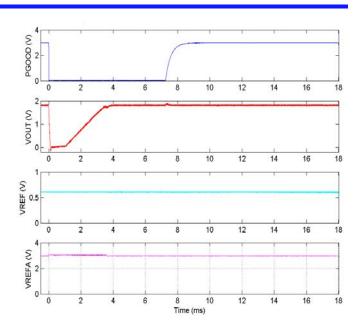

Figure 19 represents a typical negative transient, caused by a shortened pulse in the cycle previous to time = 0, followed by three maximum duty cycle pulses. There is clearly only a one pulse disruption followed by the regulator adjusting its duty cycle to recover from the disruption of normal operation. Recovery is very controlled and duration is ~40µs. The actual time below 3% is even shorter (<20µs). The response of the output is similar to a transient load step in which the capacitance value dominates the droop. As previously mentioned, adding a second capacitor on the output would reduce the deviation by approximately half.

Figure 20 shows a positive transient when the DUT is operated from a 3V input. Two clock cycles before trigger captures at t = 0, one can see the increase in duty cycle of the LX pulse train due to the ion strike, which leads to the positive SET. The larger duty cycle increases the output voltage and the regulator corrects the error by terminating the following LX pulses at lower duty cycles. The recovery of the output voltage is controlled with no oscillations and is quick with recovery to nominal output voltage in less than 20µs.

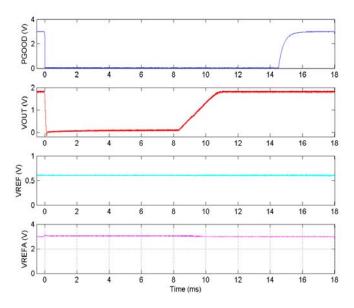

Figure 21 is an example of a positive SET when the DUT is operated from a 13.2V input. A single elongated pulse is seen in the LX plot, in the clock cycle before time = 0 followed by a shortened pulse due to the regulator trying to recover from the increased output voltage. Recovery is controlled and less than 10 $\mu$ s. Once again the LX pulse train only shows one disturbance due to an SET.

FIGURE 19. NEGATIVE SET, RUN 201 CAPTURE 3, VIN = 3V

FIGURE 20. POSITIVE SET, RUN 204 CAPTURE 204,  $V_{IN}$  = 3V

FIGURE 21. POSITIVE SET, RUN 217 CAPTURE 117, VIN = 13.2V

Figure 22, shows a negative transient when the DUT is configured to operate from a 13.2V input. A skipped LX pulse causes a droop in the output voltage. As a result, the error amplifier's output increases and induces the next pulses to have a longer on time to regulate the output voltage to its steady state value. There is only one disturbance in the LX pulse train that is induced by the heavy ion strike.

FIGURE 22. NEGATIVE SET, RUN 217 CAPTURE 242,  $V_{\mbox{\rm IN}}$  = 13.2V

### **Single Event Functional Interrupt Results**

Single event functional interrupt (SEFI) phenomena were encountered in previous testing of POL regulators, therefore, it was an extensive part of SEE testing [1] [2]. SEFI phenomena for the ISL70001SRH and ISL70002SRH were encountered only at low supply voltage (3V), hence there was an expectation to encounter SEFI at the same supply level. A single event functional interrupt is defined as a non destructive event resulting in the disruption of normal operation of the part, followed by a recovery to normal operation through a soft-start cycle.

For the SEFI tests, the input voltages tested were 3V, 5.5V and 13.2V. The samples were irradiated at an LET of 86 MeV  $\cdot$  cm<sup>2</sup>/mg and 60 MeV  $\cdot$  cm<sup>2</sup>/mg, using Au and Pr ions respectively. The PGOOD pin of the DUT was monitored through a scope and counts were taken as the scope triggered on a falling edge of PGOOD. The trigger level was set to 50% of the PGOOD pull-up voltage. Other monitored signals included VOUT, REF and VREFA.

SEFI events were observed at 3V input and LET = 86 MeV  $\cdot$  cm<sup>2</sup>/mg only. No SEFI's were seen with 5.5V or 13.2V input at LET 86.4 MeV  $\cdot$  cm<sup>2</sup>/mg and with 3V input at LET 60 MeV  $\cdot$  cm<sup>2</sup>/mg. Table 6 summarizes the SEFI cross section results of the ISL70003SEH.

| V <sub>IN</sub><br>(V) | V <sub>OUT</sub><br>(V) | I <sub>OUT</sub><br>(A) | LET<br>(MeV•cm <sup>2</sup> /mg) | SPECIES | FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | RUNS | SEFI EVENTS | CUMULATIVE CROSS<br>SECTION (cm <sup>2</sup> ) |  |  |  |  |

|------------------------|-------------------------|-------------------------|----------------------------------|---------|-----------------------------------------|------|-------------|------------------------------------------------|--|--|--|--|

| 3.0                    | 1.8                     | 3                       | 86.4                             | Au      | 1.0 x 10 <sup>7</sup>                   | 8    | 44          | 5.5 x 10 <sup>-7</sup>                         |  |  |  |  |

| 3.0                    | 1.8                     | 3                       | 60                               | Pr      | 1.0 x 10 <sup>7</sup>                   | 4    | 0           | 2.5 x 10 <sup>-8</sup>                         |  |  |  |  |

| 5.5                    | 1.8                     | 3                       | 86.4                             | Au      | 1.0 x 10 <sup>7</sup>                   | 4    | 0           | 2.5 x 10 <sup>-8</sup>                         |  |  |  |  |

| 13.2                   | 3.3                     | 3                       | 86.4                             | Au      | 1.0 x 10 <sup>7</sup>                   | 8    | 0           | 1.3 x 10 <sup>-8</sup>                         |  |  |  |  |

#### TABLE 6. ISL70003SEH SEFI CROSS SECTION SUMMARY

All SEFI signatures observed showed a spontaneous recovery to normal operation. Some were restarts, while others were a hiccup cycle (which is a dummy soft-start cycle) followed by a restart. The recovery time is a function of the value of the soft-start capacitor used as an SEE fixture. The SEFI cross section for 3V input was  $5.5 \times 10^{-7/}$  cm<sup>2</sup>, indicating a very low probability of occurrence of this phenomenon.

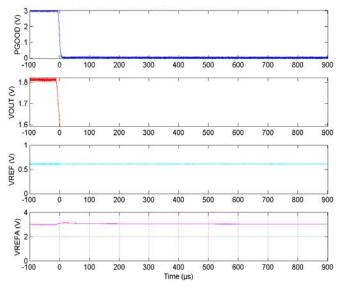

Figure 23 shows an ISL70003SEH SEFI signature at LET = 86.4 MeV  $\cdot$  cm<sup>2</sup>/mg at 3V input. The PGOOD output drops to zero as output voltage decays to zero. VREF remains at 600mV and VREFA remains at 3V indicating an active regulator. The horizontal axis is calibrated at 100µs per division.

Figure 24 shows another SEFI response with the time scale changed to 2ms per division. This response shows the regulator starting up ~1ms after the SEFI occurs. This is consistent with the delay interval of 512 clock cycles seen after fault condition, such as overcurrent protection occurs.

Figure 25 shows a SEFI signature with a hiccup cycle. In this signature the regulator goes through a dummy soft-start before it starts backup. In all cases, the regulator does not need a reset or removal of power to restart.

FIGURE 23. SEFI, RUN 204 CAPTURE 2, VIN = 3V

FIGURE 24. SEFI, RUN 208 CAPTURE 1, VIN = 3V

FIGURE 25. SEFI, RUN 204 CAPTURE 1, V<sub>IN</sub> = 3V

### **SET Results of Other Outputs**

The ISL70003SEH is a highly integrated buck regulator, which features a current monitor output and internal buffer to generate the  $V_{REF}$  voltage necessary in DDR power applications. In conjunction with SET and SEFI testing of the output voltage, both of these outputs were also monitored during SET testing. These features were not intended to be single event transient immune therefore, it is important to characterize their SET behavior with cross section results and composite plots of the transient response.

### **IMON Current Sense Output SET Results**

The ISL70003SEH provides a current monitor function through the IMON pin. Current monitoring informs designers if down steam loads are operating as expected and to measure the overall performance of a system. The IMON pin outputs a high speed analog current source that is proportional to the sensed peak current through the ISL70003SEH. In typical applications, a resistor R<sub>IMON</sub> is connected to the IMON pin to convert the sensed current to voltage, V<sub>IMON</sub>.

For 13.2V input tests  $R_{IMON}$  was set to  $100 k\Omega$  and for 3V input test  $R_{IMON} = 50 k\Omega$ . In both configurations there was a 100 pF ceramic capacitor to reduce the switching noise in the IMON signal. A trigger window of  $\pm 80 mV$  was used to capture and count the events on IMON. This equates to a  $\pm 2.7\%$  deviation with respect to the 3A load current.

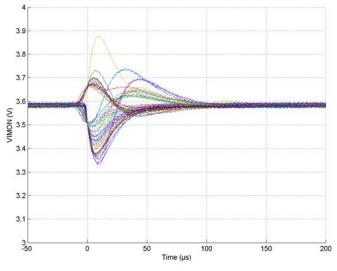

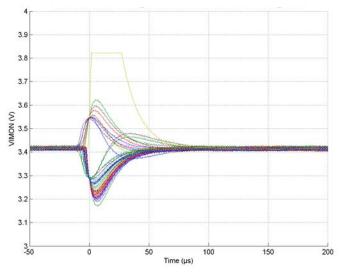

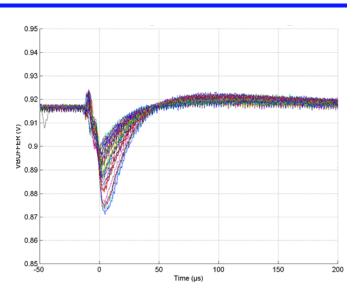

Figure 26 is a composite plot of the first 50 captures of run 215. In this run the input voltage was 13.2V, output conditions were 3.3V output with 3A load and the regulator switching at 300kHz. The transients are both positive and negative with a controlled response to its nominal value within 100µs. Peak transients in this example is ~300mV, which equates to 10% of the load current. Since the IMON output is not intended to be a real time representation of the current through the regulator but a long term diagnostic tool to evaluate the overall performance of the system's load, it is more important that an SET does not cause a permanent shift in the average value than the actual peak deviation induced by the SET.

FIGURE 26. IMON COMPOSITE SET PLOT, RUN 215, VIN = 13.2V

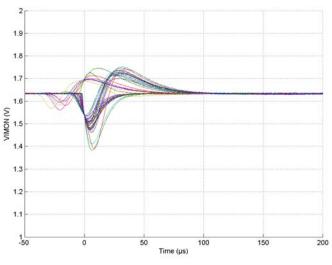

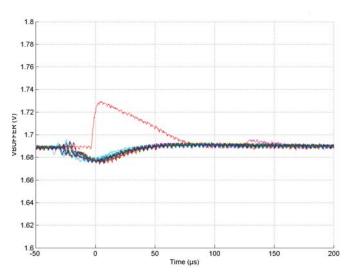

Figure 27 is a composite plot of the first 50 captures of run 220. In this run the input voltage was 13.2V, output conditions were 3.3V output with 3A load and the regulator switching at 500kHz. Due to the higher switching frequency, the peak current through the regulator is smaller, this is reflected by the average VIMON being lower in this figure compared to Figure 26. The response is similar to previous composite plot, except for the one railed out transient. In a worst case condition a SET on the IMON circuitry could cause the output signal to rail to in the internal bias (VREFA) of the ISL70003SEH.

FIGURE 27. IMON COMPOSITE SET PLOT, RUN 220,  $V_{IN}$  = 13.2V

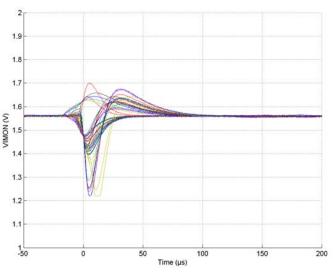

Figures 28 and 29 show the results with a 3V input switching at 300kHz and 500kHz, respectively.  $R_{IMON} = 50k\Omega$  the VIMON average voltage is approximately half of the high input voltage configuration. Figure 29 the IMON signal is railed below the capture window. In a worst case condition, the IMON signal can swing to ground. However, the signal recovers within 100µs to its nominal value indicating there has been no permanent change in the load current

FIGURE 28. IMON COMPOSITE SET PLOT, RUN 207, VIN = 3V

FIGURE 29. IMON COMPOSITE SET PLOT, RUN 211,  $V_{IN}$  = 3V

Table 7 gives details of the cross section for the IMON output signal. All tests were done with Au ions at zero degrees for an LET of 86.4MeV • cm2/mg. Four devices were run for each configuration, however for the 3V input test the first runs had erroneous trigger conditions. The captures were terminated early and the data is not used in the calculations.

### **Buffer Output SET Results**

The buffer amplifier is used to generate the reference voltage (V<sub>REF</sub>) for the DDR memory chips. Sourcing capability of the buffer amplifier is 10mA typical and needs a minimum of 1µF load capacitance for stability. Typical applications will tie the output voltage of the regulator through an R/R resistor divider and configure the amplifier in unity gain. Figure 1 shows the board included two 100k resistors to divide the output voltage by half and connect to the non-inverting input of the buffer amplifier. The amp was configured in unity gain with a 1µF capacitor load. Two devices of each varying input voltage had an additional 62.5 $\Omega$  load to test the device at no load and loaded condition. In DDR application, the V<sub>REF</sub> connection is a high impedance input and the buffer amplifier, will have very light load.

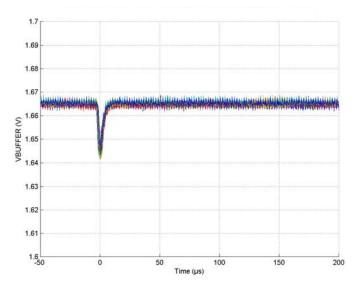

<u>Table 8</u> shows the cross section results of the buffer amplifier. An SET was characterized as a  $\pm$ 40mV deviation of buffer output, which coincides with the limit on V<sub>REF</sub> for DDRI applications. The table also clearly shows the effect of loading on the counts of the SET. As mentioned before, DDR applications will have very light to no load on the buffer amplifier, which is a plus due to the small cross sections achieved in the no load condition.

| V <sub>IN</sub><br>(V) | V <sub>OUT</sub><br>(V) | l <sub>out</sub><br>(A) | FSW<br>(kHz) | LET<br>(MeV•cm <sup>2</sup> /mg) | SPECIES | CUMULATIVE FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | EVENTS | CUMULATIVE CROSS<br>SECTION (cm <sup>2</sup> ) |

|------------------------|-------------------------|-------------------------|--------------|----------------------------------|---------|----------------------------------------------------|--------|------------------------------------------------|

| 3.0                    | 1.8                     | 3                       | 300          | 86.4                             | Au      | 3.0 x 10 <sup>7</sup>                              | 3490   | 1.2 x 10 <sup>-4</sup>                         |

| 3.0                    | 1.8                     | 3                       | 500          | 86.4                             | Au      | 3.0 x 10 <sup>7</sup>                              | 3456   | 1.2 x 10 <sup>-4</sup>                         |

| 13.2                   | 3.3                     | 3                       | 300          | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 5008   | 1.3 x 10 <sup>-4</sup>                         |

| 13.2                   | 3.3                     | 3                       | 500          | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 6137   | 1.5 x 10 <sup>-4</sup>                         |

#### TABLE 7. ISL70003SEH IMON SET CROSS SECTION SUMMARY

TABLE 8. ISL70003SEH BUFFER AMPLIFIER SET CROSS SECTION SUMMARY

| V <sub>IN</sub><br>(V) | V <sub>ОUT</sub><br>(V) | <sup>I</sup> оит<br>(А) | BUFFER<br>LOAD<br>(Ω) | LET<br>(MeV•cm <sup>2</sup> /mg) | SPECIES | CUMULATIVE FLUENCE<br>(PARTICLES/cm <sup>2</sup> ) | EVENTS | CUMULATIVE CROSS<br>SECTION (cm <sup>2</sup> ) |

|------------------------|-------------------------|-------------------------|-----------------------|----------------------------------|---------|----------------------------------------------------|--------|------------------------------------------------|

| 3.0                    | 1.8                     | 3                       | OPEN                  | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 1      | 2.5 x 10 <sup>-8</sup>                         |

| 3.0                    | 1.8                     | 3                       | 62.5                  | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 1979   | 4.95 x 10 <sup>-5</sup>                        |

| 13.2                   | 3.3                     | 3                       | OPEN                  | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 4      | 1.0 x 10 <sup>-7</sup>                         |

| 13.2                   | 3.3                     | 3                       | 62.5                  | 86.4                             | Au      | 4.0 x 10 <sup>7</sup>                              | 3866   | 9.67 x 10 <sup>-5</sup>                        |

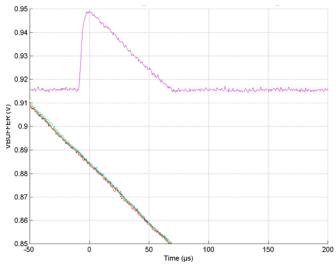

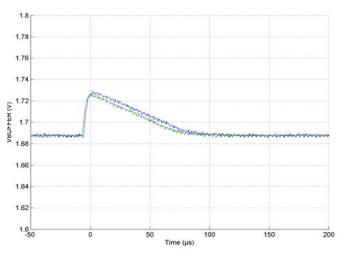

Figure 30 shows the composite plot for 3V input configuration and the buffer unloaded. The graph only shows one true SET of the buffer amplifier, the other captures are due to the SEFIs phenomenon. The peak deviation is ~35mV and recovery is ~75µs after the peak. The response is controlled dominated by the slew rate of the buffer amplifier and exhibits no oscillations. A typical DDR memory will have in the order of meaning will have somewhere around  $20\mu$ F to  $30\mu$ F of capacitive loading on the buffer output, which will help further with SET mitigation.

Figure 31 shows the SET composite plot of the first 50 captures of run 211. The input voltage is 3V and the buffer output is loaded with  $62.5\Omega$ . The SET are mainly negative most likely due to the load resistor to ground. Peak deviations are less than 50mV.

Figure 32 is the composite plot of run 215 with an input voltage of 13.2V and the buffer not resistively loaded. Most likely the only SET due to an ion hit on the buffer circuitry is the positive going trace. The other traces are due to SETs on the output voltage propagating through the resistor divider connected to the non- inverting input of the buffer amp. In DDR applications the V<sub>REF</sub> signal needs to track half of the VDDQ voltage [3]. In our configuration the output voltage and the buffer amplifier is tracking the voltage as intended.

Figure 33 further emphasizes the theory that in Figure 32 there is only one true SET due to the buffer amp. Figure 33 shows the composite plot of run 217. The device is configured in similar fashion and the responses seen on this plot is very similar to the positive SET in Figure 32. In the calculations for cross section mentioned previously the SET induced by tracking of the output voltage were not used.

FIGURE 30. BUFFER COMPOSITE SET PLOT, RUN 201, VIN = 3V

FIGURE 31. BUFFER COMPOSITE SET PLOT, RUN 211, VIN = 3V

FIGURE 32. BUFFER COMPOSITE SET PLOT, RUN 215, VIN = 13.2V

FIGURE 33. BUFFER COMPOSITE SET PLOT, RUN 217, VIN = 13.2V

<u>Figure 34</u> is the composite plot of the 50 first captures of run 222. The buffer is resistively loaded with  $62.5\Omega$ . Once again the SETs are in the negative direction.

In all conditions the response is controlled without oscillations to the output of the buffer amplifier. Typical DDR memory power solutions will have 20 times the amount of capacitive loading, which will mitigate SET. In addition,  $V_{\text{REF}}$  is an input to a differential pair, common-source amplifier, so there will be no significant current draw, which SEE testing has demonstrated will result in a very small SET cross section.

### Summary

### **Destructive SEE**

No SEL/SEB/SEGR was observed for the device up to an LET of 86.4MeV  $\cdot$  cm<sup>2</sup>/mg (+125°C) at a maximum voltage supply of V<sub>IN</sub> = 14.7V when the DUT is disabled or sourcing to the maximum rated load current, providing over 10% margin to the maximum recommended input voltage of 13.2V.

Applications that result in a negative inductor valley current are limited to maximum voltage supply of V<sub>IN</sub> = 13.7V, a 3% margin to the maximum recommended input voltage of 13.2V. In DDR applications typical input voltages are from 3.3V or 5V rails and 13.7V provides more than enough headroom to use this device as a V<sub>TT</sub> termination regulator.

### **Single Event Transient**

Even though complete triple redundancy is not employed in the control loop, the ISL70003SEH provides excellent single event transient response and we have met our goal of <3% deviation. Further mitigation of the transient may be used by increasing the amount of capacitance on the output filter. Testing has been conducted with a single  $150\mu$ F tantalum output capacitor.

The SEFI phenomenon is still seen on the regulator with 3V input voltage at LET 86.4MeV  $\cdot$  cm<sup>2</sup>/mg only and the cross section is very small indicating a low probability of occurrence. Restart of the IC is autonomous with no outside intervention needed to return to normal operation. At a LET 60MeV  $\cdot$  cm<sup>2</sup>/mg the SEFIs go away with 3V input. SEFIs are not seen with input voltages above 5.5V at LET 86.4MeV  $\cdot$  cm<sup>2</sup>/mg.

Additional SET has been done on the buffer amplifier and current monitor. Both outputs demonstrate a controlled response due to an ion strike with no oscillations.

### References

- [1] JEDEC STANDARD JESD8-9A. Stub Series Terminated Logic for 2.5V (SSTL\_2)

- [2] Intersil Web-based report, '<u>Single Event Effects</u> (SEE) Testing of the ISL70002SEH Synchronous Buck Regulator'.

- [3] Intersil Web-based report, '<u>Single Event Effects</u> (SEE) Testing of the ISL70001SRH Synchronous Buck Regulator'.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338