# **DA913x Quick Start**

# 1 Quick Start

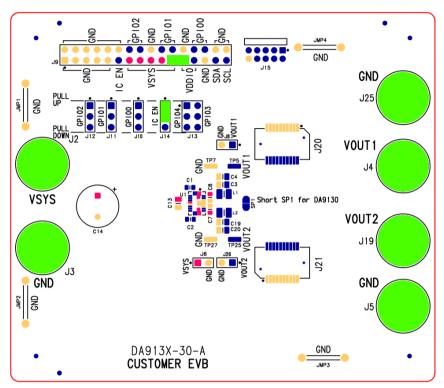

Figure 1: DA913x-30 Jumpers and headers location

Connections from the table below are highlighted in green

Table 1: Jumpers and headers overview

| Connection | Description             | Default                              | Location                                |

|------------|-------------------------|--------------------------------------|-----------------------------------------|

| J14        | IC_EN                   | Jumper fitted to pull-up position    | Top-left, 4th jumper from the left      |

| J9         | GPIO header             | Jumper between VSYS and VDDIO        | TOP left, jumper on positions 21 and 23 |

| J2 - J3    | VSYS - GND              | Supply from PSU, 4V - 5A recommended | Left of EVB                             |

| J4 - J25   | VOUT1 - GND             | Channel 1 output                     | Top right of EVB                        |

| J5 - J19   | VOUT2 [Note 1] -<br>GND | Channel 2 [Note 1] output            | Bottom right of EVB                     |

Note 1 VOUT2 is connected to VOUT1 on DA9130 boards.

## 1.1 Instructions

Make sure the jumper configuration is correct. IC\_EN has to be on pull-up position and VDDIO connected to VSYS.

Connect a bench PSU to VSYS (J2, positive) and GND (J3, return) and make sure it can supply 4V and 5A. Measure the outputs on VOUT1 (J4) and VOUT2 (J19).

Pull-up and pull-down jumpers may be needed on GPIOs 0 to 2 depending on the configuration.

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.