### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Renesas Starter Kit 2+ for SH/7670

User's Manual

Renesas Single-Chip Microcomputer SH Family

Rev.1.00 2008.10

#### Disclaimer

By using this Renesas Starter Kit (RSK), the user accepts the following terms. The RSK is not guaranteed to be error free, and the entire risk as to the results and performance of the RSK is assumed by the User. The RSK is provided by Renesas on an "as is" basis without warranty of any kind whether express or implied, including but not limited to the implied warranties of satisfactory quality, fitness for a particular purpose, title and non-infringement of intellectual property rights with regard to the RSK. Renesas expressly disclaims all such warranties. Renesas or its affiliates shall in no event be liable for any loss of profit, loss of data, loss of contract, loss of business, damage to reputation or goodwill, any economic loss, any reprogramming or recall costs (whether the foregoing losses are direct or indirect) nor shall Renesas or its affiliates be liable for any other direct or indirect special, incidental or consequential damages arising out of or in relation to the use of this RSK, even if Renesas or its affiliates have been advised of the possibility of such damages.

#### Precautions

This Renesas Starter Kit is only intended for use in a laboratory environment under ambient temperature and humidity conditions. A safe separation distance should be used between this and any sensitive equipment. Its use outside the laboratory, classroom, study area or similar such area invalidates conformity with the protection requirements of the Electromagnetic Compatibility Directive and could lead to prosecution.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures;

- ensure attached cables do not lie across the equipment

- reorient the receiving antenna

- increase the distance between the equipment and the receiver

- connect the equipment into an outlet on a circuit different from that which the receiver is connected

- power down the equipment when not is use

- consult the dealer or an experienced radio/TV technician for help NOTE: It is recommended that wherever possible shielded interface cables are used.

The product is potentially susceptible to certain EMC phenomena. To mitigate against them it is recommended that the following measures be undertaken;

- The user is advised that mobile phones should not be used within 10m of the product when in use.

- The user is advised to take ESD precautions when handling the equipment.

The Renesas Starter Kit does not represent an ideal reference design for an end product and does not fulfil the regulatory standards for an end product.

## Table of Contents

| Chapter 1. Preface                                 | 5  |

|----------------------------------------------------|----|

| Chapter 2. Purpose                                 | 6  |

| Chapter 3. Power Supply                            | 7  |

| 3.1. Requirements                                  | 7  |

| 3.2. Power up Behaviour                            | 7  |

| Chapter 4. Board Layout                            | 8  |

| 4.1. Component Layout                              | 8  |

| 4.2. Board Dimensions                              | 9  |

| Chapter 5. Block Diagram                           | 10 |

| Chapter 6. User Circuitry                          | 12 |

| 6.1. Switches                                      | 12 |

| 6.2. LEDs                                          | 12 |

| 6.3. Serial port                                   | 12 |

| 6.4. USB                                           | 13 |

| 6.5. Ethernet                                      | 14 |

| 6.5.1. Ethernet MAC Address                        | 14 |

| 6.6. Debug LCD Module                              | 14 |

| 6.7. Graphic Colour TFT LCD Module                 | 15 |

| 6.8. Serial Sound Interface (SSI)                  | 17 |

| 6.9. Video Stream Interface                        | 18 |

| 6.10. Option Links                                 | 19 |

| 6.11. Switch Settings                              | 22 |

| 6.12. Oscillator Sources                           | 24 |

| 6.13. Reset Circuit                                | 24 |

| Chapter 7. Modes                                   | 25 |

| Chapter 8. Programming Methods                     | 26 |

| 8.1. H-UDI Header for E10A                         | 26 |

| Chapter 9. Headers                                 | 27 |

| 9.1. Microcontroller Headers                       | 27 |

| 9.2. Application Headers                           | 33 |

| Chapter 10. Code Development                       | 37 |

| 10.1. Overview                                     | 37 |

| 10.2. Compiler Restrictions                        | 37 |

| 10.3. Breakpoint Support                           | 37 |

| 10.4. Memory Map                                   |    |

| 10.5. CPLD                                         |    |

| 10.5.1. Local TFT Bus Clock                        |    |

| 10.5.2. Synchronise local TFT bus to CPU bus clock |    |

| 10.5.3. External buffer activation control. |    |

|---------------------------------------------|----|

| 10.5.4. Chip Select 5 Area allocation       | 40 |

| Chapter 11. Component Placement             | 41 |

| Chapter 12. CPLD Code Reference             | 43 |

| 12.1. CPLD Device Pinout                    | 44 |

| Chapter 13. Additional Information          | 58 |

## Chapter 1. Preface

#### Cautions

This document may be, wholly or partially, subject to change without notice.

All rights reserved. Duplication of this document, either in whole or part is prohibited without the written permission of Renesas Technology Europe Limited.

#### Trademarks

All brand or product names used in this manual are trademarks or registered trademarks of their respective companies or organisations.

#### Copyright

© 2008 Renesas Technology Europe Ltd. All rights reserved.

© 2008 Renesas Technology Corporation. All rights reserved.

© 2008 Renesas Solutions Corporation. All rights reserved.

Website: <u>http://www.renesas.com/</u>

#### Glossary

| CPLD     | CMOS Programmable Logic Device     | PC   | Program Counter              |

|----------|------------------------------------|------|------------------------------|

| CPU      | Central Processing Unit            | RSK+ | Renesas Starter Kit+         |

| E10A-FSK | On-chip debugger module            | SSI  | Serial sound interface       |

| HEW      | High-performance Embedded Workshop | STI  | Stream interface             |

| LCD      | Liquid crystal Display             | USB  | Universal Serial Bus         |

| LED      | Light Emitting Diode               | RAM  | Random Access memory         |

| ROM      | Read only memory                   | TFT  | Thin film transistor Display |

## Chapter 2.Purpose

This RSK is an evaluation tool for Renesas microcontrollers.

This manual describes the technical details of the RSK hardware. The Quick Start Guide and Tutorial Manual provide details of the software installation and debugging environment.

Features include:

- Renesas Microcontroller Programming.

- User Code Debugging.

- User Circuitry such as Buttons, Switches and LEDs.

- User or Example Application.

- Sample peripheral device initialisation code.

The RSK2+ board contains all the circuitry required for microcontroller operation.

## Chapter 3. Power Supply

### 3.1. Requirements

This RSK2+ operates from an external 12V (centre positive) power supply unit.

A diode provides reverse polarity protection only if a current limiting power supply is used.

All RSK2+ boards are supplied with an E10A debugger.

All RSK2+ boards have an optional centre positive supply connector using a 2.0mm barrel power jack. Following table describes about jumper settings for power supply section. Default settings are in BOLD.

|           | Option Link Settings              |                                |                                 |          |  |

|-----------|-----------------------------------|--------------------------------|---------------------------------|----------|--|

| Reference | Reference Function Fitted Removed |                                |                                 |          |  |

| 5V_SEL_1  | Power supply                      | Enables 5V supply to the board | Disables 5V supply to the board | 5V_SEL_2 |  |

|           | configuration                     |                                | Enables 12V supply connection   |          |  |

|           |                                   |                                | to the board                    |          |  |

| 5V_SEL_2  | Power supply                      | Enables 5V supply to the board | Disables 5V supply to the       | 5V_SEL_1 |  |

|           | Configuration                     |                                | board. Enables 12V supply       |          |  |

|           |                                   |                                | connection to the board.        |          |  |

Table 3-3-1: Jumper settings-Power supply

#### Warning

The RSK2+ is neither under nor over voltage protected. Use a centre positive supply for this board.

### 3.2. Power up Behaviour

When the RSK is purchased the RSK2+ board has the 'Release' or stand alone code from the example tutorial code pre-programmed into the Renesas microcontroller. On powering up the board the user LEDs will start to flash.

## Chapter 4. Board Layout

### 4.1. Component Layout

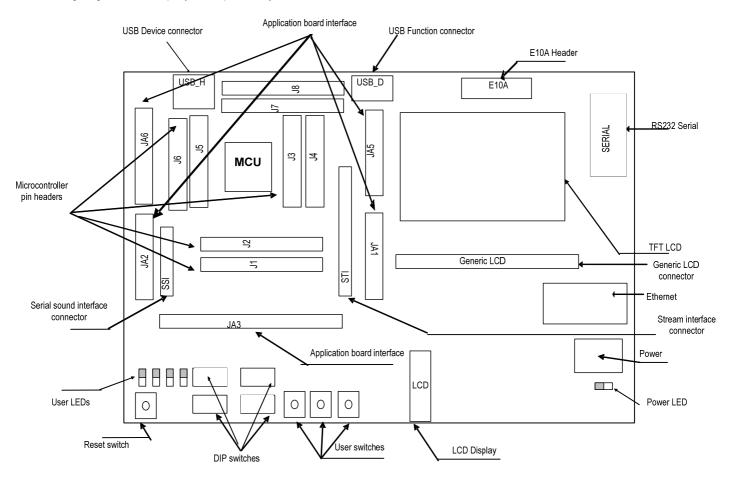

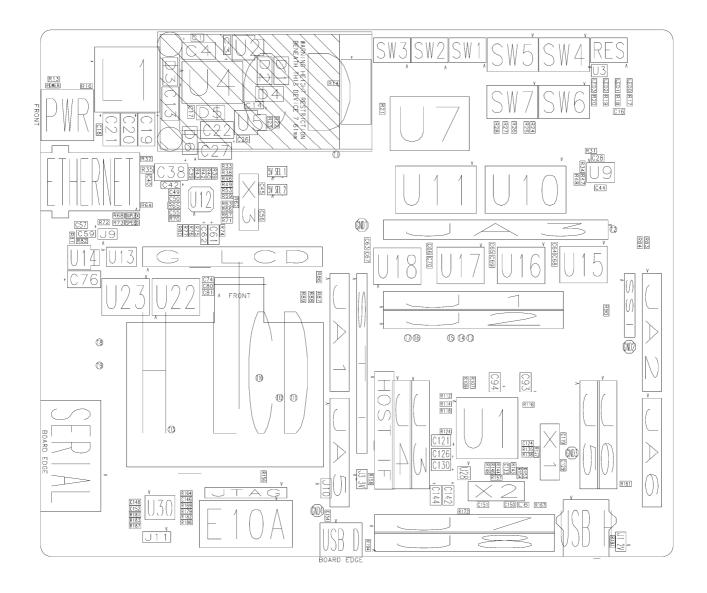

The following diagram shows top layer component layout of the board.

Figure 4-1: Board Layout

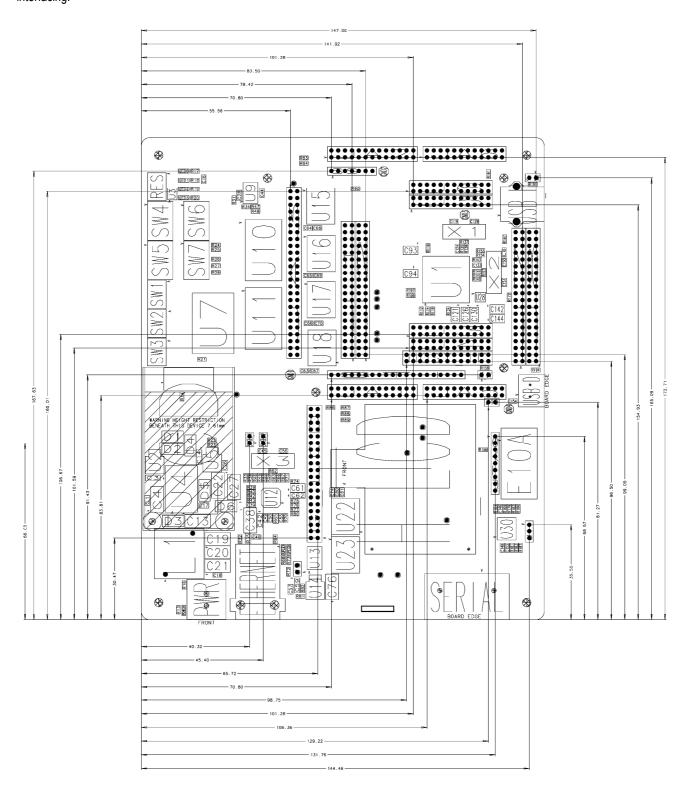

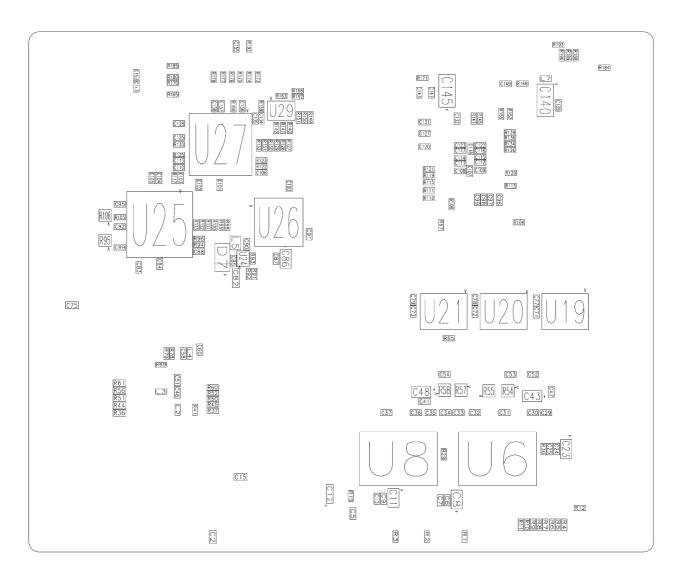

### 4.2. Board Dimensions

The following diagram gives the board dimensions and connector positions. All through hole connectors are on a common 0.1" grid for easy interfacing.

Figure 4-2: Board Dimensions

## Chapter 5. Block Diagram

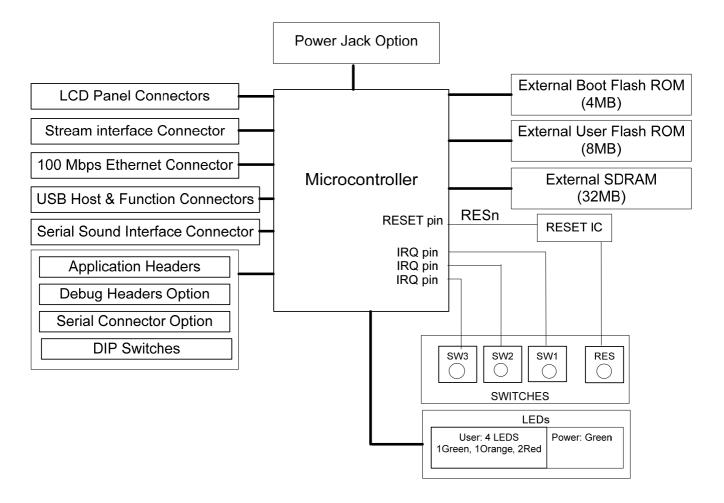

Figure 5-1 shows the CPU board components and their connectivity.

Figure 5-1: Block Diagram

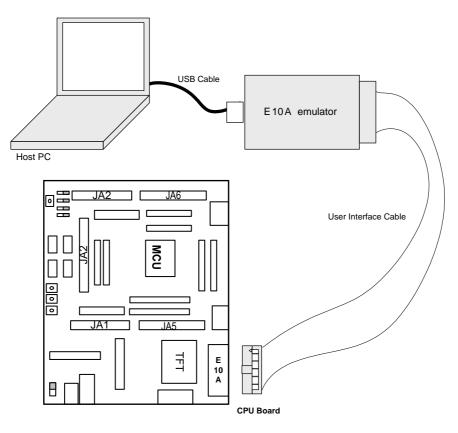

Figure 5-2 shows the E10A connections to the RSK2+.

Figure 5-2: RSK2+ E10A Connections

## Chapter 6. User Circuitry

### 6.1. User Switches

There are four user switches located on the CPU board. The function of each button and its connection are shown in Table 6-1 Switch Functions

| Switch | Function                                                                         | Microcontroller |

|--------|----------------------------------------------------------------------------------|-----------------|

| RES    | When pressed, the RSK2+ microcontroller is reset.                                | RESn, Pin W18   |

| SW1*   | Connects to an IRQ input for user controls.                                      | IRQ4n, Pin N1   |

|        | Note: to connect this button to the CPU please check that dip-switch SW5.1 is in | (Port D pin 4)  |

|        | the 'On' position (for details refer to schematic).                              |                 |

| SW2*   | Connects to an IRQ line for user controls.                                       | IRQ5n, Pin N2   |

|        | Note: to connect this button to the CPU please check that dip-switch SW5.3 is in | (Port D, pin 5) |

|        | the 'On' position (for details refer to schematic).                              |                 |

| SW3*   | Connects to an IRQ line for user controls.                                       | IRQ6n, Pin N3   |

|        | Note: to connect this button to the CPU please check that dip-switch SW5.5 is in | (Port D, pin 6) |

|        | the 'On' position (for details refer to schematic).                              |                 |

#### Table 6-1 Switch Functions

\*Refer to schematic for detailed connectivity information.

### 6.2. LEDs

There are seven LEDs on the RSK2+ board. The green 'POWER' LED lights when the board is powered. The four user LEDs are connected to an IO port and will light when their corresponding port pin is set low. Two green LEDs (placed near Ethernet PHY LAN8700i device) light when Ethernet connection is established, for details refer to Chapter 6.5

Table 6-2, below, shows the User LED pin references and their corresponding microcontroller port pin connections.

| LED Reference<br>(As shown on silkscreen) | Colour | Microcontroller Port Pin | Microcontroller<br>Pin Number |

|-------------------------------------------|--------|--------------------------|-------------------------------|

| LED0                                      | Green  | Port E4                  | Y13                           |

| LED1                                      | Orange | Port E5                  | W13                           |

| LED2                                      | Red    | Port E10                 | W15                           |

| LED3                                      | Red    | Port E11                 | W16                           |

Table 6-2 LED Ports

### 6.3.Serial port

Serial port SCIF2 is connected to the standard on-board RS232 header (Male). Serial port SCIF1 can optionally be connected to the same RS232 header, for details please refer to schematic. Please use standard serial RS232 null-modem cable to connect RSK2+ board to a PC.

The default serial port connections are listed in Table 6-3.

| Description | Function            | Microcontroller<br>Port Pin | Fit for RS232 | Default State |

|-------------|---------------------|-----------------------------|---------------|---------------|

| SCI1 Rx     | Spare Serial Port   | W14                         | R187          | Not fitted    |

| SCI1 Tx     | Spare Serial Port   | V14                         | R186          | Not Fitted    |

| SCI2 Rx     | Default serial port | Y15                         | R169          | Fitted        |

| SCI2 Tx     | Default serial port | Y16                         | R180          | Fitted        |

#### Table 6-3 Serial Port settings

The SCI1 port pins are also available on JA2 header. The SCI2 port pins are available on JA6 header. For details please refer to schematic.

### 6.4. USB

The USB module can be used either for USB host or function (device) modes. For the USB host mode the on-board 'USB\_H' connector must be used. For the USB function mode please use on-board 'USB\_D' connector.

| Table 6-4 contains details of the signal descriptions and pin connections. |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

| Description | Function                             | Microcontroller<br>Pin Number | Header Pins   |

|-------------|--------------------------------------|-------------------------------|---------------|

| VBUS        | Function mode:                       | W9                            | J8-17         |

|             | External USB connection monitor pin. |                               |               |

|             | Host mode:                           |                               |               |

|             | On-board USB power supply pin.       |                               |               |

| USB_D+      | USB data I/O pin                     | Y9                            | Not available |

| USB_D-      | USB data I/O pin                     | Y8                            | Not available |

| USB_X1      | USB clock pin                        | W12                           | J8-23*        |

| USB_X2      | USB clock pin                        | Y12                           | J8-24*        |

| REFIN       | Reference input                      | Y11                           | -             |

#### Table 6-4 USB module settings

\*SW4.1 and SW4.3 must be in the 'On' position while SW4.2 in OFF position for USB\_H mode. SW4.1 and SW4.3 must be in the 'OFF' position while SW4.2 in ON position for USB\_D (function) mode. For details please refer to Table 6-16.

The host power is supplied by a controlled 500mA MOSFET switch with overload protection. IRQ7n is connected to this device to provide overload sensing for devices connected to the host USB port. The device is self resetting when the overload is removed.

When this board is connected as a function device the VBUS signal is connected to a logic device input. To protect this device from having a voltage applied when the main power is turned off on the PCB a diode is fitted in the power supply. This will try to power the board from the connected host device. It is likely that this will shut down the connected host unless it is in high power mode. Please ensure that when developing USB function applications that the USB cable is removed when removing power form this product. Operation is not expected when the product is powered from the function USB port.

The single USB channel is split between the Host and Function connectors using a USB Mux Switch. Care is required when routing Hi-Speed USB signals on your applications. On switching SW4-3 the USB signals are routed to the other connector and disconnected form the current selection.

### 6.5.Ethernet

The Ethernet module conforms to the Ethernet or IEEE802.3 media access control (MAC) standard. Ethernet controller is connected to the direct memory access controller for Ethernet controller (E-DMAC) and carries out high-speed data transfer to and from the memory. In addition the Ethernet controller is connected to on-board SMSC LAN8700i physical layer (PHY) chip enabling it to perform transmission and reception of Ethernet frames. The hardware address of the LAN8700i is predefined as '0x1F'.

There are two Ethernet LEDs on the RSK2+ board and two LEDs on the on-board Ethernet RJ-45 connector. The on-board green SPEED LED lights when 100 Mbit connection is established between the PHY device and any other connected Ethernet device. The green DUPLEX LED lights when Full-Duplex connection is established between the PHY device and any other connected Ethernet device. The embedded Ethernet connector green LED lights when there is a link with the other devices. The yellow LED lights when there is a network activity.

| LED Reference<br>(As shown on silkscreen) | Colour | LAN8700i Port Pin | LAN8700i Pin<br>Number |

|-------------------------------------------|--------|-------------------|------------------------|

| SPEED                                     | Green  | SPEED100_PHYAD0   | 9                      |

| DUPLEX                                    | Green  | FDUPLEX_PHYAD3    | 12                     |

| Ethernet connector: Yellow LED            | Yellow | ACTIVITY_PHYAD2   | 11                     |

| Ethernet connector: Green LED             | Green  | LINK_PHYAD1       | 10                     |

Table 6-5 contains details of the signal descriptions and pin connections.

Table 6-5 Ethernet module settings

#### 6.5.1. Ethernet MAC Address

This board contains an SPI EEPROM device (U29). This device has been pre-programmed with an individual MAC address for the board. The first six locations in the device contain the MAC address in hexadecimal numbers starting with the most significant byte. The rest of this EEPROM device is available for customer use. However care must be taken to store the existing value in the device before it is erased.

### 6.6. Debug LCD Module

A debug LCD module is embedded on the RSK2+ board. The debug LCD module uses a 4 bit interface to reduce the CPU pin allocation. The contrast control is set by a resistor on the supplied display module. The LCD module must be connected to the CPU pins by turning ON SW6 dip-switches: 7 and 9. SW6 switches 8 and 10 must be turned off. For more details please refer to schematic.

Table 6-6 shows the LCD pin allocation and CPU signal names used to handle the LCD.

|     | LCD                       |                       |     |                                        |     |  |

|-----|---------------------------|-----------------------|-----|----------------------------------------|-----|--|

| LCD | LCD pin name / CPU port   | CPU pin               | LCD | LCD pin name / CPU port                | CPU |  |

| Pin |                           |                       | Pin |                                        | pin |  |

| 1   | Ground                    | Ground                | 2   | 5V Only                                |     |  |

| 3   | No Connection             |                       | 4   | DLCDRS / PA24                          | D2  |  |

| 5   | R/W (Wired to Write only) | Pulled down to Ground | 6   | DLCDE + 100k pull down to ground / PB4 | A3  |  |

| 7   | No Connection             |                       | 8   | No connection                          |     |  |

| 9   | No Connection             |                       | 10  | No connection                          |     |  |

| 11  | DLCDD4 / PD0DLCD4         | R3                    | 12  | DLCDD5 / PD2                           | P1  |  |

| 13  | DLCDD6 / PD2DLCD6         | P2                    | 14  | DLCDD7 / PD3                           | P3  |  |

#### Table 6-6 Debug LCD Module Connections

The Debug LCD module can only be used when A24 and DACK1 are not used.

### 6.7. Graphic Colour TFT LCD Module.

The RSK2+ board is equipped with a SSD1906R TFT LCD module controller and two headers for TFT LCD modules. The SSD1906R controller has 256K Embedded Display SRAM and can support colour and monochrome TFT displays. TFT modules can be inserted in the H\_LCD connector (for the Hitachi LCD modules) or G\_LCD connector (for other TFT modules). An adaptor board may be required for other TFT modules.

The TFT controller fitted can support driving panels up to 18 bits in colour depth. When using panels of 18 bit depth with 16 bit data it is necessary to connect Red0 and Blue0 to ground. To support these panels we have provided jumper J9 which will connect these signals to Logic 0 when fitted.

Connections are provided to support an alternate TFT LCD driver IC (Epson S1D13A04) these connections are not verified and information is provided for reference only. Customers may use this alternate device at their own risk.

By default the on-board backlight voltage generator (U24) is enabled and it is configured to drive a string of up to 6 series LEDs with a current of 16.2mA. If the User needs to dim a LCD backlight or disable it, R92 resistor may be fitted. For an appropriate value of the resistor please refer to datasheet of backlight voltage generator (MAX1599).

The connections for the TFT LCD Modules are listed in Table 6-7 and Table 6-8.

|     | H_LCD (For Hitachi LCD) |            |     |                       |            |

|-----|-------------------------|------------|-----|-----------------------|------------|

| Pin | CPU board Signal Name   | Device Pin | Pin | CPU board Signal Name | Device Pin |

| 1   | GROUND                  |            | 2   | GROUND                |            |

| 3   | GROUND                  |            | 4   | LCD_VCC               |            |

| 5   | LCD_VCC                 |            | 6   | LCD_VCC               |            |

| 7   | BLCD_DATA0              |            | 8   | BLCD_DATA1            |            |

| 9   | BLCD_DATA2              |            | 10  | BLCD_DATA3            |            |

| 11  | BLCD_DATA4              |            | 12  | BLCD_DATA5            |            |

| 13  | BLCD_DATA6              |            | 14  | BLCD_DATA7            |            |

| 15  | BLCD_DATA8              |            | 16  | BLCD_DATA9            |            |

| 17  | BLCD_DATA10             |            | 18  | BLCD_DATA11           |            |

| 19  | BLCD_DATA12             |            | 20  | BLCD_DATA13           |            |

| 21  | BLCD_DATA14             |            | 22  | BLCD_DATA15           |            |

| 23  | BLCD_DATA16             |            | 24  | BLCD_DATA17           |            |

| 25  | BLCD_DOTCLK             |            | 26  | BLCD_HSYNC            |            |

| 27  | BLCD_VSYNC              |            | 28  | BSSCS                 | B4         |

| 29  | BSSCK                   | V15        | 30  | BSSO                  | V14        |

| 31  | RXD1                    | W14        | 32  | BLCD_RESn             | W18        |

| 33  | GROUND                  |            | 34  | VLED +                |            |

| 35  | VLED +                  |            | 36  | VLED -                |            |

| 37  | VLED -                  |            | 38  | GROUND                |            |

| 39  | GROUND                  |            |     |                       |            |

Table 6-7 Hitachi LCD Module Connections

|     | G_LCD (For Generic LCD) |            |     |                       |            |  |

|-----|-------------------------|------------|-----|-----------------------|------------|--|

| Pin | CPU board Signal Name   | Device Pin | Pin | CPU board Signal Name | Device Pin |  |

| 1   | BOARD_5V                |            | 2   | BOARD_5V              |            |  |

| 3   | LCD_VCC                 |            | 4   | LCD_VCC               |            |  |

| 5   | VLED+                   |            | 6   | VLED-                 |            |  |

| 7   | BLCD_DATA1              |            | 8   | BLCD_DATA2            |            |  |

| 9   | BLCD_DATA3              |            | 10  | BLCD_DATA4            |            |  |

| 11  | BLCD_DATA5              |            | 12  | BLCD_DATA6            |            |  |

| 13  | BLCD_DATA7              |            | 14  | BLCD_DATA8            |            |  |

| 15  | BLCD_DATA9              |            | 16  | BLCD_DATA10           |            |  |

| 17  | BLCD_DATA11             |            | 18  | BLCD_DATA13           |            |  |

| 19  | BLCD_DATA14             |            | 20  | BLCD_DATA15           |            |  |

| 21  | BLCD_DATA16             |            | 22  | BLCD_DATA17           |            |  |

| 23  | BLCD_DON                |            | 24  | BLCD_HSYNC            |            |  |

| 25  | BLCD_DOTCLK             |            | 26  | BLCD_MDISP            |            |  |

| 27  | BLCD_VSYNC              |            | 28  | BCLD_CLK (LCD CLK)    |            |  |

| 29  | BSSCK                   | V15        | 30  | RXD1                  | W14        |  |

| 31  | BSSO                    |            | 32  | BSSCS                 | B4         |  |

| 33  | BLCD_RESn               | W18        | 34  | GROUND                |            |  |

| 35  | BLCD_VCPWC              |            | 36  | BLCD_VEPWC            | 145        |  |

| 37  | GROUND                  |            | 38  | GROUND                |            |  |

| 39  | GROUND                  |            | 40  | GROUND                |            |  |

### 6.8. Serial Sound Interface (SSI).

The RSK2+ board is equipped with Serial Sound Interface (SSI). The SSI is a module designed to send or receive an audio data stream with various devices. The 'SSI' header is accessible on the RSK2+ board. Please see the microcontroller hardware manual for more details.

|     | J2               |            |     |                  |            |  |

|-----|------------------|------------|-----|------------------|------------|--|

| Pin | Circuit Net Name | Device Pin | Pin | Circuit Net Name | Device Pin |  |

| 1   | Board_5V         |            | 2   | Board_VCC        |            |  |

| 3   | SSI_SCK1         | W17        | 4   | SSI_WS1          | V12        |  |

| 5   | SSI_DATA1        | V13        | 6   | AUDIOCLK         | V16        |  |

| 7   | GROUND           |            |     |                  |            |  |

Table 6-9 Serial sound interface Connections

### 6.9. Video Stream Interface

The RSK2+ board is equipped with Video Stream Interface header 'STI'. For details please refer to the SH/7670 hardware manual.

|     | STI connector         |            |     |                       |            |  |

|-----|-----------------------|------------|-----|-----------------------|------------|--|

| Pin | CPU board Signal Name | Device Pin | Pin | CPU board Signal Name | Device Pin |  |

| 1   | ST0_CLKIN             | R19        | 2   | ST_CLKOUT             | Y17        |  |

| 3   | ST0_D0                | N20        | 4   | ST0_D2                | M18        |  |

| 5   | ST0_D4                | M20        | 6   | ST0_D6                | L19        |  |

| 7   | NC                    |            | 8   | GROUND                |            |  |

| 9   | GROUND                |            | 10  | NC                    |            |  |

| 11  | ST0_D7                | L20        | 12  | ST0_D5                | L18        |  |

| 13  | ST0_D3                | M19        | 14  | ST0_D1                | N18        |  |

| 15  | ST0_SYC               | N19        | 16  | ST0_VLD               | P20        |  |

| 17  | ST0_PWM               | P18        | 18  | ST0_REQ               | P19        |  |

| 19  | ST0_VCO_CLKIN         | R20        | 20  | GROUND                |            |  |

Table 6-10 Video stream interface connections

### 6.10. Option Links

Table 6-11 below describes the function of the option links contained on this RSK2+ board and associated with Serial Port Configuration. The default configuration is indicated by BOLD text.

|           | Serial Port Option Link Settings |                                    |                                           |             |  |  |

|-----------|----------------------------------|------------------------------------|-------------------------------------------|-------------|--|--|

| Reference | Function                         | Fitted                             | Not fitted                                | Related To  |  |  |

| R165      | Serial Port                      | Disables RS232 Serial              | Enables RS232 Serial                      |             |  |  |

|           | configuration                    | Transceiver                        | sceiver Transceiver                       |             |  |  |

| R169      | Serial Port                      | Connects serial port SCIF2 (Rx) to | Disconnects serial port SCIF2             | R179, R180, |  |  |

|           | Configuration                    | serial receiver pin.               | (Rx) from serial receiver pin.            | R170        |  |  |

| R170      | Serial Port                      | Connects serial port SCIF2 (Rx) to | Disconnects serial port SCIF2             | R179, R180, |  |  |

|           | Configuration                    | JA6 pins.                          | (Rx) from JA6 pins.                       | R169        |  |  |

| R180      | Serial Port                      | Connects serial port SCIF2 (Tx) to | Disconnects serial port SCIF2 (Tx)        | R179, R169, |  |  |

|           | Configuration                    | serial transmitter pin.            | from serial transmitter pin.              | R170        |  |  |

| R179      | Serial Port                      | Connects serial port SCIF2 (Tx) to | Disconnects serial port SCIF2 R169, R180, |             |  |  |

|           | Configuration                    | JA6 pins.                          | (Tx) port from JA6 pins.                  | R170        |  |  |

| R181      | Serial Port                      | Connects serial port SCIF1 (Tx) to | Disconnects port SCIF1 (Tx)               | R186        |  |  |

|           | Configuration                    | D-type connector secondary         | from D-type connector                     |             |  |  |

|           |                                  | channel.                           | secondary channel.                        |             |  |  |

| R183      | Serial Port                      | Connects serial port SCIF1 (Rx) to | Disconnects port SCIF1 (Rx)               | R187        |  |  |

|           | Configuration                    | D-type connector secondary         | from D-type connector                     |             |  |  |

|           |                                  | channel.                           | secondary channel.                        |             |  |  |

| R186      | Serial Port                      | Connects serial port SCIF1 (Tx) to | Disconnects serial port SCIF1 R181        |             |  |  |

|           | Configuration                    | secondary serial transmitter pin.  | (Tx) from secondary serial                |             |  |  |

|           |                                  |                                    | transmitter pin.                          |             |  |  |

| R187      | Serial Port                      | Connects serial port SCIF1 (Rx) to | Disconnects serial port SCIF1             | R183        |  |  |

|           | Configuration                    | secondary serial receiver pin.     | (Rx) from secondary serial                |             |  |  |

|           |                                  |                                    | receiver pin.                             |             |  |  |

Table 6-11 Serial port configuration links.

Table 6-12 below describes the function of the option links associated with power source. The default configuration is indicated by BOLD text.

|           | Power Supply Option Link Settings                                                |                                        |                                 |            |  |  |  |

|-----------|----------------------------------------------------------------------------------|----------------------------------------|---------------------------------|------------|--|--|--|

| Reference | ference Function Fitted Not fitted                                               |                                        | Not fitted                      | Related To |  |  |  |

| 5V_SEL_1  | RSK2+ board                                                                      | Both jumper blocks are to be fitted to | Both jumper blocks are to be    | R16, R22,  |  |  |  |

|           | power supply                                                                     | override the input regulator and allow | removed to allow an external    | 5V_SEL_2   |  |  |  |

| 5V_SEL_2  | External power                                                                   | an external 5V supply to power the     | 7-12V supply to power the       | R16, R22,  |  |  |  |

|           | supply                                                                           | board.                                 | board.                          | 5V_SEL_1   |  |  |  |

| R191      | Power source                                                                     | Normal operation                       | J1_2 provides the option to     |            |  |  |  |

|           |                                                                                  |                                        | measure the current. *WARNING*  |            |  |  |  |

| R158      | Power source                                                                     | Normal operation                       | J3_3 provides the option to     |            |  |  |  |

|           |                                                                                  |                                        | measure the current. *WARNING*  |            |  |  |  |

| R86       | External power Routes JA1-3 pin to on-board 3V3. Disable 3V3 output to JA1-3 pin |                                        | Disable 3V3 output to JA1-3 pin | R171,R172  |  |  |  |

|           | supply                                                                           |                                        |                                 |            |  |  |  |

| R22       | External power                                                                   | Routes JA1-1 pin to on-board 5V.       | Disable 5V output to JA1-1 pin  | 5V_SEL_1,  |  |  |  |

|           | supply                                                                           |                                        |                                 | 5V_SEL_2   |  |  |  |

| R92       | LCD backlight                                                                    | Disables or dims TFT LCD backlight     | Enables 16.2mA output for TFT   |            |  |  |  |

|           |                                                                                  |                                        | LCD backlight                   |            |  |  |  |

Table 6-12 Power configuration links.

\*WARNING: All power connections with provision for current measurement must remain connected while the power is on or damage to the connected devices is highly likely. Table 6-13 below describes the function of the option links associated with clock configuration. The default configuration is indicated by BOLD text.

|           | Clock Option Link Settings |                                                               |                               |             |  |  |

|-----------|----------------------------|---------------------------------------------------------------|-------------------------------|-------------|--|--|

| Reference | Function                   | Fitted                                                        | Not fitted                    | Related To  |  |  |

| R62       | PHY clock source           | Load resistor for a crystal                                   | Not fitted                    |             |  |  |

| R63       | PHY clock source           | Connects on-board oscillator for Can be replaced with damping |                               |             |  |  |

|           |                            | the PHY device                                                | resistor if required.         |             |  |  |

| R157      | USB clock source           | Load resistor for a crystal                                   | Not fitted                    |             |  |  |

| R146      | USB clock source           | On-board oscillator is used                                   | External clock source is used | R144, R145, |  |  |

|           |                            |                                                               |                               | R147        |  |  |

| R147      | USB External clock         | External clock source is used                                 | On-board Clock Source is used | R144, R145, |  |  |

|           | source                     |                                                               |                               | R146        |  |  |

| R144      | USB clock source           | On-board oscillator is used                                   | External clock source is used | R146, R145, |  |  |

|           |                            |                                                               |                               | R147        |  |  |

| R145      | USB External clock         | External clock source is used                                 | On-board Clock Source is used | R144, R146, |  |  |

|           | source                     |                                                               |                               | R147        |  |  |

| R137      | CPU clock source           | Load resistor for a crystal                                   | Not fitted                    |             |  |  |

| R139      | CPU External clock         | External clock source is used                                 | On-board Clock Source is used | R135, R136, |  |  |

|           | source                     |                                                               |                               | R138        |  |  |

| R138      | CPU clock source           | On-board oscillator is used                                   | External clock source is used | R135, R136, |  |  |

|           |                            |                                                               |                               | R139        |  |  |

| R136      | CPU External clock         | External clock source is used                                 | On-board Clock Source is used | R135, R139, |  |  |

|           | source                     |                                                               |                               | R138        |  |  |

| R135      | CPU clock source           | On-board oscillator is used                                   | External clock source is used | R139, R136, |  |  |

|           |                            |                                                               |                               | R138        |  |  |

#### Table 6-13 Clock configuration links.

Table 6-14 below describes the function of the option links associated with USB. The default configuration is indicated by BOLD text.

|           | Option Link Settings                  |                                |                                |            |  |  |

|-----------|---------------------------------------|--------------------------------|--------------------------------|------------|--|--|

| Reference | Function                              | Fitted Not fitted              |                                | Related To |  |  |

| R184      | USB Host                              | USB Host connector shield is   | USB Host connector shield is   | -          |  |  |

|           | connector shield                      | grounded                       | unconnected                    |            |  |  |

| R194      | USB Device                            | USB Device connector shield is | USB Device connector shield is | -          |  |  |

|           | connector shield grounded unconnected |                                |                                |            |  |  |

Table 6-14 USB links.

### 6.11.DIP Switch Settings

| DIP Switch | State | DIP Switch | State | DIP    | State | DIP    | State |

|------------|-------|------------|-------|--------|-------|--------|-------|

| SW4        |       | SW5        |       | Switch |       | Switch |       |

|            |       |            |       | SW6    |       | SW7    |       |

| 1          | ON    | 1          | OFF   | 1      | OFF   | 1      | OFF   |

| 2          | OFF   | 2          | ON    | 2      | ON    | 2      | ON    |

| 3          | ON    | 3          | OFF   | 3      | OFF   | 3      | ON    |

| 4          | ON    | 4          | ON    | 4      | ON    | 4      | OFF   |

| 5          | ON    | 5          | OFF   | 5      | OFF   | 5      | ON    |

| 6          | ON    | 6          | ON    | 6      | ON    | 6      | OFF   |

| 7          | ON    | 7          | OFF   | 7      | ON    | 7      | ON    |

| 8          | ON    | 8          | ON    | 8      | OFF   | 8      | OFF   |

| 9          | OFF   | 9          | OFF   | 9      | ON    | 9      | ON    |

| 10         | OFF   | 10         | ON    | 10     | OFF   | 10     | OFF   |

Table 6-15 Default DIP Switch Settings

|    | Switch (SW4)                                 |                                 |                                     |  |  |  |  |

|----|----------------------------------------------|---------------------------------|-------------------------------------|--|--|--|--|

| ID | Function                                     | Action On                       | Action Off                          |  |  |  |  |

| 1  | Selection of USB VBUS Flag                   | USB Host connector connected to | USB Host connector VBUS flag        |  |  |  |  |

|    |                                              | VBUS                            | disconnected                        |  |  |  |  |

| 2  |                                              | USB Function connector          | USB Function connector VBUS flag    |  |  |  |  |

|    |                                              | connected to VBUS               | disconnected                        |  |  |  |  |

| 3  | Select between USB Host and Function         | USB Host connector is selected. | USB Function connector is selected. |  |  |  |  |

|    | Connectors.                                  |                                 |                                     |  |  |  |  |

| 4  | TFT Controller CF4                           | Little Endian bus interface     | Big Endian bus interface            |  |  |  |  |

| 5  | TFT Controller CF6                           | CF6 = 0 *See Table 6-17         | CF6 = 1 *See table Table 6-17       |  |  |  |  |

| 6  | TFT Controller CF7                           | CF7 = 0 *See Table 6-17         | CF7 = 1 *See table Table 6-17       |  |  |  |  |

| 7  | Chip Select 5 (Expansion Header) Selection 0 | CS5_SEL0 = 0 *See Table 10-2    | CS5_SEL0 = 1 * See Table 10-2       |  |  |  |  |

| 8  | Chip Select 5 (Expansion Header) Selection 1 | CS5_SEL1 = 0 *See Table 10-2    | CS5_SEL1 = 1 * See Table 10-2       |  |  |  |  |

| 9  | Flash Protection (Boot Flash)                | Flash protection On             | Flash Protection Off                |  |  |  |  |

| 10 | Flash Protection (User Flash)                | Flash Protection On             | Flash Protection Off                |  |  |  |  |

Table 6-16 SW4 Functions

| CF6 | CF7 | CLKI to BCLK Divide Ratio |

|-----|-----|---------------------------|

| 0   | 0   | 1:1                       |

| 0   | 1   | 2:1                       |

| 1   | 0   | 3:1                       |

| 1   | 1   | 4:1                       |

#### Table 6-17 SW4-5+6 Function

|    | Switch (SW5)                   |                  |                     |  |  |

|----|--------------------------------|------------------|---------------------|--|--|

| ID | Function                       | Action On        | Action Off          |  |  |

| 1  | Multiplexed Pin: ST0D0 and IO0 | ST0_D0 Connected | ST0_D0 Disconnected |  |  |

| 2  |                                | IO0 Connected    | IO0 Disconnected    |  |  |

| 3  | Multiplexed Pin: ST0D1 and IO1 | ST0_D1 Connected | ST0_D1 Disconnected |  |  |

| 4  |                                | IO1 Connected    | IO1 Disconnected    |  |  |

| 5  | Multiplexed Pin: ST0D2 and IO2 | ST0_D2 Connected | ST0_D2 Disconnected |  |  |

| 6  |                                | IO2 Connected    | IO2 Disconnected    |  |  |

| 7  | Multiplexed Pin: ST0D3 and IO3 | ST0_D3 Connected | ST0_D3 Disconnected |  |  |

| 8  |                                | IO3 Connected    | IO3 Disconnected    |  |  |

| 9  | Multiplexed Pin: ST0D4 and IO4 | ST0_D4 Connected | ST0_D4 Disconnected |  |  |

| 10 |                                | IO4 Connected    | IO4 Disconnected    |  |  |

#### Table 6-18 SW5 Functions

|    |                                  | Switch (SW6)     |                     |

|----|----------------------------------|------------------|---------------------|

| ID | Function                         | Action On        | Action Off          |

| 1  | Multiplexed Pin: ST0_D5 and IO5  | ST0_D5 Connected | ST0_D5 Disconnected |

| 2  |                                  | IO5 Connected    | IO5 Disconnected    |

| 3  | Multiplexed Pin: ST0_D6 and IO6  | ST0_D6 Connected | ST0_D6 Disconnected |

| 4  |                                  | IO6 Connected    | IO6 Disconnected    |

| 5  | Multiplexed Pin: ST0_D7 and IO7  | ST0_D7 Connected | ST0_D7 Disconnected |

| 6  |                                  | IO7 Connected    | IO7 Disconnected    |

| 7  | Multiplexed Pin: DLCDE and DACK1 | DLCDE Connected  | DLCDE Disconnected  |

| 8  |                                  | DACK1 Connected  | DACK1 Disconnected  |

| 9  | Multiplexed Pin: DLCDRS and A24  | DLCDRS Connected | DLCDRS Disconnected |

| 10 |                                  | A24 Connected    | A24 Disconnected    |

Table 6-19 SW6 Functions

|    | Switch (SW7)                                                                                 |                                                   |                                                       |  |  |  |  |  |

|----|----------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| ID | Function                                                                                     | Action On                                         | Action Off                                            |  |  |  |  |  |

| 1  | Multiplexed Pin HIFMD and A25. HIFMD is sampled at reset and determines if this is a host or | Pulled high                                       | Disconnected                                          |  |  |  |  |  |

| 2  | slave device. If both switches are off operation is not guaranteed.                          | Pulled Low                                        | Disconnected                                          |  |  |  |  |  |

| 3  | Selection of CS5C                                                                            | CS5C is connected to signal<br>CS5Cn_CS5Dn on JA3 | CS5C is not connected to signal<br>CS5Cn_CS5Dn on JA3 |  |  |  |  |  |

| 4  | Selection of CS5D                                                                            | CS5C is connected to signal<br>CS5Cn_CS5Dn on JA3 | CS5C is not connected to signal<br>CS5Cn_CS5Dn on JA3 |  |  |  |  |  |

| 5  | Multiplexed Pin: WAITn and SDA                                                               | WAITn Connected                                   | WAITn Disconnected                                    |  |  |  |  |  |

| 6  |                                                                                              | SDA Connected                                     | SDA Disconnected                                      |  |  |  |  |  |

| 7  | Multiplexed Pin: CS5n and TEND1                                                              | CS5n Connected                                    | CS5n Disconnected                                     |  |  |  |  |  |

| 8  |                                                                                              | TEND1 Connected                                   | TEND1 Disconnected                                    |  |  |  |  |  |

| 9  | Multiplexed Pin: CS6n and DREQ1                                                              | CS6n Connected                                    | CD6n Disconnected                                     |  |  |  |  |  |

| 10 |                                                                                              | DREQ1 Connected                                   | DREQ1 Disconnected                                    |  |  |  |  |  |

#### Table 6-20 SW7 Functions

### 6.12. Oscillator Sources

Crystal oscillators are fitted on the RSK2+ and used to supply the main clock input to the Renesas microcontroller. Please see the table below for details of the oscillators that are fitted and alternative footprints provided on this RSK2+:

| Component        |        |

|------------------|--------|

| Crystal (X1),    | 25 MHz |

| Main clock.      |        |

| Crystal (X2),    | 48 MHz |

| USB module.      |        |

| Crystal (X3),    | 25 MHz |

| Ethernet module. |        |

Table 6-21 Oscillators / Resonators

### 6.13.Reset Circuit

The CPU Board includes µP Supervisory Circuit with Manual Reset ability. The reset timeout period is set as 15 ms.

Please check the reset requirements carefully to ensure the reset circuit on the user's board meets all the reset timing requirements.

## Chapter 7. Modes

This CPU incorporates a host interface (HIF) for use in high-speed transfer of data between external devices which cannot utilize the system bus. The HIF allows external devices to read from and write to 4 Kbytes (2 Kbytes x 2 banks) of the on-chip RAM exclusively for HIF use (HIFRAM) within this CPU, in 32-bit units.

Using HIFRAM, the HIF also supports HIF boot mode allowing this CPU to be booted. In HIF boot mode, this CPU can be booted from HIFRAM by an external device storing the instruction code in HIFRAM. The HIF's 'HOST Interface' header is accessible on the RSK2+ board.

For the details please refer to the SH/7670 Group Hardware Manual.

## Chapter 8. Programming Methods

The RSK2+SH7670 board can be programmed using E10A-FSK supplied with the kit. Following header is provided to download and debug the user code – H-UDI.

### 8.1. H-UDI Header for E10A

This is a 14 pin header used to download and debug the user program. This header provides H-UDI interface for user debugging. Limited Event conditions in ROM and unlimited Breakpoints in RAM are supported. The AUD trace function is not supported on this interface.

## Chapter 9. Headers

### 9.1. Microcontroller Headers

Table 9-1 to Table 9-8 show the microcontroller pin headers and their corresponding microcontroller connections. The header pins connect directly to the microcontroller pin unless otherwise stated.

|     | J1               |        |     |                  |        |  |  |  |

|-----|------------------|--------|-----|------------------|--------|--|--|--|

| Pin | Circuit Net Name | Device | Pin | Circuit Net Name | Device |  |  |  |

|     |                  | Pin    |     |                  | Pin    |  |  |  |

| 1   | A(17)            | A1     | 2   | A(19)            | B1     |  |  |  |

| 3   | A(0)             | A2     | 4   | A(18)            | B2     |  |  |  |

| 5   | DLCDE_DACK1      | A3     | 6   | CS5n_TEND1       | B3     |  |  |  |

| 7   | WAITn_SDA        | A4     | 8   | IOCS             | B4     |  |  |  |

| 9   | CS4n             | A5     | 10  | RDn              | B5     |  |  |  |

| 11  | DQM1             | A6     | 12  | BSn              | B6     |  |  |  |

| 13  | D(9)             | A7     | 14  | D(8)             | B7     |  |  |  |

| 15  | D(12)            | A8     | 16  | D(10)            | B8     |  |  |  |

| 17  | D(15)            | A9     | 18  | D(14)            | B9     |  |  |  |

| 19  | D(5)             | A10    | 20  | D(6)             | B10    |  |  |  |

| 21  | D(2)             | A11    | 22  | D(3)             | B11    |  |  |  |

| 23  | A(16)            | A12    | 24  | D(0)             | B12    |  |  |  |

| 25  | A(13)            | A13    | 26  | A(14)            | B13    |  |  |  |

| 27  | A(10)            | A14    | 28  | A(11)            | B14    |  |  |  |

| 29  | A(7)             | A15    | 30  | A(8)             | B15    |  |  |  |

| 31  | A(4)             | A16    | 32  | A(5)             | B16    |  |  |  |

| 33  | A(1)             | A17    | 34  | A(2)             | B17    |  |  |  |

| 35  | SDRASn           | A18    | 36  | CS3n             | B18    |  |  |  |

| 37  | SDCASn           | A19    | 38  | GROUND           | B19    |  |  |  |

| 39  | GROUND           | A20    | 40  | SDCKE            | B20    |  |  |  |

Table 9-1: J1

|     | J2               |               |     |                  |               |  |  |  |

|-----|------------------|---------------|-----|------------------|---------------|--|--|--|

| Pin | Circuit Net Name | Device<br>Pin | Pin | Circuit Net Name | Device<br>Pin |  |  |  |

| 1   | A(22)            | C1            | 2   | HIFMD_A25        | D1            |  |  |  |

| 3   | A(21)            | C2            | 4   | DLCDRS_A24       | D2            |  |  |  |

| 5   | A(20)            | C3            | 6   | A(23)            | D3            |  |  |  |

| 7   | CS6n_DREQ1       | C4            | 8   | GROUND           | D4            |  |  |  |

| 9   | SCL              | C5            | 10  | GROUND           | D5            |  |  |  |

| 11  | CS0n             | C6            | 12  | UC_VCCQ          | D6            |  |  |  |

| 13  | DQM0             | C7            | 14  | UC_VCC           | D7            |  |  |  |

| 15  | D(11)            | C8            | 16  | GROUND           | D8            |  |  |  |

| 17  | D(13)            | C9            | 18  | UC_VCCQ          | D9            |  |  |  |

| 19  | D(7)             | C10           | 20  | UC_VCCQ          | D10           |  |  |  |

| 21  | D(4)             | C11           | 22  | GROUND           | D11           |  |  |  |

| 23  | D(1)             | C12           | 24  | GROUND           | D12           |  |  |  |

| 25  | A(15)            | C13           | 26  | UC_VCC           | D13           |  |  |  |

| 27  | A(12)            | C14           | 28  | GROUND           | D14           |  |  |  |

| 29  | A(9)             | C15           | 30  | UC_VCCQ          | D15           |  |  |  |

| 31  | A(6)             | C16           | 32  | GROUND           | D16           |  |  |  |

| 33  | A(3)             | C17           | 34  | GROUND           | D17           |  |  |  |

| 35  | GROUND           | C18           | 36  | DQM3             | D18           |  |  |  |

| 37  | WEn              | C19           | 38  | DQM2             | D19           |  |  |  |

| 39  | CKIO             | C20           | 40  | D(25)            | D20           |  |  |  |

Table 9-2: J2

|     | J3               |        |     |                  |        |  |  |  |

|-----|------------------|--------|-----|------------------|--------|--|--|--|

| Pin | Circuit Net Name | Device | Pin | Circuit Net Name | Device |  |  |  |

|     |                  | Pin    |     |                  | Pin    |  |  |  |

| 1   | LNKSTA           | E1     | 2   | PIN_E2           | E2     |  |  |  |

| 3   | TX-CLK           | F1     | 4   | MDIO             | F2     |  |  |  |

| 5   | MII_TXD3         | G1     | 6   | TX-ER            | G2     |  |  |  |

| 7   | MII_TXD0         | H1     | 8   | MII_TXD1         | H2     |  |  |  |

| 9   | RX-CLK           | J1     | 10  | COL              | J2     |  |  |  |

| 11  | MII_RXD3         | K1     | 12  | RX-DV            | K2     |  |  |  |

| 13  | MII_RXD0         | L1     | 14  | MII_RXD1         | L2     |  |  |  |

| 15  | NC               | -      | 16  | ASEMDn           | M2     |  |  |  |

| 17  | IRQ4n            | N1     | 18  | IRQ5n            | N2     |  |  |  |

| 19  | DLCDD5           | P1     | 20  | DLCDD6           | P2     |  |  |  |

| 21  | HIF_D14          | R1     | 22  | HIF_D15          | R2     |  |  |  |

| 23  | HIF_D11          | T1     | 24  | HIF_D12          | T2     |  |  |  |

Table 9-3: J3

|     | J4               |        |     |                  |        |  |  |

|-----|------------------|--------|-----|------------------|--------|--|--|

| Pin | Circuit Net Name | Device | Pin | Circuit Net Name | Device |  |  |

|     |                  | Pin    |     |                  | Pin    |  |  |

| 1   | PIN_E3           | E3     | 2   | GROUND           | E4     |  |  |

| 3   | MDC              | F3     | 4   | UC_VCCQ          | F4     |  |  |

| 5   | TX-EN            | G3     | 6   | GROUND           | G4     |  |  |

| 7   | MII_TXD2         | H3     | 8   | UC_VCC           | H4     |  |  |

| 9   | CRS              | J3     | 10  | GROUND           | J4     |  |  |

| 11  | RX-ER            | K3     | 12  | UC_VCCQ          | K4     |  |  |

| 13  | MII_RXD2         | L3     | 14  | UC_VCCQ          | L4     |  |  |

| 15  | IRQ7n            | M3     | 16  | GROUND           | M4     |  |  |

| 17  | IRQ6n            | N3     | 18  | GROUND           | N4     |  |  |

| 19  | DLCDD7           | P3     | 20  | UC_VCC           | P4     |  |  |

| 21  | DLCDD4           | R3     | 22  | UC_VCC           | R4     |  |  |

| 23  | HIF_D13          | Т3     | 24  | GROUND           | T4     |  |  |

Table 9-4: J4

|     | J5               |        |     |                  |        |  |  |

|-----|------------------|--------|-----|------------------|--------|--|--|

| Pin | Circuit Net Name | Device | Pin | Circuit Net Name | Device |  |  |

|     |                  | Pin    |     |                  | Pin    |  |  |

| 1   | GROUND           | E17    | 2   | D(24)            | E18    |  |  |

| 3   | UC_VCCQ          | F17    | 4   | D(27)            | F18    |  |  |

| 5   | UC_VCCQ          | G17    | 6   | D(31)            | G18    |  |  |

| 7   | UC_VCCQ          | H17    | 8   | UC_VCCQ          | H18    |  |  |

| 9   | GROUND           | J17    | 10  | GROUND           | J18    |  |  |

| 11  | UC_VCC           | K17    | 12  | GROUND           | K18    |  |  |

| 13  | GROUND           | L17    | 14  | ST0D5_IO5        | L18    |  |  |

| 15  | GROUND           | M17    | 16  | ST0D2_IO2        | M18    |  |  |

| 17  | UC_VCCQ          | N17    | 18  | ST0D1_IO1        | N18    |  |  |

| 19  | GROUND           | P17    | 20  | ST0_PWM          | P18    |  |  |

| 21  | UC_VCC           | R17    | 22  | WDTOVFn          | R18    |  |  |

| 23  | GROUND           | T17    | 24  | GROUND           | T18    |  |  |

Table 9-5: J5

|     | J6               |        |     |                  |        |  |  |

|-----|------------------|--------|-----|------------------|--------|--|--|

| Pin | Circuit Net Name | Device | Pin | Circuit Net Name | Device |  |  |

|     |                  | Pin    |     |                  | Pin    |  |  |

| 1   | D(26)            | E19    | 2   | D(28)            | E20    |  |  |

| 3   | D(29)            | F19    | 4   | D(30)            | F20    |  |  |

| 5   | D(23)            | G19    | 6   | D(22)            | G20    |  |  |

| 7   | D(21)            | H19    | 8   | D(20)            | H20    |  |  |

| 9   | D(19)            | J19    | 10  | D(18)            | J20    |  |  |

| 11  | D(17)            | K19    | 12  | D(16)            | K20    |  |  |

| 13  | ST0D6_IO6        | L19    | 14  | ST0D7_IO7        | L20    |  |  |

| 15  | ST0D3_IO3        | M19    | 16  | ST0D4_IO4        | M20    |  |  |

| 17  | ST0_SYC          | N19    | 18  | ST0D0_IO0        | N20    |  |  |

| 19  | ST0_REQ          | P19    | 20  | ST0_VLD          | P20    |  |  |

| 21  | ST0_CLKIN        | R19    | 22  | ST0_VCO_CLKIN    | R20    |  |  |

| 23  | MD_BW            | T19    | 24  | ASEBRKn          | T20    |  |  |

Table 9-6: J6

|     | J7               |               |     |                  |               |  |  |  |

|-----|------------------|---------------|-----|------------------|---------------|--|--|--|

| Pin | Circuit Net Name | Device<br>Pin | Pin | Circuit Net Name | Device<br>Pin |  |  |  |

| 1   | HIF_D9           | U1            | 2   | HIF_D7           | V1            |  |  |  |

| 3   | HIF_D10          | U2            | 4   | GROUND           | V2            |  |  |  |

| 5   | GROUND           | U3            | 6   | HIF_D4           | V3            |  |  |  |

| 7   | GROUND           | U4            | 8   | HIF_D1           | V4            |  |  |  |

| 9   | GROUND           | U5            | 10  | HIF_RS           | V5            |  |  |  |

| 11  | UC_VCCQ          | U6            | 12  | HIF_RDY          | V6            |  |  |  |

| 13  | GROUND           | U7            | 14  | GROUND           | V7            |  |  |  |

| 15  | GROUND           | U8            | 16  | GROUND           | V8            |  |  |  |

| 17  | DV12             | U9            | 18  | GROUND           | V9            |  |  |  |

| 19  | UV12             | U10           | 20  | GROUND           | V10           |  |  |  |

| 21  | AV12             | U11           | 22  | AGND             | V11           |  |  |  |

| 23  | UC_VCC           | U12           | 24  | SSI_WS1          | V12           |  |  |  |

| 25  | GROUND           | U13           | 26  | SSI_DATA1        | V13           |  |  |  |

| 27  | UC_VCCQ          | U14           | 28  | TXD1             | V14           |  |  |  |

| 29  | UC_VCCQ          | U15           | 30  | SCK1             | V15           |  |  |  |

| 31  | GROUND           | U16           | 32  | AUDIOCLK         | V16           |  |  |  |

| 33  | GROUND           | U17           | 34  | тск              | V17           |  |  |  |

| 35  | MD_CLK1          | U18           | 36  | TDI              | V18           |  |  |  |

| 37  | NMI              | U19           | 38  | MD_CLK0          | V19           |  |  |  |

| 39  | NC               | -             | 40  | CON_EXTAL        | V20           |  |  |  |

Table 9-7: J7

|     |                  | J             | 18  |                  |               |

|-----|------------------|---------------|-----|------------------|---------------|

| Pin | Circuit Net Name | Device<br>Pin | Pin | Circuit Net Name | Device<br>Pin |

| 1   | GROUND           | W1            | 2   | HIF_D8           | Y1            |

| 3   | HIF_D6           | W2            | 4   | HIF_D5           | Y2            |

| 5   | HIF_D3           | W3            | 6   | HIF_D2           | Y3            |

| 7   | HIF_D0           | W4            | 8   | HIF_CSn          | Y4            |

| 9   | HIF_WRn          | W5            | 10  | HIF_RDn          | Y5            |

| 11  | HIF_DREQ         | W6            | 12  | HIF_INTn         | Y6            |

| 13  | HIF_EBL          | W7            | 14  | DV33             | Y7            |

| 15  | GROUND           | W8            | 16  | NC (USB D-)      |               |

| 17  | VBUS_IN          | W9            | 18  | NC (USB D+)      |               |

| 19  | AGND             | V11           | 20  | AV33             | Y10           |

| 21  | GROUND           | W11           | 22  | NC               |               |

| 23  | CON_USB_X1       | W12           | 24  | CON_USB_X2       | Y12           |

| 25  | LED1             | W13           | 26  | LED0             | Y13           |

| 27  | RXD1             | W14           | 28  | SCK2             | Y14           |

| 29  | LED2             | W15           | 30  | RXD2             | Y15           |

| 31  | LED3             | W16           | 32  | TXD2             | Y16           |

| 33  | SSI_SCK1         | W17           | 34  | ST_CLKOUT        | Y17           |

| 35  | RESn             | W18           | 36  | TRSTn            | Y18           |

| 37  | TDO              | W19           | 38  | TMS              | Y19           |

| 39  | CON_XTAL         | W20           | 40  | NC               |               |

Table 9-8: J8

## 9.2. Application Headers

| JA1 |                     |             |        |     |                     |             |        |  |

|-----|---------------------|-------------|--------|-----|---------------------|-------------|--------|--|

| Pin | Generic Header Name | CPU board   | Device | Pin | Generic Header Name | CPU board   | Device |  |

|     |                     | Signal Name | Pin    |     |                     | Signal Name | Pin    |  |

| 1   | 5V                  | CON_5V      |        | 2   | 0V                  | GROUND      |        |  |

| 3   | 3V3                 | CON_3V3     |        | 4   | 0V                  | GROUND      |        |  |

| 5   | AVcc                | NC          |        | 6   | AVss                | CON_AVSS    |        |  |

| 7   | AVref               | NC          |        | 8   | ADTRG               | NC          |        |  |

| 9   | AD0                 | NC          |        | 10  | AD1                 | NC          |        |  |

| 11  | AD2                 | NC          |        | 12  | AD3                 | NC          |        |  |

| 13  | DAC0                | NC          |        | 14  | DAC1                | NC          |        |  |

| 15  | IO_0                | IO_0        | N20    | 16  | 10_1                | IO_1        | N18    |  |

| 17  | 10_2                | 10_2        | M18    | 18  | IO_3                | IO_3        | M19    |  |

| 19  | IO_4                | IO_4        | M20    | 20  | IO_5                | IO_5        | L18    |  |

| 21  | IO_6                | IO_6        | L19    | 22  | IO_7                | 10_7        | L20    |  |

| 23  | IRQ3                | IRQ7n       | M3     | 24  | IIC_EX              | NC          |        |  |

| 25  | IIC_SDA             | SDA         | A4     | 26  | IIC_SCL             | SCL         | C5     |  |

\* Shared pins. Please refer to schematic.

|  | Table 9-9: | JA1 Si | tandard | Generic | Header |

|--|------------|--------|---------|---------|--------|