### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

### CMOS Logic IC HD74AC Series (FACT)

### **Definition of Specifications**

#### 1. Power Dissipation-Test Philosophy

In an erfort to reduce confusion about measuring  $C_{PD}$ , a JEDEC standard test procedure (7A Appendix E) has been adopted, which specifies the test setup for each type of device. This allows a device to be exercised in a consistent manner for the purpose of specification comparison. All device measurements are made with  $V_{CC} = 5.0$  V at 25°C, with 3-state outputs both enabled and disabled.

- Gates: Switch one input. Bias the remaining inputs such that the output switches.

- Latches: Switch the Enable and D inputs such that the latch toggles.

- Flip-Flops: Switch the clock pin while changing D (or bias J and K) such that the output (s) change each clock cycle. For parts with a common clock, exercise only one flip flop.

- Decoders: Switch one address pin which changes two outputs.

- Multiplexers: Switch one address pin with the corresponding data inputs at opposite logic levels so that the output switches.

- Counters: Switch the clock pin with other inputs biased such that the device counts.

- Shift Registers: Switch the clock pin with other inputs biased such that the device counts.

- Transceivers: Switch one data input. For bidirectional devices enable only one direction.

- Parity Generator: Switch one input.

- Priority Encoders: Switch the lowest priority input.

- Load Capacitance: Each output which is switching should be loaded with the standard 50 pF. The equivalent load capacitance, based upon the number of outputs switching and their respective frequency, is then subtracted form the measured gross C<sub>PD</sub> number to obtain the device's actual C<sub>PD</sub> value.

If the device is tested at a high enough frequency, the static supply current can be ignored. Thus at 1 MHz, the following formula can be used to calculate  $C_{PD}$ :

$C_{PD} = I_{CC}/(V_{CC}) (1 \times 10^6) - Equivalent Load Capacitance$

#### 2. Ratings and Specifications

#### Table 1 Absolute Maximum Ratings<sup>\*1</sup>

| Parameter                                           | Symbol                              | Limit                        | Unit | Condition                      |

|-----------------------------------------------------|-------------------------------------|------------------------------|------|--------------------------------|

| Supply voltage                                      | V <sub>CC</sub>                     | -0.5 to 7.0                  | V    |                                |

| DC input Diode current or DC input                  | I <sub>IK</sub>                     | -20                          | mA   | $V_1 = -0.5$                   |

| voltage                                             |                                     | 20                           | mA   | $V_1 = V_{CC} + 0.5$           |

|                                                     | VI                                  | –0.5 to V <sub>CC</sub> +0.5 | V    |                                |

| DC output Diode current or DC output                | I <sub>OK</sub>                     | -50                          | mA   | $V_0 = -0.5$                   |

| voltage                                             |                                     | 50                           | mA   | $V_{\rm O} = V_{\rm CC} + 0.5$ |

|                                                     | Vo                                  | –0.5 to V <sub>CC</sub> +0.5 | V    |                                |

| DC output source or sink current                    | lo                                  | ±50                          | mA   |                                |

| DC V <sub>CC</sub> or ground current per output pin | I <sub>CC</sub> or I <sub>GND</sub> | ±50                          | mA   |                                |

| Storage temperature                                 | T <sub>STG</sub>                    | –65 to 150                   | °C   |                                |

Note: 1. Absolute maximum ratings are those values beyond which damage to the device may occur. Obviously the document specifications should be met, without exception to ensure that the system design is reliable over its power supply, temperature, output/input loading variables. Renesas does not recommend operation of FACT circuits outside document specifications.

#### Table 2 Recommended Operating Conditions

| Parameter                                                                  | Symbol         | Limit           | Unit                 | Condition              |  |

|----------------------------------------------------------------------------|----------------|-----------------|----------------------|------------------------|--|

| Supply Voltage (unless otherwise AC devices                                |                | V <sub>cc</sub> | 2.0 to 6.0           | V                      |  |

| specified)                                                                 | ACT devices    |                 | 4.5 to 5.5           |                        |  |

| Input voltage                                                              | ·              | VI              | 0 to V <sub>CC</sub> | V                      |  |

| Output voltage                                                             | Vo             | 0 to $V_{CC}$   | V                    |                        |  |

| Operating temperature                                                      | T <sub>A</sub> | -40 to +85      | °C                   |                        |  |

| Input rise and Fall time <sup>*1</sup> (typical)                           | tr, tf         | 150             | ns/V                 | V <sub>CC</sub> @ 3.0V |  |

| (except Schmitt inputs) 'AC devices                                        |                | 40              | ns/V                 | V <sub>CC</sub> @ 4.5V |  |

| 30% to 70% of V <sub>CC</sub>                                              |                | 25              | ns/V                 | V <sub>CC</sub> @ 5.5V |  |

| Input rise and Fall time*1 (typical)                                       | tr, tf         | 10              | ns/V                 | V <sub>CC</sub> @ 4.5V |  |

| (except schmitt inputs) 'ACT device<br>0.8 to 2.0 V, Vmeas from 0.8 to 2.0 |                | 8               | ns/V                 | V <sub>CC</sub> @ 5.5V |  |

Note: 1. See individual data sheets for those devices which differ from the typical input rise and fall times noted here.

#### Table 3 DC Characteristics for HD74AC Family Devices

| Parameter                           | Symbol           | V <sub>cc</sub> | Ta = +25°C | Ta = -4 | 0 to +85°C | Unit     | Condition                                             |

|-------------------------------------|------------------|-----------------|------------|---------|------------|----------|-------------------------------------------------------|

|                                     |                  | (V)             | Тур        | Guaran  | teed Limit |          |                                                       |

| Minimum High Level                  | VIH              | 3.0             | 1.5        | 2.1     | 2.1        | V        | Vout = $0.1 \text{ V or}$                             |

| Input Voltage                       |                  | 4.5             | 2.25       | 3.15    | 3.15       |          | V <sub>CC</sub> –0.1 V                                |

|                                     |                  | 5.5             | 2.75       | 3.85    | 3.85       |          |                                                       |

| Maximum Low Level                   | V <sub>IL</sub>  | 3.0             | 1.5        | 0.9     | 0.9        | V        | Vout = 0.1 V or                                       |

| Input Voltage                       |                  | 4.5             | 2.25       | 1.35    | 1.35       |          | V <sub>CC</sub> –0.1V                                 |

|                                     |                  | 5.5             | 2.75       | 1.65    | 1.65       |          |                                                       |

| Maximum High Level                  | V <sub>OH</sub>  | 3.0             | 2.99       | 2.9     | 2.9        | V        | I <sub>OUT</sub> = -50 μA                             |

| Output Voltage                      |                  | 4.5             | 4.49       | 4.4     | 4.4        |          |                                                       |

|                                     |                  | 5.5             | 5.49       | 5.4     | 5.4        |          |                                                       |

|                                     |                  | 3.0             |            | 2.58    | 2.48       | V        | $V_{IN} = V_{IL} \text{ or } V_{IH}$                  |

|                                     |                  | 4.5             |            | 3.94    | 3.80       |          | –12 mA l <sub>OH</sub> –24 mA <sup>*1</sup><br>–24 mA |

|                                     |                  | 5.5             |            | 4.94    | 4.80       |          |                                                       |

| Maximum Low Level<br>Output Voltage | V <sub>OL</sub>  | 3.0             | 0.002      | 0.1     | 0.1        | V        | I <sub>OUT</sub> = 50 μA                              |

|                                     |                  | 4.5             | 0.001      | 0.1     | 0.1        |          |                                                       |

|                                     |                  | 5.5             | 0.001      | 0.1     | 0.1        |          |                                                       |

|                                     |                  | 3.0             |            | 0.32    | 0.37       | V        | $V_{IN} = V_{IL}$ or $V_{IH}$                         |

|                                     |                  | 4.5             |            | 0.32    | 0.37       |          | 12 mA I <sub>OL</sub> 24 mA <sup>*1</sup>             |

|                                     |                  | 5.5             |            | 0.32    | 0.37       |          | 24 mA                                                 |

| Maximum Input                       | I <sub>IN</sub>  | 5.5             |            | ±0.1    | ±1.0       | μA       | $V_{I} = V_{CC}, GND$                                 |

| Leakage Current                     |                  |                 |            |         |            |          |                                                       |

| Maximum 3-State                     | I <sub>OZ</sub>  | 5.5             |            | ±0.5    | ±5.0       | μA       | $V_{I (OE)} = V_{IL}, V_{IH}$                         |

| Current                             |                  |                 |            |         |            |          | $V_{I} = V_{CC}, V_{GND}$                             |

|                                     | l                |                 |            | ļ       |            | <u> </u> | $V_0 = V_{CC}, GND$                                   |

| Minimum Dynamic                     | I <sub>OLD</sub> | 5.5             | _          |         | 86         | mA       | V <sub>OLD</sub> = 1.1 V                              |

| Output Current *2                   | I <sub>OHD</sub> | 5.5             |            |         | -75        | mA       | V <sub>OHD</sub> = 3.85 V                             |

Notes: 1. All outputs loaded; thresholds on input associated with output under test.

2. Maximum test duration 2.0 ms, one output loaded at a time.

| Parameter                           | Symbol           | V <sub>cc</sub> | Ta = +25°C | Ta = -4          | 0 to +85°C | Unit | Condition                                      |

|-------------------------------------|------------------|-----------------|------------|------------------|------------|------|------------------------------------------------|

|                                     |                  | (V)             | Тур        | Guaranteed Limit |            |      |                                                |

| Minimum High Level                  | V <sub>IH</sub>  | 4.5             | 1.5        | 2.0              | 2.0        | V    | $V_{OUT} = 0.1 V \text{ or}$                   |

| Input Voltage                       |                  | 5.5             | 1.5        | 2.0              | 2.0        |      | V <sub>CC</sub> –0.1V                          |

| Maximum Low Level                   | V <sub>IL</sub>  | 4.5             | 1.5        | 0.8              | 0.8        | V    | $V_{OUT} = 0.1 V \text{ or}$                   |

| Input Voltage                       |                  | 5.5             | 1.5        | 0.8              | 0.8        |      | V <sub>CC</sub> –0.1V                          |

| Maximum High Level                  | V <sub>OH</sub>  | 4.5             | 4.49       | 4.4              | 4.4        | V    | I <sub>OUT</sub> = -50 μA                      |

| Output Voltage                      |                  | 5.5             | 5.49       | 5.4              | 5.4        |      |                                                |

|                                     |                  | 4.5             |            | 3.94             | 3.80       | V    | $V_{IN} = V_{IL} \text{ or } V_{IH}$           |

|                                     |                  | 5.5             |            | 4.94             | 4.80       |      | I <sub>OH</sub> –24 mA <sup>*1</sup> , –24 mA  |

| Maximum Low Level<br>Output Voltage | V <sub>OL</sub>  | 4.5             | 0.001      | 0.1              | 0.1        | V    | Ι <sub>ΟUT</sub> = 50 μΑ                       |

|                                     |                  | 5.5             | 0.001      | 0.1              | 0.1        |      |                                                |

|                                     |                  | 4.5             |            | 0.32             | 0.37       | V    | $V_{IN} = V_{IL} or V_{IH}$                    |

|                                     |                  | 5.5             |            | 0.32             | 0.37       |      | I <sub>OL</sub> 24 mA <sup>*1</sup> , 24 mA    |

| Maximum Input<br>Current            | I <sub>IN</sub>  | 5.5             |            | ±0.1             | ±1.0       | μA   | $V_1 = V_{CC}, \text{ GND}$                    |

| Maximum 3-State<br>Current          | I <sub>oz</sub>  | 5.5             |            | ±0.5             | ±5.0       | μA   | $V_{I} = V_{IL}, V_{IH}$ $V_{O} = V_{CC}, GND$ |

| Maximum<br>ICC/Input Current        | I <sub>CCT</sub> | 5.5             | 0.6        |                  | 1.5        | mA   | $V_{I} = V_{CC} - 2.1V$                        |

| Minimum Dynamic                     | I <sub>OLD</sub> | 5.5             |            |                  | 86         | mA   | V <sub>OLD</sub> = 1.1 V                       |

| Output Current <sup>*2</sup>        | I <sub>OHD</sub> | 5.5             |            |                  | -75        | mA   | V <sub>OHD</sub> = 3.85 V                      |

#### Table 4 DC Characteristics for HD74ACT Family Devices

Notes: 1. All outputs loaded; thresholds on input associated with output under test.

2. Maximum test duration 2.0 ms, one output loaded at a time.

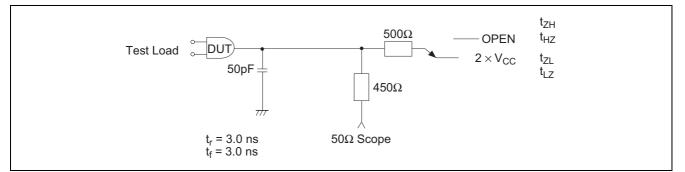

Figure 1 AC Loading Circuit

#### 3. AC Loading and Waveforms

#### 3.1 Loading Circuit

Figure 1 shows the AC loading circuit used in characterizing and specifying propagation delays of all FACT devices (HD74AC and HD74ACT) unless otherwise specified in the data sheet of a specific device.

The use of this load, differs somewhat from previous practice provides more meaningful information and minimizes problems of instrumentation and customer correlation. In the past, +25°C propagation delays for TTL devices were specified with a load of 15 pF to ground; this required great care in building test jigs to minimize stray capacitance and implied the use of high-impedance, high-frequency scope probes. FACT circuits changed to 50 pF of capacitance, allowing more leeway in stray capacitance and also loading the device during rising or falling output transitions.

This more closely resembles the inloading to be expected in average applications and thus gives the designer more useful delay figures. We have incorporated this scheme into the FACT product line. The net effect of the change in AC load is to increase the average observed propagation delay by about 1 ns.

# RENESAS

#### CMOS Logic IC HD74AC Series (FACT) Definition of Specifications

The 500  $\Omega$  resistor to ground can be a high-frequency passive probe for a sampling oscilloscope, which costs much less than the equivalent high-impedance probe. Alternately, the 500  $\Omega$  resistor to ground can simply be a 450  $\Omega$  resistor feeding into a 50  $\Omega$  coaxial cable leading to a sampling scope input connector, with the internal 50 W termination of the scope completing the path to ground. This is the preferred scheme for correlation. (See figure 1.) With this scheme there should be a matching cable from the device input pin to the other input of the sampling scope; this also serves as a 50  $\Omega$  termination for the pulse generator that supplies the input signal.

Shown in figure 1 is a second 500  $\Omega$  resistor from the device output to a switch. For most measurements this switch is open; it is closed for measuring one set of the Enable/Disable parameters (low-to-off and off-to-low) of a 3-state output. With the switch closed, the pair of 500  $\Omega$  resistors and the 2 × V<sub>CC</sub> supply voltage establish a quiescent high level.

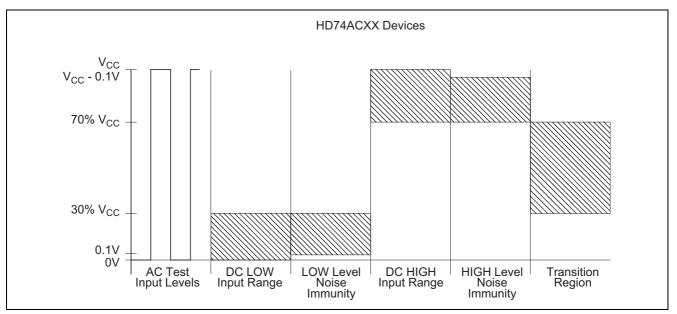

Figure 2a Test Input Signal Levels

Figure 2b Test Input Signal Levels (cont)

#### 3.2 Test Conditions

Figure 2 describes the input signal voltage levels to be used when testing FACT circuits. The AC test conditions follow industry convention requiring  $V_{IN}$  to range from 0 V for a logic low to 3.0 V for a logic high for HD74ACT devices and 0 V to  $V_{CC}$  for HD74AC devices. The DC parameters are normally tested with  $V_{IN}$  at guaranteed input levels, that is

# RENESAS

$V_{IH}$  to  $V_{IL}$  (see tables 3 and 4 for details). Care must be taken to adequately decouple these high performance parts and to protect the test signals from electrical noise. In an electrically noisy environment, (e.g., a tester and handlder not specifically designed for high-speed work), DC input levels may need to be adjusted to increase the noise margin to allow for the extra noise in the tester which would not be see in a system.

Noise immunity testing is performed by raising  $V_{IN}$  to the nominal supply voltage of 5.0 V then dropping it to a level corresponding to  $V_{IH}$ , and then raising it again to the 5.0 V level. Noise tests can also be performed on the  $V_{IL}$  characteristics by raising  $V_{IN}$  from 0 V to  $V_{IL}$ , then returning it to 0 V. Both  $V_{IH}$  and  $V_{IL}$  noise immunity tests should not induce a switch condition on the appropriate outputs of the FACT device.

Good high-frequency wiring practices should be used in constructing test jigs. Leads on the load capacitor should be as short as possible to minimize ripples on the output waveform transitions and to minimize undershoot. Generous ground metal (preferably a ground plane) should be used for the same reasons. A  $V_{CC}$  bypass capacitor should be provided at the test socket, also with minimum lead lengths.

#### 3.3 Rise and Fall Times

Input signals should have rise and fall times of 3.0 ns and signal swing of 0 V to 3.0 V for HD74ACT devices or 0 V to  $V_{CC}$  for HD74ACT devices. Rise and fall times less than or equal to 1 ns should be used for testing  $f_{max}$  or pulse widths.

CMOS devices, including, 4000 Series CMOS, HC, HCT and FACT families, tend to oscillate when the input rise and fall times become lengthy. As a direct result of its increased performance, FACT devices can be more sensitive to slow input rise and fall times than other lower performance technologies.

It is important to understand why this oscillation occurs. Consider the outputs, where the problem is initiated. Usually, CMOS outputs drive capacitive loads with low DC leakage. When the output changes from a high level to a low level, or from a low level to a high level, this capacitance has to be charged or discharged. With the present high performance technologies, this charging or discharging takes place in a very short time, typically 2-3 ns. The requirement to charge or discharge the capacitive loads quickly creates a condition where the instantaneous current change through the output structure is quite high. A voltage is generated across the VCC or ground leads inside the package due to the inductance of these leads. The internal ground of the chip will change in reference to the outside world become of this induced voltage.

Consider the input. If the internal ground changes, the input voltage level appears to change to the DUT. If the input rise time is slow enough, its level might still be in the device threshold region, or very close to it, when the output switches. If the internally-induced voltage is large enough, it is possible to shift the threshold region enough so that it re-crosses the input level. If the gain of the device is sufficient and the input rise or fall time is slow enough, then the device may go into oscillation. As device propagation delays become shorter, the inputs will have less time to rise or fall through the threshold region. As device gains increase, the outputs will swing more, creating more induced voltage. Instantaneous current change will be greater as outputs become quicker, generating more induced voltage.

Package-related causes of output oscillation are not entirely to blame for problems with input rise and fall time measurements. All testers have  $V_{CC}$  and ground leads with a finite inductance. This inductance needs to be added to the inductance in the package to determine the overall voltage which will be induced when the outputs change. As the reference for the input signals moves further away from the pin under test, the test will be more susceptible to problems caused by the inductance of the leads and stray noise. Any noise on the input signal will also cause problems. With FACT logic having gains as high as 100, it merely takes a 50 mV change in the input to generate a full 5 V swing on the output.

#### 3.4 Propagation Delays, f<sub>max</sub>, Set and Hold Times

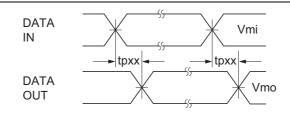

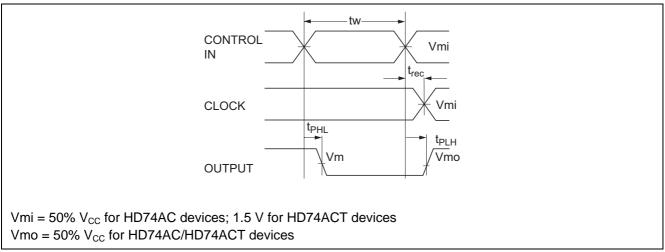

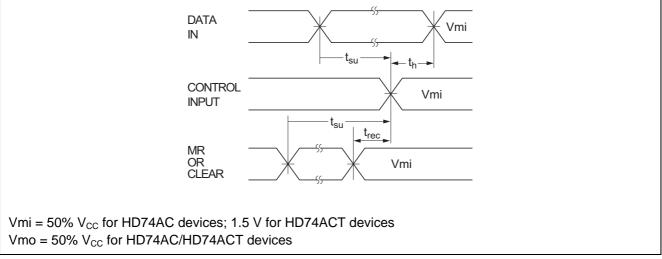

A 1.0 MHz square wave is recommended for most propagation delay tests (figures 3 and 4) The repetition rate must necessarily be increased for testing  $f_{max}$ . A 50% duty cycle should always be used when testing  $f_{max}$ . Two pulse generators are usually required for testing such parameters as setup time, hold time, recovery time etc.

Vmi = 50% V<sub>CC</sub> for HD74AC devices; 1.5 V for HD74ACT devices Vmo = 50% V<sub>CC</sub> for HD74AC/HD74ACT devices

#### 3.5 Enable and Disable Times

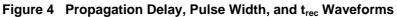

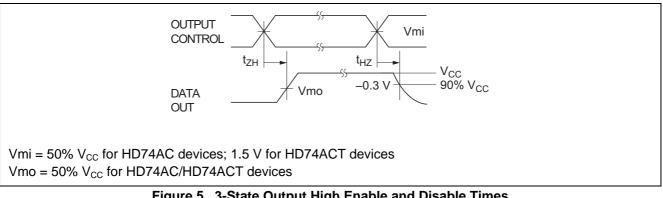

Figures 5 and 6 show that the disable times are measured at the point where the output voltage has risen or fallen by 10% from the voltage rail level (i.e., ground for  $t_{LZ}$  or  $V_{CC}$  for  $t_{HZ}$ ). This change enhances the repeatability of measurements, reduces test time, and gives the system designer more realistic delay times to use in calculating minimum cycle times. Since the high-impedance state rising or falling waveform is RC-controlled, the first 10% of change is more linear and is less susceptible to external influences. More importantly, perhaps from the system designer's point of view, a change in voltage of 10% is adequate to ensure that a device output has turned off. Measuring to a larger change in voltage merely exaggerates the apparent Disable time and thus penalizes system performance since the designer must use the Enable and Disable times to device worst case timing signals to ensure that the output of one device is disabled before that of another device is enabled.

Figure 5 3-State Output High Enable and Disable Times

#### Figure 6 3-State Output Low Enable and Disable Times

#### 3.6 Electrostatic Discharge

Precautions should be taken to prevent damage to devices by electrostatic discharge. Static charge tends to accumulate on insulated surfaces such as synthetic fabrics or carpeting, plastic sheets, trays, foam, tubes or bags, and on ungrounded electrical tools or appliances. The problem is much worse in a dry atmosphere. In general, it is recommended that individuals take the precaution of touching a known ground before handling devices. More often, handling equipment that is not properly grounded, causes damage to parts. Ensure that all plastic parts of the tester, that are near the device, are conductive and connected to ground.

Figure 7 Setup Time, Hold Time and Recovery Time

#### 4. Symbols and Terms Defined for HD74AC Series

Explanation of Symbols Used in Electrical Characteristics and Recommended Operating Conditions

#### Table 5 DC Characteristics

| Symbol                      | Term                                      | Description                                                                                                                                                                          |

|-----------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub>             | High level input voltage                  | High level input voltage to ensure that a logic element operates under some constraint                                                                                               |

| V <sub>IL</sub>             | Low level input voltage                   | Low level input voltage to ensure that a logic element operates under some constraint                                                                                                |

| V <sub>OL</sub>             | Low level output voltage                  | Output voltage in effect when, under the input condition for bringing the output low, the rated output current is allowed to flow to the output terminal                             |

| V <sub>OH</sub>             | High level output voltage                 | Output voltage in effect when, under the input condition for bringing the output high, the rated output current is allowed to flow to the output terminal                            |

| V <sub>t</sub> <sup>+</sup> | Forward input threshold voltage           | Input voltage in effect when the operation of a logic element varies as the input is allowed to go up form a voltage level lower than the reverse input threshold voltage $V_t^-$    |

| V <sub>t</sub> <sup>-</sup> | Reverse input threshold voltage           | Input voltage in effect when the operation of a logic element varies as the input is allowed to drop up form a voltage level higher than the forward input threshold voltage $V_t^+$ |

| V <sub>h</sub>              | Hysteresis voltage                        | Difference between forward input threshold voltage $V_t^{ *}$ and reverse threshold voltage $V_t^{-}$                                                                                |

| I <sub>IN</sub>             | Input leakage current                     | Input current that flows in when the rated maximum input voltage is applied to the input terminal                                                                                    |

| I <sub>OZ</sub>             | Off-state output current (high-impedance) | Current that flows to the 3-state output of an element under the input condition for bringing the output to high-impedance state                                                     |

| I <sub>CC</sub>             | Quiescent Supply current                  | Current that flows to the supply terminal (V <sub>CC</sub> ) under the rated input condition                                                                                         |

| I <sub>OLD</sub>            | Minimum Dynamic Output<br>Current         | Output current that flows in when, under the condition for bringing the output low, the output terminal is tied to the rated out voltage $V_{OLD}$ .                                 |

| I <sub>OHD</sub>            |                                           | Output current that flows out when, under the condition for bringing the output high, the output terminal is tied to the rated out voltage $V_{\text{OHD}}$ .                        |

| I <sub>CCT</sub>            | Maximum I <sub>cc</sub> /Input            | Current that flows to the supply terminal ( $V_{CC}$ ) under the rated input condition                                                                                               |

#### Table 6 AC Characteristics

| Symbol           | Term                                     | Description                                                                                                                                                                             |

|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>max</sub> | Maximum clock frequency                  | Maximum clock frequency that maintains the stable<br>changes in output logic level in the rated sequence<br>under the I/O condition allowing clock pulses to change<br>the output state |

| t <sub>τLH</sub> | Rise (transient) time                    | Rated time from low level to high level of a waveform<br>during the defined transient period changing from low<br>level to high level                                                   |

| t <sub>THL</sub> | Fall (transient) time                    | Rated time from high level to low level of a waveform<br>during the defined transient period changing from high<br>level to low level                                                   |

| t <sub>PLH</sub> | Output rise propagation delay time       | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the output changing from low level to high level                            |

| t <sub>PHL</sub> | Output fall propagation delay time       | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the output changing from high level to low level                            |

| t <sub>HZ</sub>  | 3-state output disable time (high level) | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from high level to the high-impedance state     |

| t <sub>LZ</sub>  | 3-state output disable time (low level)  | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from low level to the high-impedance state      |

| t <sub>ZH</sub>  | 3-state output enable time (high level)  | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from the high-impedance state to high level     |

| t <sub>ZL</sub>  | 3-state output enable time (low level)   | Delay time between the rated voltage levels of an I/O voltage waveform under a defined load condition, with the 3-state output changing from the high-impedance state to low level      |

| t <sub>w</sub>   | Pulse width                              | Duration of time between the rated levels from a leading edge to a trailing edge of a pulse waveform                                                                                    |

| t <sub>h</sub>   | Hold time                                | Time in which to hold data at the specified input<br>terminal after a change at another related input<br>terminal (e.g., clock input)                                                   |

| t <sub>SU</sub>  | Setup time                               | Time in which to set up and keep data at the specified<br>input terminal before a change at another related input<br>terminal (e.g., clock input)                                       |

| t <sub>rec</sub> | Recovery time                            | Time period between the time when data at the specified input terminal is released and the time when another related input terminal (e.g., clock input) can be changed                  |

| C <sub>IN</sub>  | Input capacitance                        | Capacitance between GND terminal and an input terminal to which 0 V is applied                                                                                                          |

| CPD              | Power Dissipation Capacitance            | Equivalent device power capacitance in dynamic state                                                                                                                                    |

#### Table 7 Explanation of Symbols Used in Function Tables

| Symbol   | Description                                                                                                  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------|--|--|

| Н        | High level (in steady state; written H or "H" level in sentences)                                            |  |  |

| L        | Low level (in steady state; written L or "L" level in sentences)                                             |  |  |

|          | Transition from L level to H level                                                                           |  |  |

| <u> </u> | Transition from H level to L level                                                                           |  |  |

| Х        | Either H or L                                                                                                |  |  |

| Z        | 3-state output off (high impedance)                                                                          |  |  |

| ah       | Input level of steady state for each of inputs A-H                                                           |  |  |

| Q0       | Q level immediately before the indicated input condition is established                                      |  |  |

| Q0       | Complement of Q <sub>0</sub>                                                                                 |  |  |

| Qn       | Q level immediately before the latest active change ( $\_$ or $\_$ ) occurs                                  |  |  |

|          | Single H level pulse                                                                                         |  |  |

|          | Single L level pulse                                                                                         |  |  |

| TOGGLE   | Each output is changed to the complement of the preceding state by an active input change ( $-\int$ or $-$ ) |  |  |

#### **Revision Record**

|      |           |      | Description          |  |  |  |

|------|-----------|------|----------------------|--|--|--|

| Rev. | Date      | Page | Summary              |  |  |  |

| 1.00 | Jul.09.04 | —    | First edition issued |  |  |  |

|      |           |      |                      |  |  |  |

|      |           |      |                      |  |  |  |

|      |           |      |                      |  |  |  |

|      |           |      |                      |  |  |  |

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.