MM5033 November 1991

Harris Analog

## HA-5033 SPICE BUFFER AMPLIFIER MACRO-MODEL

Author: David Riemer

#### Introduction

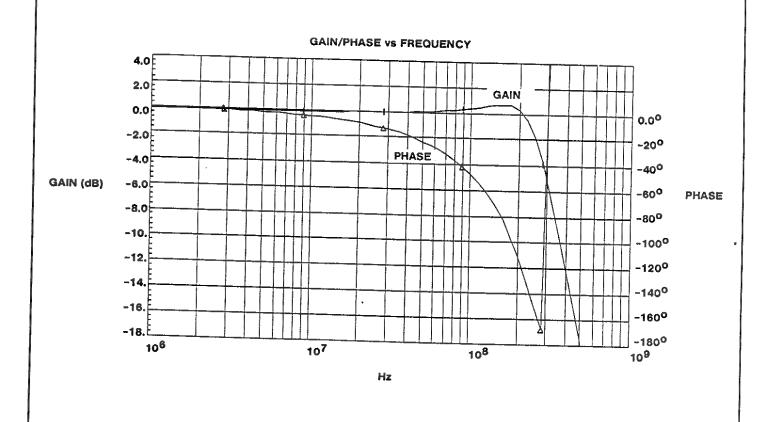

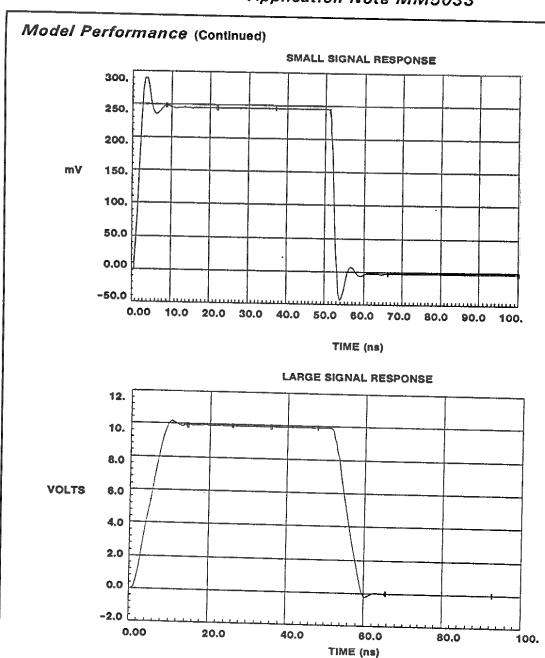

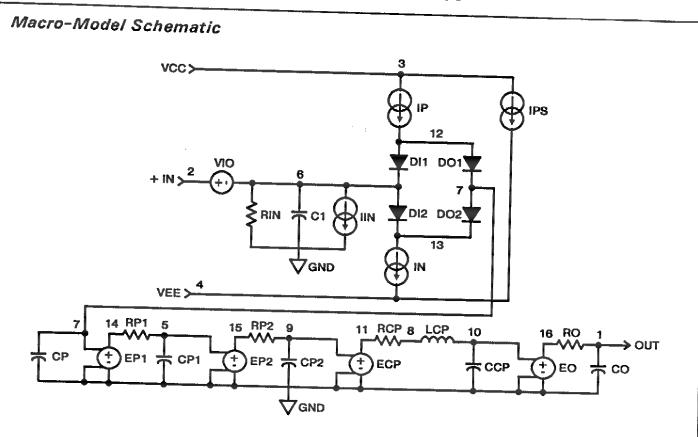

This application note describes the SPICE macro-model for the HA-5033, a wide bandwidth, high output current, buffer amp. The model was designed to be compatible with the well known SPICE program developed by the University of California in hope that most simulation software vendors follow this basic format and syntax. A schematic of the macro-model, the Spice net listing and various simulated performance curves are included. The macro-model schematic includes node numbers to help relate the SPICE listing to the schematic. The model is designed to emulate a typical rather than a worst case part. Most AC and DC paramaters are simulated. Significant poles and zeros are included to give the most accurate AC and transient simulation with minimum complexity.

### Model Description

CIN and RIN represent the input parasitics of the HA-5033, with voltage source VIO modelling the offset voltage. Diodes DI1, DI2, DO1, and DO2 with current sources IP and IN and capacitor CP model slew rate. Current source IIN provides the DC input current. Power supply current is modeled by current source IPS.

The most significant singularities of the HA-5033 are modeled by EP1,2 and ECP, RP1,2, RCP, CP1,2, CCP and LCP.

Source EO and elements RO and CO model the output stage and package parasitics.

### Parameters Not Modeled

To maintain a simple macro-model not all op amp parameters are modeled. Most of the parameters not modeled are listed below:

- Power Supply Range

- Temperature Effects

- Input and Output Voltage Limits.

- Input Voltage and Current Noise.

- Tolerances for Monte Carlo Analysis

- Power Supply Current Tracking of Output Current.

Harris Corporation, Semiconductor Sector, makes no warranty, either expressed or implied, including but not limited to any warranties or merchantability and fitness for a particular purpose using this macro-model. This macro-model is provided solely and exclusively for use by Harris customers to assist them in the assessment of this product for possible applications. In no event will Harris be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of the macro-model. Although every effort has been made to ensure accuracy of the information contained in this application note, Harris assumes no responsibility for inadvertent errors. Harris reserves the right to make changes to the product and the macro-model without prior notice.

```

Spice Listing

*COPYRIGHT (C) 1991 HARRIS CORPORATION

*ALL RIGHTS RESERVED

*HA-5033 MACRO-MODEL

*REV: 7-29-91

*BY: D.W. RIEMER

*PINOUT:

IN VCC VEE OUT

.SUBCKT HA5033 2 3 4 1

.MODEL D1 D IS=5.57E-11 N=1 RS=10

*INPUT STAGE

*OFFSET VOLTAGE MAY BE VARIED BY

ADJUSTING THE VALUE OF SOURCE VIO.

VIO 26+3E-03

RIN 6 0 +1.5E+06

CIN 60+1E-12

IIN 6 0 +2E-05

IP 3 12 +2E-04

IN 134+2E-04

DO1 12 7 D1

DI2613D1

DO2713D1

DI1 126 D1

CP 7 0 +7.5E-14

*SINGULARITIES

*GAIN MAY BE ADJUSTED BY CHANGING

THE VALUE OF EP1 (0.995->?)

EP1 14 0 7 0 0.995

EP2 15 0 5 0 1

ECP 11 09 01

RP1 14 5 500

RP2 15 9 100

RCP 11 8 +1E+03

LCP 8 10 +7.5E-07

CP1 5 0 +1E-12

CP2 9 0 +1E-12

CCP 100 +6E-13

*OUTPUT STAGE

IPS 3 4 +2.1E-03

EO 16 0 10 0 1

RO 16 1 1

CO 1 0 +1E-12

.ENDS HA5033

```

# Model Performance