### Introduction

The VersaClock5 - 5P49V59xx family programmer board is made to ease the programming of blank 5P49V59xx parts. With the on-board USB interface, IDT Timing Commander™ GUI can be used to communicate with the VersaClock5 family of devices in the socket for configuration and programming. The family of VersaClock 5 devices includes the following part numbers: 5P49V5901, 5P49V5913, 5P49V5914, 5P49V5923, 5P49V5925, 5P49V5927, 5P49V5929, 5P49V5933, 5P49V5935.

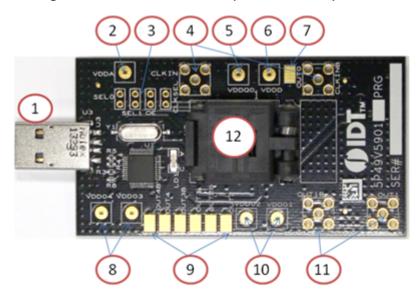

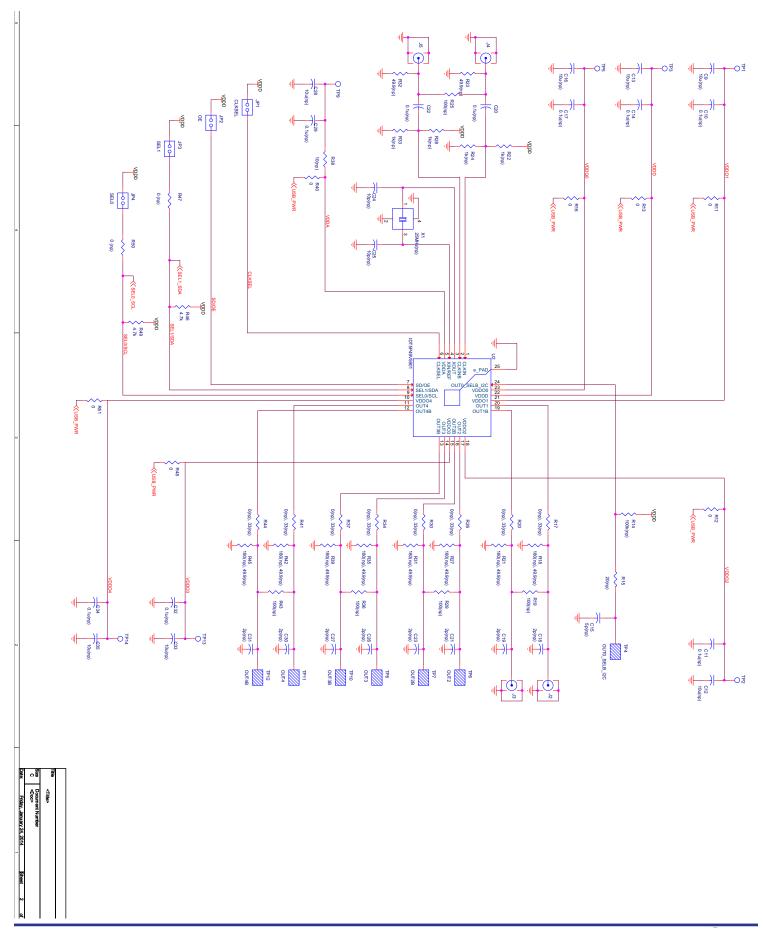

#### **Board Overview**

As shown the in the following diagram, all necessary components and connections are available to test the functionality of the configuration after the device is programmed. By installing R14 on the back of the board with a  $100 \text{K}\Omega$  resistor, the device will be powering up in hardware select mode, in which SEL1 and SEL0 pins can be used to switch among 4 configurations that the device supports.

Figure 1. Programmer Board Overview (socket closed)

- 1. USB Connector

- 2. VDDA

- SEL[1:0]/OE/CLKSEL

- 4. CLKIN/CLKINB

- VDD00

- 6. VDDD

- OUT0

- 8. VDD03/4

- Test Pads for OUT2/2B, OUT3/3B & OUT4/4B

- 10. VDDO1/2

- 11. OUT1/1B

- 12. Socket

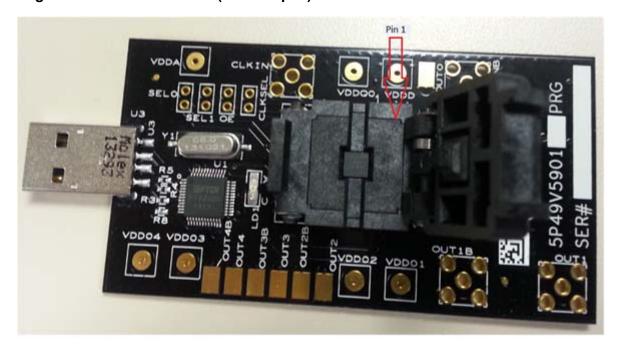

### Placing a Blank Chip in the Socket

When socket is open, identify the position of Pin 1 as shown in Figure 2. Align the dot of the blank device with the round dent engraved on the corner of the socket as pointed. After placing the blank device, secure the socket cover.

Figure 2. Programmer Board Overview (socket open)

# **Programming Steps**

- 1. Place a blank part in the socket—Refer to Figure 2 above. With socket opened, identify pin 1 position and place a blank part accordingly. Close the socket and secure the socket lid.

- 2. **Plug the board into USB port** –USB port provides power to the board as well as a communication channel between GUI and the device.

- 3. **Start Timing Commander GUI**—Launch the Timing Commander GUI software. Load the proper personality file.

- 4. Start a new settings file or open a pre-optimized configuration file.

- 5. **Connect to the board**—Click on the chip symbol on the top-right corner of the GUI window, as shown in Figure 3 below (left). A rectangular area in green will display (right).

Figure 3. Connecting to the chip: Left: click on the chip symbol to make the connection; Right: A green area appears if I<sup>2</sup>C communication is established.

- 6. **Execute "Write All" command**—Double check the setting file that is open in GUI window and make sure everything is correct. Then click on "Write-All" symbol in the green area (See Figure 3 above, right). This is a step that must be executed before OTP programming of the device.

- 7. Click on OTP button in the GUI—On lower left portion of GUI window, there is a button called OTP (Figure 4: left). Click this button to open OTP Programming dialogue window (Figure 4: right).

Figure 4. OTP Dialogue Window

In OTP dialogue window, there is a box in front of each configuration. Check the box for the configuration(s) that you want to program. One or more configurations can be selected at the same time. If All is checked, all 4 configuration will be programmed.

After intended configuration(s) is selected, then programming the device is only one click away – click on the blue "Burn" button will launch the programming. If one or more of the target configurations have already been burned, there will be a warning.

Once done, a completion message will pop out which indicates a successful programming:

Figure 5. Message for Successful Programming

**Important**: Burning irreversibly converts ones to zeroes; it is possible to go back and burn an unburned bit or bits to zero; zeroes cannot be restored to ones. This allows revision of a burn under limited circumstances.

### **Loading from OTP**

For loading one or more configurations from a burned part into the VC5 GUI ("load OTP") follow these steps: Before reading back cycle the power on the part and set the input crystal and/or clock frequencies in the GUI to those in the original configuration(s). This must be done manually because there is no way to store this information on the part itself. If there is more than one configuration, this step must be repeated for each one.

Connect to the part. The "OTP" button becomes enabled. In personalities 1.27 and later, the "Active" and "Configuration" indicator lights will be displayed (see Figure 6 below), and be illuminated or dark as appropriate. The green "Active" light means that the "OTP Burned" bit (R0[7]) has been burned. The red "Configuration" lights are illuminated as appropriate: if on, that configuration in the OTP has been burned.

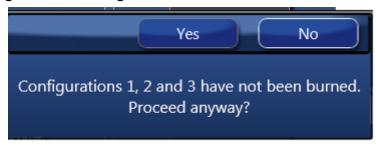

Click the "OTP" button. In the OTP dialog, check the boxes of the configurations to be loaded. If you check a box corresponding to an unburned configuration, there will be a warning (see Figure 7 below). If there are four configurations, there is an "All" checkbox for convenience (see Figure 8 below). Click "Load".

Figure 6. Indicator Lights

Figure 7. Unburned Configuration Warning

Figure 8. OTP "All" Checkbox

## In-System VersaClock 5 OTP Non-Volatile Programming via I2C

The procedure below enables the user to calibrate the device to a proper VCO band that will guarantee functionality over the full temperature range of the device. That band will then be programmed into the OTP. Certain conditions are required to properly program the device.

- 1. Conditions: Ambient temperature 25°C, 3.3V. For any other conditions, contact IDT.

- 2. Procedure:

- a. Power-up the device

- b. Write all relevant bits to the device to program PLL, FOD and output types

- c. Provide a reference clock to the IC corresponding to the configuration.

- d. Specific bits need to be set:

- Set VCO Monitoring in address x1D, bit[1] to "0"

- Set "AFC Enable" bit in address x16, bit[3] to "0"

- Set Test mode bit in register 0x11 (bit[5]) to "0"

- e. Perform VCO Calibration:

- Toggle bit[7] in 0x1C by writing the bit to 0 then 1 and then back to 0. Final state of the bit should be 0.

- Wait 100 ms

- Read band in I2C register 0x99 bit[7:3]

(read only register located in the factory programmable section of the RAM)

- The value read from register 0x99 has to be different from 0 or 23. If this is not the case then repeat the Calibration step.

- Write the content of the I2C register 0x99 bit[7:3] to the bits bit[4:0] into register 0x11.

- f. Programming the OTP

Before programming the OTP, change Test mode bit in register 0x11 (bit[5]) to "1" to force the chip to run the band number written previously in bits[4:0].

Now program the OTP by following the steps on page 5 of the <u>VersaClock 5 Family Register Descriptions and Programming Guide.</u>

## VersaClock 5 Volatile Programming via I2C

The procedure below enables the user to calibrate the device to a proper VCO band that will guarantee functionality over the full temperature range of the device. Certain conditions are required to properly calibrate the VCO.

- 1. Conditions: Ambient temperature 25°C, 3.3V. For any other conditions, contact IDT.

- 2. Procedure:

- a. Power-up the device

- b. Write all relevant bits to the device to program PLL, FOD and output types

- c. Provide a reference clock to the IC corresponding to the configuration written in point b.

- d. Specific bits need to be set:

- Set VCO Monitoring in address x1D, bit[1] to "0"

- Set Test mode bit in register 0x11 (bit[5]) to "0"

- e. Perform VCO Calibration:

- f. Toggle bit[7] in 0x1C by writing the bit to 0 then 1 and then back to 0. Final state of the bit should be 0.

- Wait 100 ms

#### **Programmed Device Testing**

As indicated in the Board Overview section, the programmed device can be verified with this same board. To verify, complete the following:

- Install R14 (100K $\Omega$ ) and then power up to latch the board in hardware selection mode

- Pull-up or pull-down SEL1 and SEL0 pins to proper levels to match the specific configuration for verification.

- Supply VDDA, VDDD and VDDO0~4

- Supply a reference signal via CLKIN/CLKINB (needed to populate C20 and C22) or a Crystal (X1) needs to placed, if not populated in the 3.2x2.5mm package. A Crystal is not necessary for 5P49V5933/35 devices.

- In order to probe the output(s) of interest the following components need to be placed:

- 1) R15 and C15 need to be populated to measure OUT0.

- 2) R17, R18 and J2 to measure OUT1.

- 3) R20, R21 and J3 to measure OUT1B. R19 s required only when measuring OUT1B and OUT1 in LVDS mode.

- 4) R26, R27 to measure OUT 2.

- 5) R30, R31 to measure OUT2B. R29 is only required when measuring OUT2B and OUT3 in LVDS mode.

- 6) R34, R35 to measure OUT 3.

- 7) R37, R39 to measure OUT3B. R36 is only required when measuring OUT2B and OUT3 in LVDS mode.

- 8) R41, R42 to measure OUT4.

- 9) R44, R45 to measure OUT4B. R43 is only required when measuring OUT2B and OUT3 in LVDS mode.

The recommended values depends on which driver output has been selected – LVDS, LVPECL, HCSL or LVCMOS:

- LVCMOS requires 33Ω resistor termination in series.

- LVDS requires  $0\Omega$  resistor in series and  $100\Omega$  in parallel between the 2 differential outputs.

- LVPECL requires  $0\Omega$  resistor in series and  $180\Omega$  to ground for each differential signal.

- HCSL requires  $33\Omega$  resistor in series and  $50\Omega$  to ground for each differential signal.

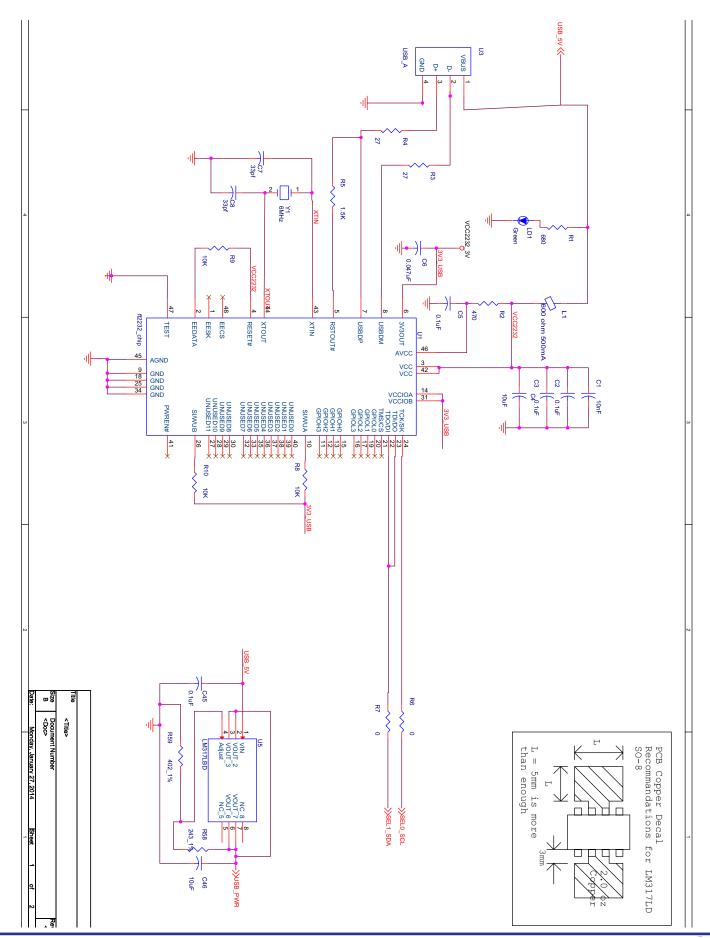

Please refer to the board schematics on the following pages of this document.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.