# **Document**

# V850E2/Fx4-L

# 32-bit Microcontroller

| 1 | 1 | R | 5 | N | E | 2/         | F | F | 4- | ı |

|---|---|---|---|---|---|------------|---|---|----|---|

| • | , | u | J | u |   | <b>~</b> I |   | _ | _  |   |

μPD70F3570 μPD70F3571 μPD70F3572

#### V850E2/FG4-L

μPD70F3576 μPD70F3577 μPD70F3578 μPD70F3579 μPD70F3580

#### V850E2/FF4-L

μPD70F3573 μPD70F3574 μPD70F3575

#### V850E2/FJ4-L

μPD70F3582 μPD70F3583 μPD70F3584 μPD70F3585

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- All information included in this document is current as of the date this document is issued. Such

information, however, is subject to change without any prior notice. Before purchasing or using any

Renesas Electronics products listed herein, please confirm the latest product information with a

Renesas Electronics sales office. Also, please pay regular and careful attention to additional and

different information to be disclosed by Renesas Electronics such as that disclosed through our

website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other

intellectual property rights of third parties by or arising from the use of Renesas Electronics

products or technical information described in this document. No license, express, implied or

otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of

Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics.

The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and

measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control

systems; anti-disaster systems; anti-crime systems; safety equipment; and

medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control

systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to

human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# **Table of Contents**

| Notice  |          |                                                       | 2  |

|---------|----------|-------------------------------------------------------|----|

| Genera  | al Pred  | cautions in the Handling of MPU/MCU Products          | 4  |

| Table o | of Con   | tents                                                 | 5  |

| How to  | use t    | his manual                                            | 20 |

| Purpe   | ose and  | d target readers                                      | 20 |

| •       |          | al notations                                          |    |

|         | Electri  | cal specifications                                    | 20 |

|         | Additio  | onal documents                                        | 20 |

| Conte   | ent of t | his manual                                            | 21 |

| Notat   | ion of   | numbers and symbols                                   | 22 |

|         |          | -                                                     |    |

| _       |          |                                                       |    |

|         |          | modules descriptions                                  |    |

|         |          | onal modules abbreviation convention                  |    |

|         |          | ct specific features                                  |    |

| Furth   |          | rmation                                               |    |

|         |          |                                                       |    |

| Chapte  | er 1     | Introduction                                          | 30 |

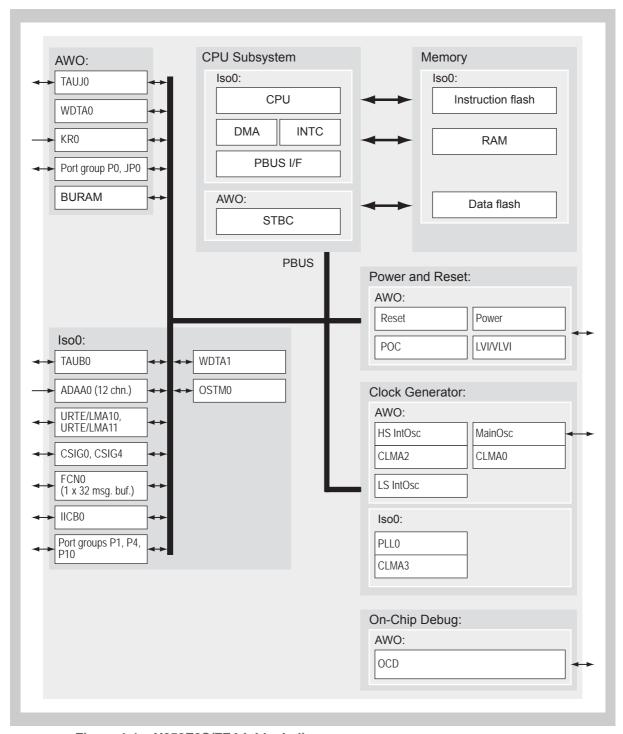

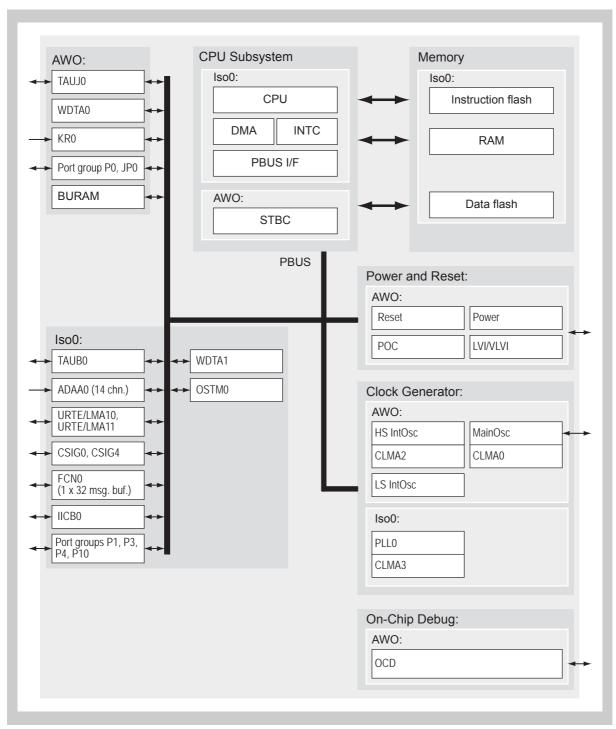

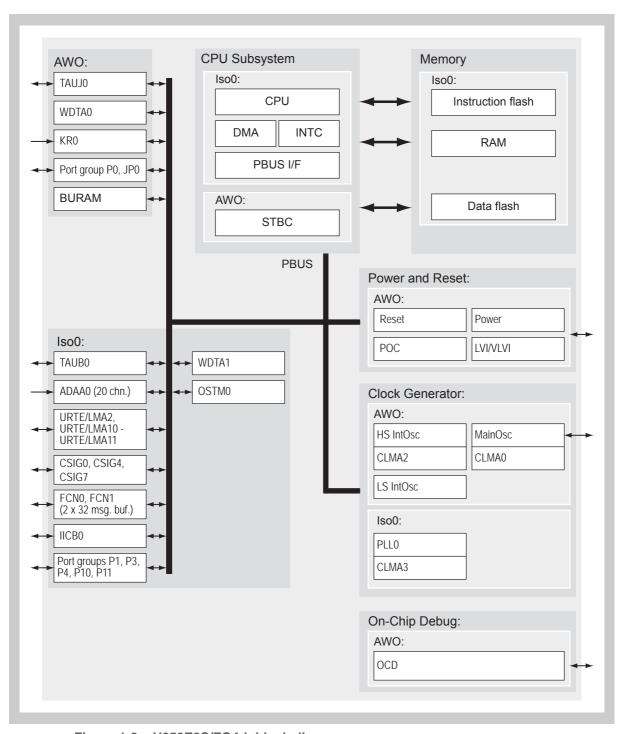

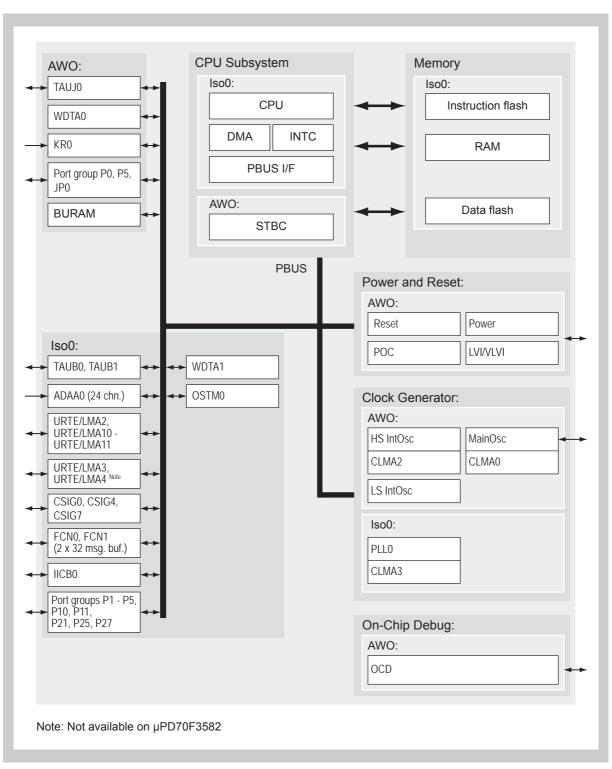

| 1.1     |          | E2/Fx4-L Product Line Overview                        |    |

| 1.2     |          | ed Documents                                          |    |

| 1.3     |          | ring Information                                      |    |

| 1.3     | Orde     |                                                       |    |

| Chapte  | er 2     | Port Functions                                        | 40 |

| 2.1     | V850     | E2/Fx4-L Port Features                                | 40 |

| 2.2     | Over     | view                                                  | 41 |

|         | 2.2.1    | Terms                                                 | 42 |

|         | 2.2.2    | Pin function configuration                            | 43 |

|         | 2.2.3    | Pin data input/output                                 | 45 |

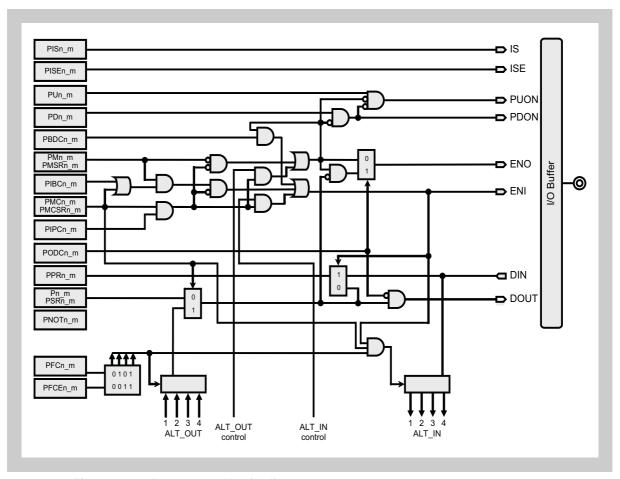

|         | 2.2.4    | Port control logic diagram                            | 47 |

| 2.3     | Port (   | Group Configuration Registers                         | 48 |

|         | 2.3.1    | Writing to protected registers                        |    |

|         | 2.3.2    | Port control registers overview                       |    |

|         | 2.3.3    | Port function configuration registers                 |    |

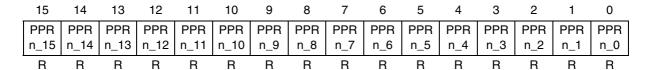

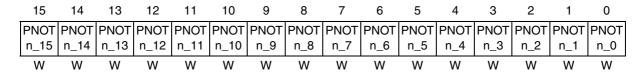

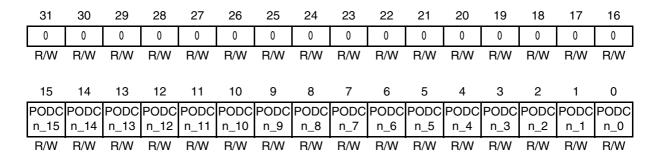

|         | 2.3.4    | Data input/output registers                           |    |

|         | 2.3.5    | Configuration of electrical characteristics registers |    |

| 2.4     |          | E2/Fx4-L Port Groups Configuration                    |    |

|         | 2.4.1    | Port register protection clusters                     |    |

|         | 2.4.2    | Common port functions                                 |    |

|         | 2.4.3    | V850E2S/FE4-L port functions                          |    |

|         | 2.4.4    | V850E2S/FF4-L port functions                          |    |

|         | 2.4.5    | V850E2S/FG4-L port functions                          | 85 |

|        | 2.4.6  | V850E2S/FJ4-L port functions                        | 92  |

|--------|--------|-----------------------------------------------------|-----|

|        | 2.4.7  | Non-port input/output signals                       |     |

|        | 2.4.8  | Alphabetic pin function list                        |     |

|        | 2.4.9  | Port and pin functions in stand-by modes            |     |

|        | 2.4.10 | Port and pin functions during and after reset       |     |

|        | 2.4.11 | Recommended connection of unused pins               |     |

| 2.5    | Port F |                                                     | 110 |

|        | 2.5.1  | Port filters assignment                             | 110 |

|        | 2.5.2  | Port filters clock supply                           | 114 |

|        | 2.5.3  | Port filters reset                                  | 115 |

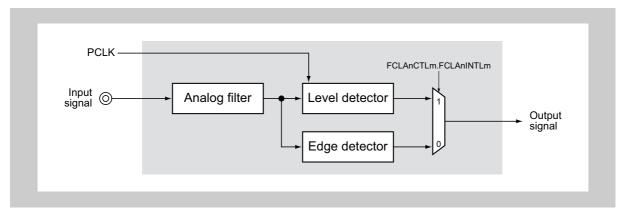

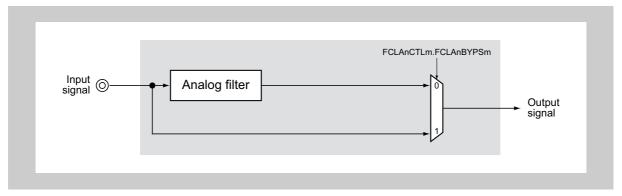

| 2.6    | Port F | Filters Functional Description                      | 116 |

|        | 2.6.1  | Analog filters                                      | 116 |

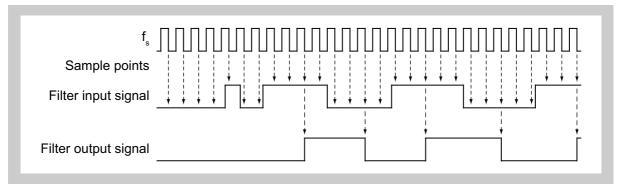

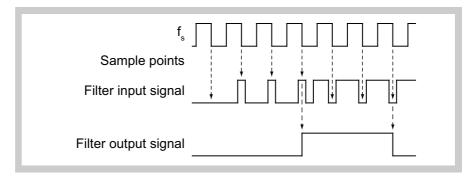

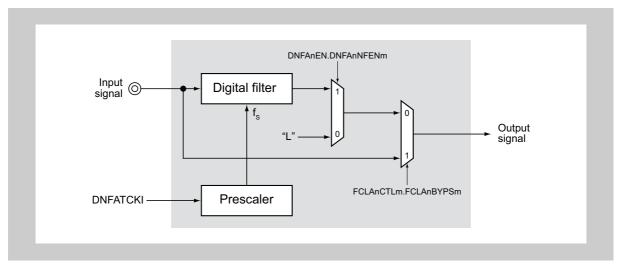

|        | 2.6.2  | Digital filters                                     | 119 |

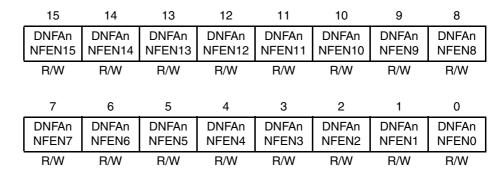

|        | 2.6.3  | Filter control registers                            | 123 |

|        |        |                                                     |     |

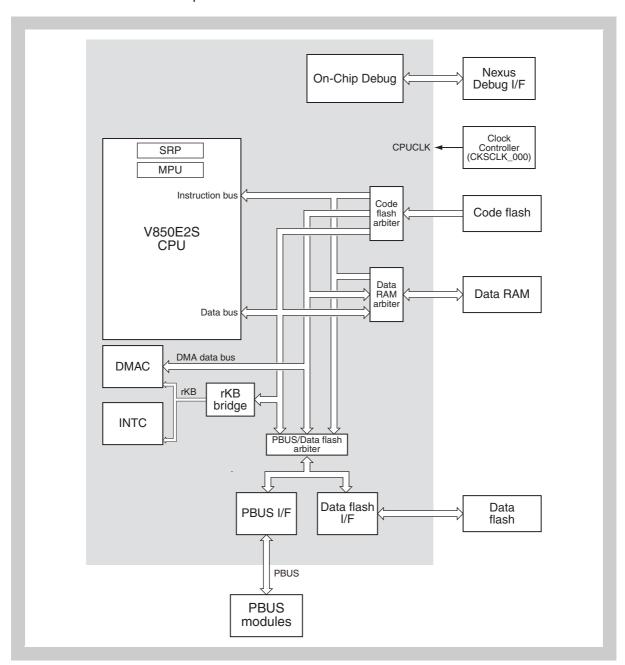

| Chapte | er 3   | CPU System Functions                                | 127 |

| 3.1    | Overv  | /iew                                                | 127 |

| 3.2    | Memo   | pry Protection Unit (MPU)                           | 128 |

| 3.3    | CPU A  | Access Bus Structures and Latencies                 | 129 |

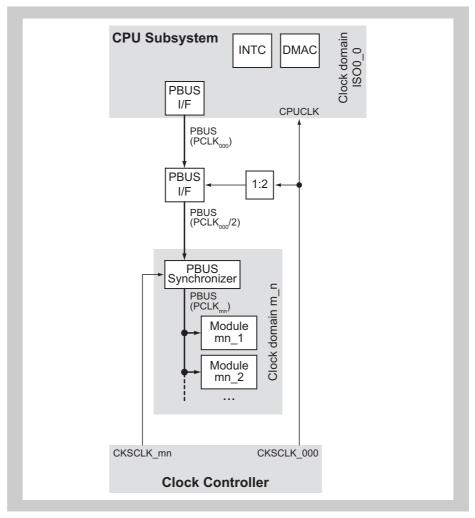

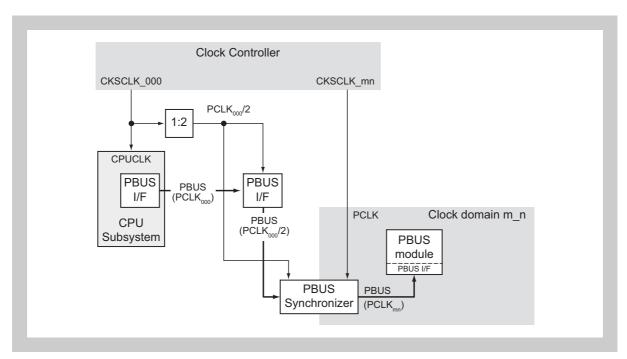

|        | 3.3.1  | CPU Subsystem modules access                        | 129 |

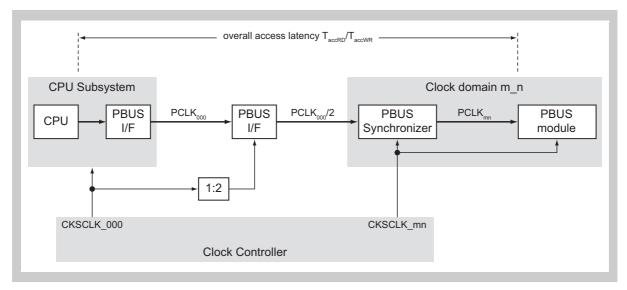

|        | 3.3.2  | PBUS modules access                                 | 130 |

|        | 3.3.3  | PBUS Synchronizer                                   | 133 |

| 3.4    | CPU S  | Subsystem                                           | 136 |

|        | 3.4.1  | Power and clock domain                              | 136 |

|        | 3.4.2  | CPU Subsystem busses overview                       | 137 |

|        | 3.4.3  | CPU Subsystem                                       | 138 |

|        | 3.4.4  | V850E2 system manual                                |     |

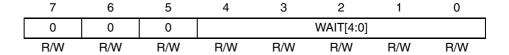

| 3.5    | Data f | flash wait cycle control                            | 141 |

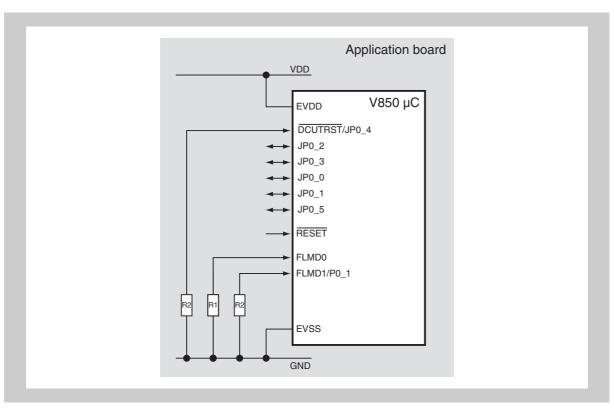

| 3.6    | Opera  | ation modes                                         | 142 |

|        | 3.6.1  | Normal operation mode                               | 142 |

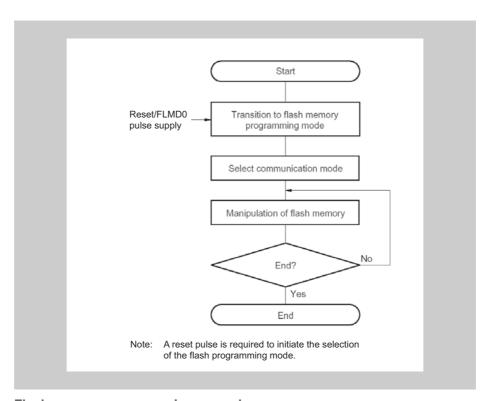

|        | 3.6.2  | Flash programming mode                              | 142 |

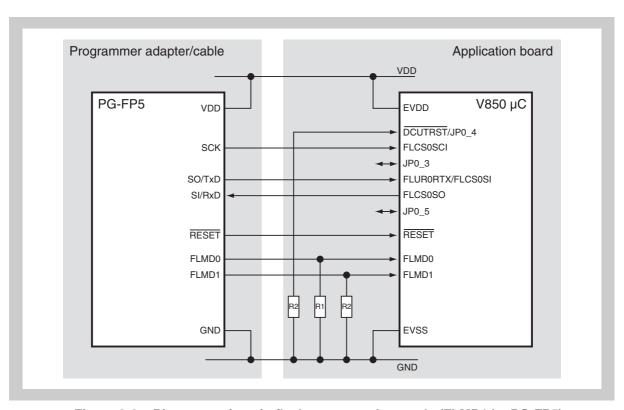

| 3.7    | Mode   | pins and JP0 connections                            | 143 |

|        | 3.7.1  | Normal operation mode                               | 144 |

|        | 3.7.2  | Debug mode                                          | 145 |

|        | 3.7.3  | Flash programming mode                              | 147 |

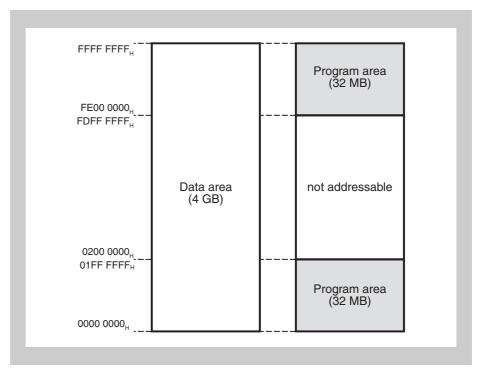

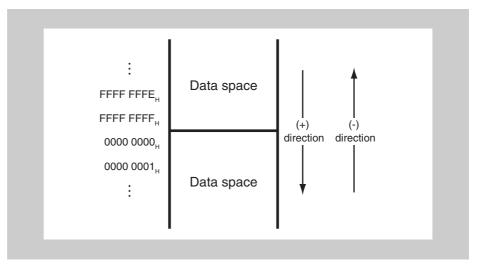

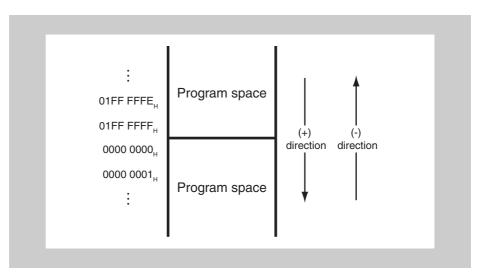

| 3.8    | Addre  | ess Space                                           | 148 |

|        | 3.8.1  | CPU data address and physical program address space | 148 |

|        | 3.8.2  | Program and data space                              |     |

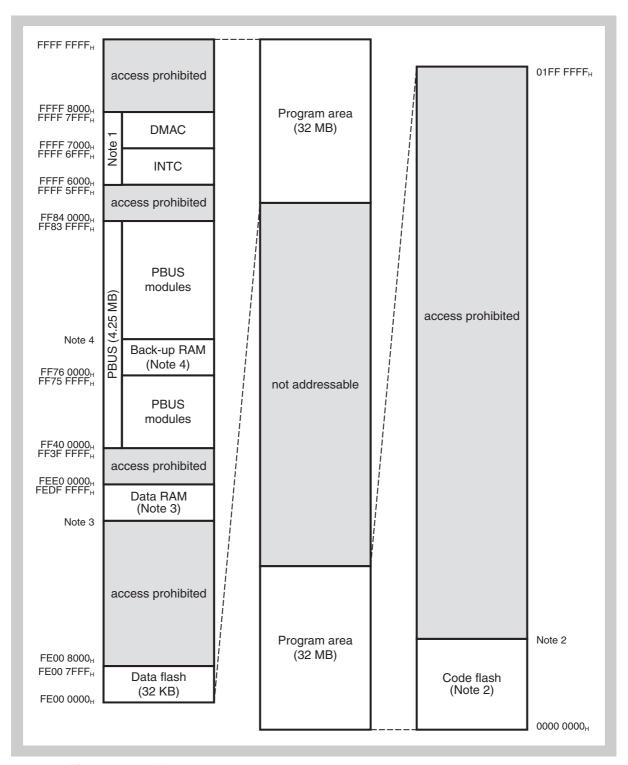

| 3.9    | V850E  | E2/Fx4-L CPU Address Map                            | 150 |

|        | 3.9.1  | DMA address map                                     | 150 |

|        | 3.9.2  | Memory map                                          |     |

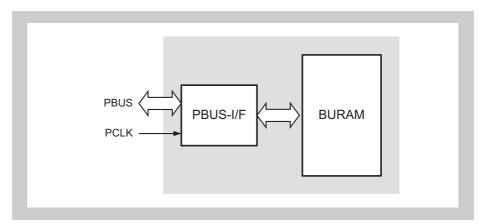

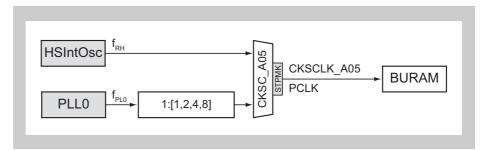

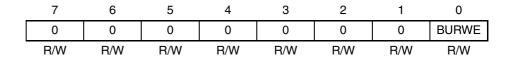

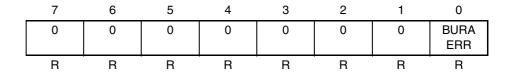

| 3.10   | Back-  | up RAM (BURAM)                                      | 154 |

|        | 3.10.1 | Back-up RAM protection                              | 155 |

| 3.11   | Write  | protected Registers                                 | 157 |

|        | 3.11.1 | Register protection clusters                        |     |

|        | 3.11.2 | Register protection unlock sequence                 |     |

|        | 3.11.3 | Register protection and interrupt/emulation break   |     |

|        | 3.11.4 | V850E2/Fx4-L write protected registers              | 159 |

|        | 3.11.5  | V850E2/Fx4-L Protection registers overview            | 161 |

|--------|---------|-------------------------------------------------------|-----|

|        | 3.11.6  | Control protection clusters registers details         |     |

|        | 3.11.7  | Clock monitors protection cluster registers details   |     |

|        | 3.11.8  | Port protection clusters registers details            | 166 |

|        | 3.11.9  | Self-programming protection cluster registers details | 167 |

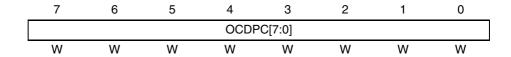

|        | 3.11.10 | OCD control protection cluster registers details      | 168 |

|        | _       |                                                       |     |

| Chapte | r 4     | Interrupt Functions                                   | 169 |

| 4.1    | Excep   | tions and Interrupts                                  | 169 |

| 4.2    | V850E   | 2/Fx4-L Exceptions                                    | 171 |

|        | 4.2.1   | Memory error exceptions MEP                           |     |

|        | 4.2.2   | System error exceptions SYSERR                        | 172 |

|        | 4.2.3   | Code flash error correction                           | 176 |

| 4.3    | V850E   | 2/Fx4-L Interrupt Requests                            | 180 |

|        | 4.3.1   | V850E2/Fx4-L interrupt sources                        | 180 |

|        | 4.3.2   | FE level non-maskable interrupt sharing               | 195 |

| 4.4    | Extern  | nal Interrupts                                        | 197 |

|        | 4.4.1   | Edge Detection Configuration                          | 197 |

|        | 4.4.2   | External interrupts as trigger and wake-up signals    | 198 |

| 4.5    | Interru | ıpt Controller Control Registers                      | 199 |

| 4.6    | Interru | ıpt Acknowledgment and Restoring                      | 209 |

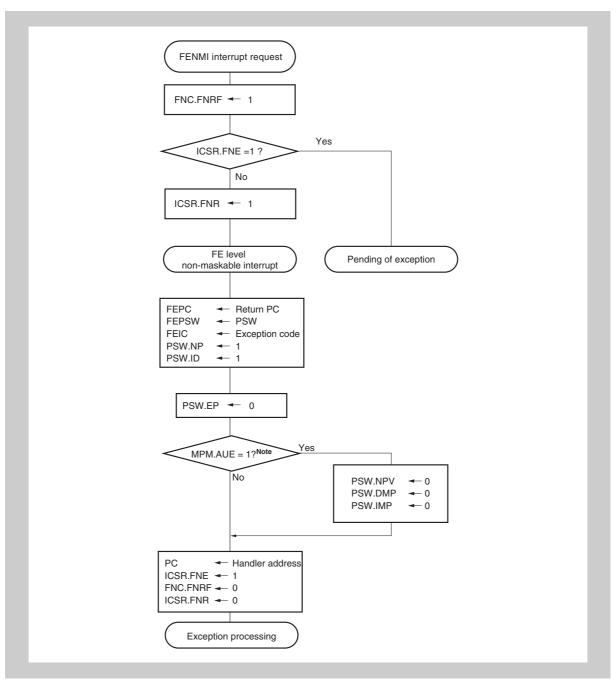

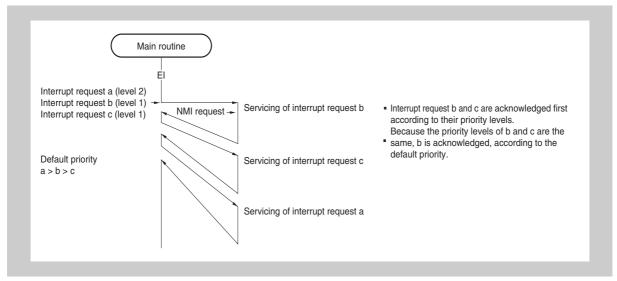

|        | 4. 6. 1 | FE level non-maskable interrupt FENMI                 | 209 |

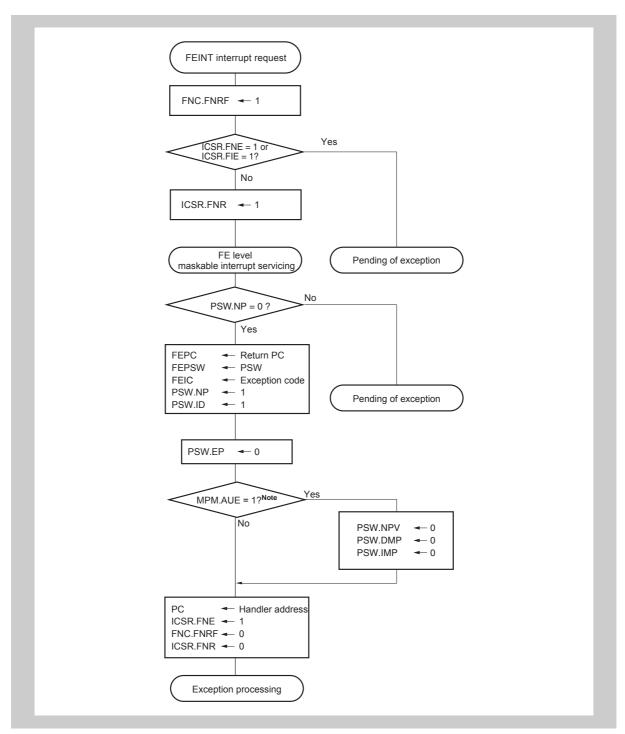

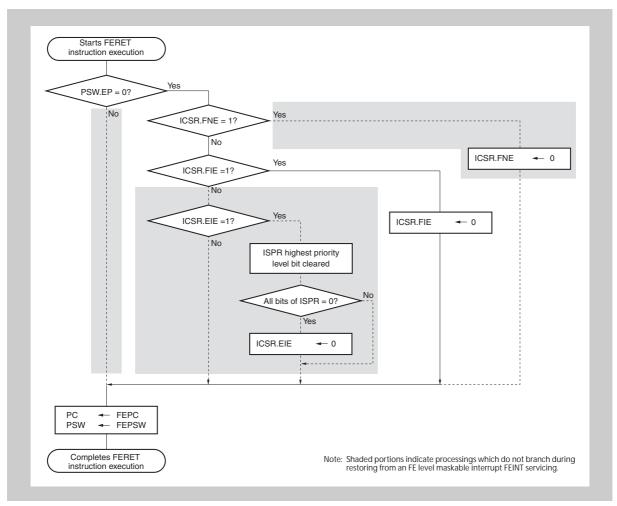

|        | 4. 6. 2 | FE level maskable interrupt FEINT                     | 211 |

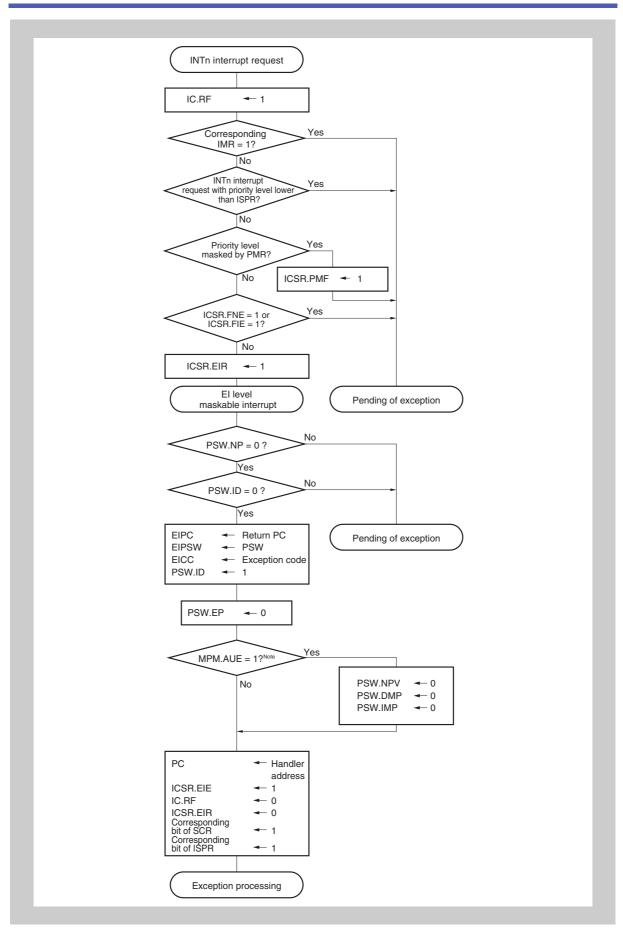

|        | 4. 6. 3 | El level maskable interrupt INTn                      | 213 |

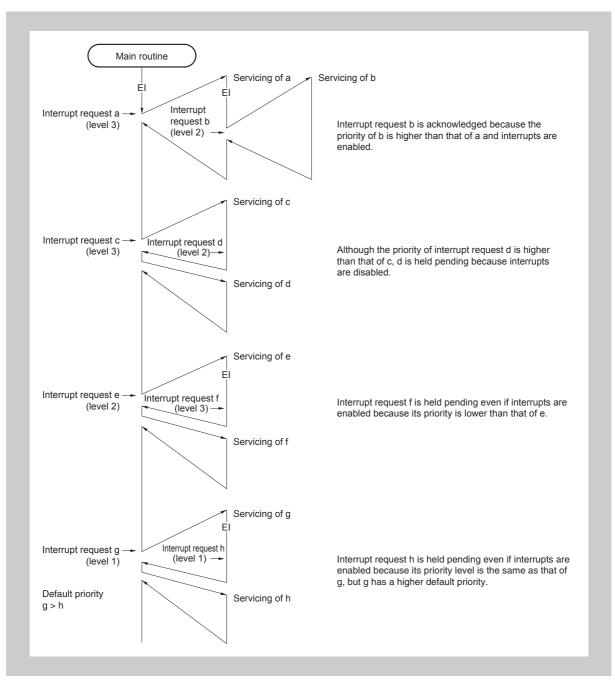

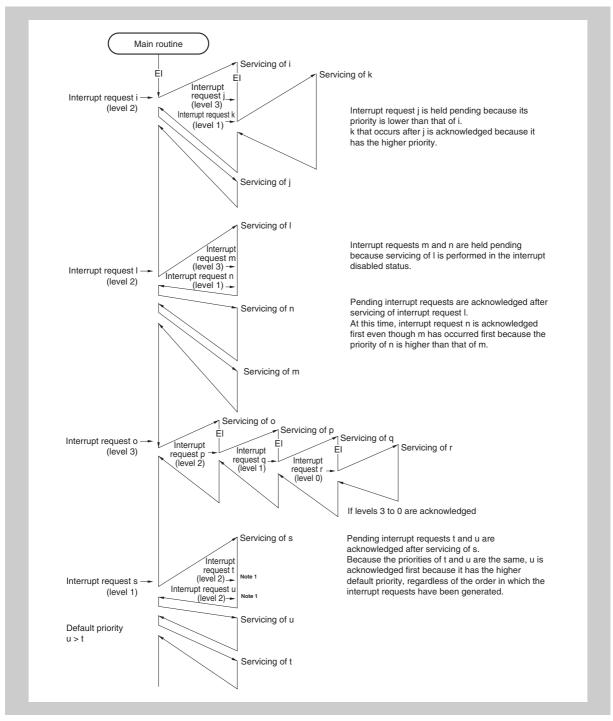

| 4.7    | Interru | ıpt Operation                                         | 216 |

|        | 4. 7. 1 | Mask function of EI level maskable interrupt INTn     | 216 |

|        | 4. 7. 2 | Interrupt priority level judgment                     | 216 |

|        | 4. 7. 3 | Priority mask function                                | 222 |

|        | 4. 7. 4 | Pending interrupt report function                     |     |

|        | 4. 7. 5 | In-service priority clear function                    |     |

| 4.8    | Excep   | tion Handler Address Switching Function               | 223 |

| 01     | . =     |                                                       |     |

| Chapte |         | DMA Controller (DMAC)                                 |     |

| 5.1    | V850E   | 2/Fx4-L DMA Features                                  | 224 |

| 5.2    | Definit | tion of Terms                                         | 226 |

| 5.3    | Gener   | al                                                    | 226 |

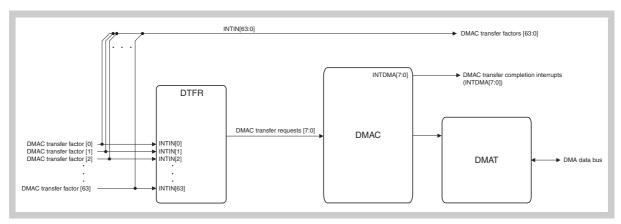

|        | 5.3.1   | DMA Controller (DMAC) function                        | 226 |

|        | 5.3.2   | DMA trigger factor register (DTFR) function           | 227 |

|        | 5.3.3   | DMA access memory map                                 | 227 |

|        | 5.3.4   | Prioritization of channels                            | 227 |

|        | 5.3.5   | Stand-by function                                     | 228 |

| 5.4    | DMAC    | Function                                              | 228 |

|        | 5.4.1   | Features                                              |     |

|        | 5.4.2   | DMAC setting registers                                | 230 |

|        | 5.4.3   | Enabling or disabling writing control registers       | 232 |

| 5.5    | DMA (   | Control Registers                                     |     |

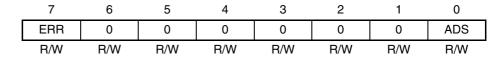

|        | 5.5.1   | DTRC – DMA transfer request control register          |     |

|        | 552     | DSAnt – DMA source address register I                 | 233 |

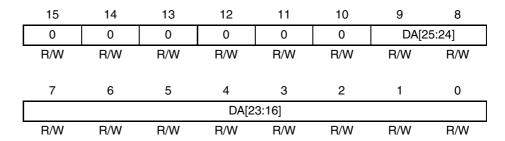

|                   | 5.5.3                                                                                                                                                                       | DSAnH – DMA source address register H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 235                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|                   | 5.5.4                                                                                                                                                                       | DDAnL – DMA destination address register L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 236                                                 |

|                   | 5.5.5                                                                                                                                                                       | DDAnH – DMA destination address register H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 238                                                 |

|                   | 5.5.6                                                                                                                                                                       | DTCn – DMA transfer count register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 239                                                 |

|                   | 5.5.7                                                                                                                                                                       | DTCTn – DMA transfer control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 240                                                 |

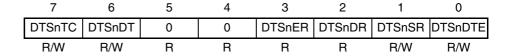

|                   | 5.5.8                                                                                                                                                                       | DTSn – DMA transfer status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 242                                                 |

| 5.6               | DMAC                                                                                                                                                                        | C Function Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 244                                                 |

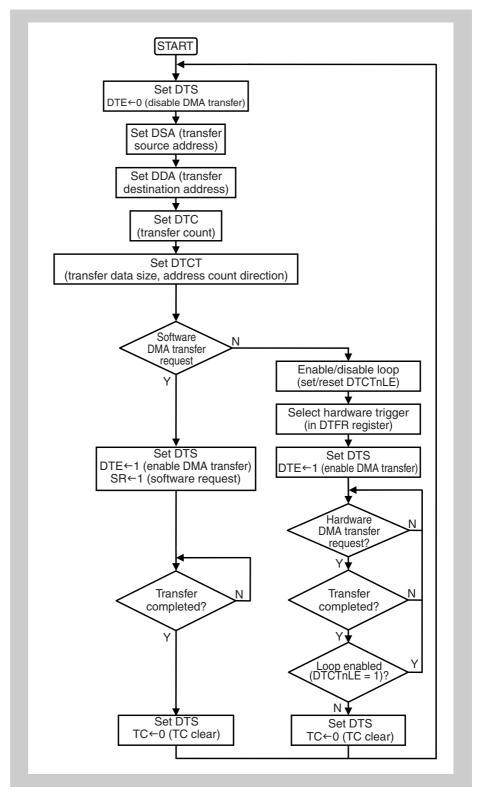

|                   | 5.6.1                                                                                                                                                                       | DMAC transfer setting flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 244                                                 |

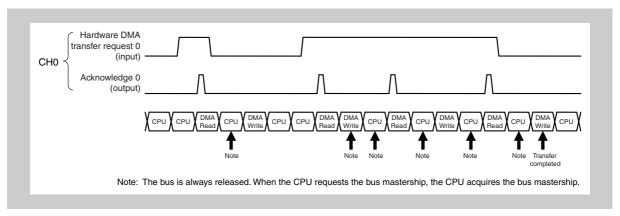

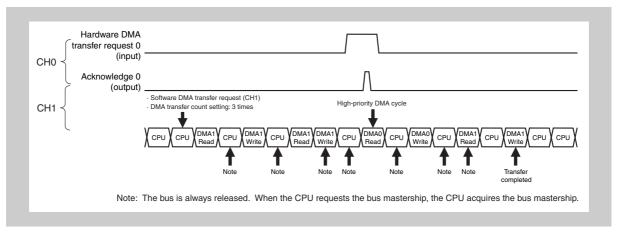

|                   | 5.6.2                                                                                                                                                                       | DMAC transfer modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 245                                                 |

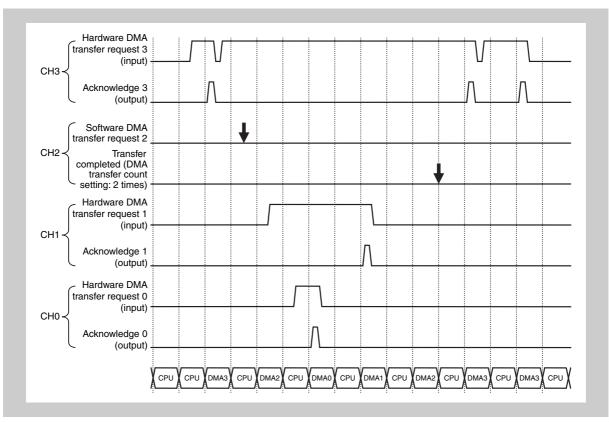

|                   | 5.6.3                                                                                                                                                                       | DMAC channel priority control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 247                                                 |

|                   | 5.6.4                                                                                                                                                                       | Valid DMA transfer request conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 248                                                 |

|                   | 5.6.5                                                                                                                                                                       | Aborting/resuming DMA transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 249                                                 |

|                   | 5.6.6                                                                                                                                                                       | Error response support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 250                                                 |

|                   | 5.6.7                                                                                                                                                                       | Stand-by support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 250                                                 |

| 5.7               | DTFR                                                                                                                                                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 251                                                 |

|                   | 5.7.1                                                                                                                                                                       | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 251                                                 |

| 5.8               | DTFR                                                                                                                                                                        | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 252                                                 |

|                   | 5.8.1                                                                                                                                                                       | DTFRn – DMA trigger factor register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 252                                                 |

|                   | 5.8.2                                                                                                                                                                       | DRQCLR – DMA request clear register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 253                                                 |

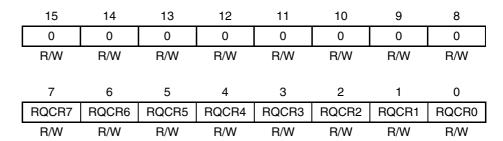

|                   | 5.8.3                                                                                                                                                                       | DRQSTR – DMA request check register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 254                                                 |

|                   | _                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

| Chapte            | er 6                                                                                                                                                                        | Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 255                                                 |

| 6.1               | Code                                                                                                                                                                        | Flash Memory Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 256                                                 |

| <b>U.</b> 1       |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

| <b>0.1</b>        | 6.1.1                                                                                                                                                                       | Code flash memory features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |

| <b>V.</b> 1       |                                                                                                                                                                             | Code flash memory features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 256                                                 |

| 0.1               | 6.1.1                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 256                                                 |

| 6.2               | 6.1.1<br>6.1.2<br>6.1.3                                                                                                                                                     | Code flash memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 256<br>256                                          |

| -                 | 6.1.1<br>6.1.2<br>6.1.3                                                                                                                                                     | Code flash memory map  Data flash memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 256<br>256<br>260                                   |

| -                 | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1                                                                                                                             | Code flash memory map  Data flash memory map  Flash Memory functional Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 256<br>256<br>259<br>260                            |

| 6.2               | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1                                                                                                                             | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite                                                                                                                                                                                                                                                                                                                                                                                                           | 256 256 259 262 263                                 |

| 6.2               | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b>                                                                                                              | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite.  Flash Memory                                                                                                                                                                                                                                                                                                                                                                                            | 256 259 262 263 263                                 |

| 6.2               | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 1<br>6.3.1<br>6.3.2                                                                                          | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite  Flash Memory  Data flash memory features                                                                                                                                                                                                                                                                                                                                                                 | 256 259 262 263 263                                 |

| 6.2<br>6.3        | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 1<br>6.3.1<br>6.3.2                                                                                          | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite  Flash Memory  Data flash memory features  Data flash reading and writing                                                                                                                                                                                                                                                                                                                                 | 256 259 262 263 263 263                             |

| 6.2<br>6.3        | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b><br>6.3.1<br>6.3.2<br><b>Flash</b>                                                                            | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite  Flash Memory  Data flash memory features  Data flash reading and writing.  Programming with Flash Programmer                                                                                                                                                                                                                                                                                             | 256 259 262 263 263 264 264                         |

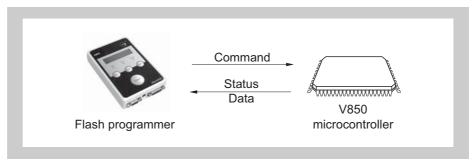

| 6.2<br>6.3        | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 1<br>6.3.1<br>6.3.2<br><b>Flash</b><br>6.4.1                                                                 | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite  Flash Memory  Data flash memory features  Data flash reading and writing.  Programming with Flash Programmer  Programming environment                                                                                                                                                                                                                                                                    | 256 259 260 262 263 263 264 264                     |

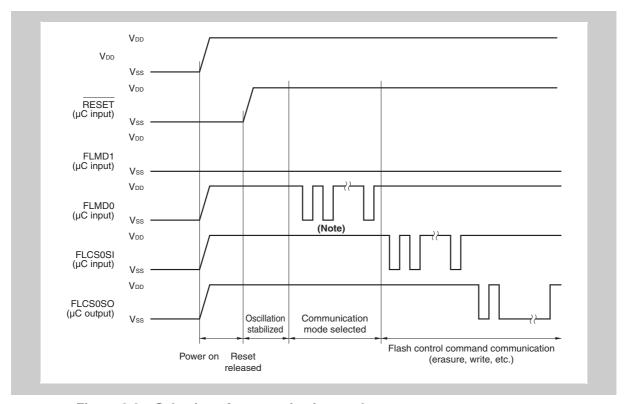

| 6.2<br>6.3        | 6.1.1<br>6.1.2<br>6.1.3<br>Code<br>6.2.1<br>Data<br>6.3.1<br>6.3.2<br>Flash<br>6.4.1<br>6.4.2                                                                               | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite  Flash Memory  Data flash memory features  Data flash reading and writing.  Programming with Flash Programmer  Programming environment  Communication modes                                                                                                                                                                                                                                               | 256 256 262 263 263 264 265 265                     |

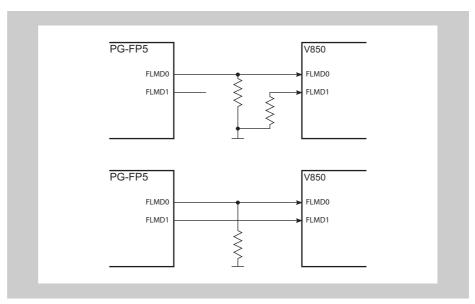

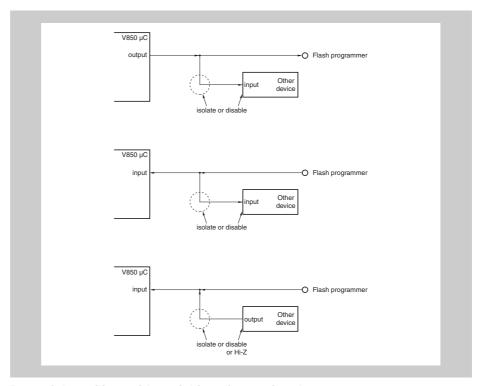

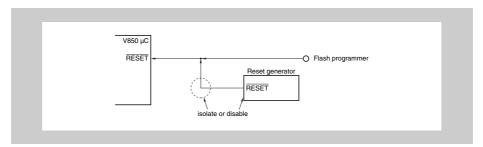

| 6.2<br>6.3        | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 1<br>6.3.1<br>6.3.2<br><b>Flash</b><br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4                                      | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite.  Flash Memory  Data flash memory features  Data flash reading and writing.  Programming with Flash Programmer  Programming environment  Communication modes  Pin connection with flash programmer PG-FP5                                                                                                                                                                                                 | 256 256 262 263 263 264 264 265 266                 |

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 1<br>6.3.1<br>6.3.2<br><b>Flash</b><br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4                                      | Code flash memory map Data flash memory map  Flash Memory functional Outline Code flash memory erasure and rewrite.  Flash Memory Data flash memory features Data flash reading and writing.  Programming with Flash Programmer Programming environment Communication modes Pin connection with flash programmer PG-FP5 Flash memory programming control                                                                                                                                                                       | 256 259 260 263 263 264 264 265 265 267             |

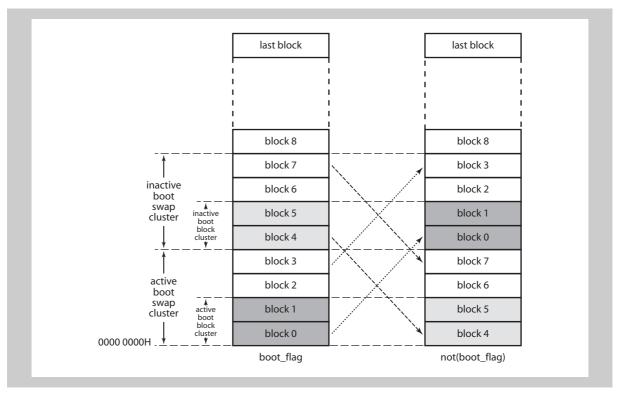

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br>Code<br>6.2.1<br>Data<br>6.3.1<br>6.3.2<br>Flash<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>Code                                                     | Code flash memory map  Data flash memory map  Flash Memory functional Outline Code flash memory erasure and rewrite  Flash Memory Data flash memory features Data flash reading and writing.  Programming with Flash Programmer Programming environment Communication modes Pin connection with flash programmer PG-FP5 Flash memory programming control  Flash Self-Programming                                                                                                                                               | 256 259 259 260 263 263 264 264 266 267 274         |

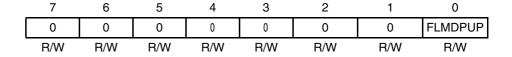

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br>Code<br>6.2.1<br>Data  <br>6.3.1<br>6.3.2<br>Flash<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>Code<br>6.5.1                                          | Code flash memory map  Data flash memory map  Flash Memory functional Outline  Code flash memory erasure and rewrite.  Flash Memory  Data flash memory features  Data flash reading and writing.  Programming with Flash Programmer  Programming environment  Communication modes  Pin connection with flash programmer PG-FP5  Flash memory programming control  Flash Self-Programming  Self-Programming enable                                                                                                              | 256 259 259 260 263 263 264 264 265 267 275         |

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br>Code<br>6.2.1<br>Data<br>6.3.1<br>6.3.2<br>Flash<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>Code<br>6.5.1<br>6.5.2                                   | Code flash memory map  Data flash memory map  Flash Memory functional Outline Code flash memory erasure and rewrite  Flash Memory Data flash memory features Data flash reading and writing.  Programming with Flash Programmer  Programming environment  Communication modes Pin connection with flash programmer PG-FP5 Flash memory programming control  Flash Self-Programming  Self-Programming enable Self-Programming library functions                                                                                 | 256 259 259 260 263 263 263 264 265 265 267 276     |

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br><b>Code</b><br>6.2.1<br><b>Data</b> 6.3.1<br>6.3.2<br><b>Flash</b><br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br><b>Code</b><br>6.5.1<br>6.5.2<br>6.5.3 | Code flash memory map  Data flash memory map  Flash Memory functional Outline Code flash memory erasure and rewrite.  Flash Memory Data flash memory features Data flash reading and writing.  Programming with Flash Programmer Programming environment Communication modes Pin connection with flash programmer PG-FP5 Flash memory programming control  Flash Self-Programming Self-Programming enable Self-Programming library functions Self-Programming internal RAM occupancy                                           | 256 256 259 262 263 263 264 264 265 267 275 276 276 |

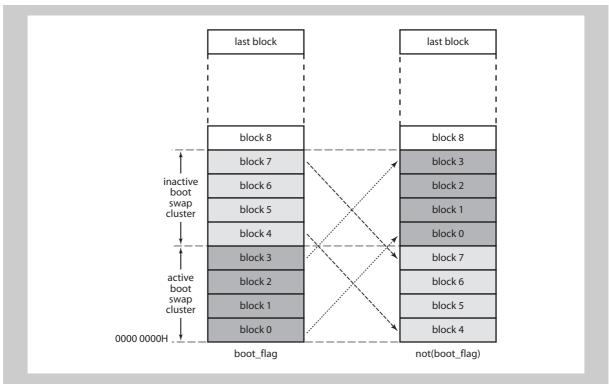

| 6.2<br>6.3<br>6.4 | 6.1.1<br>6.1.2<br>6.1.3<br>Code<br>6.2.1<br>Data<br>6.3.1<br>6.3.2<br>Flash<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>Code<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5        | Code flash memory map Data flash memory map Flash Memory functional Outline Code flash memory erasure and rewrite Flash Memory Data flash memory features Data flash reading and writing. Programming with Flash Programmer Programming environment Communication modes Pin connection with flash programmer PG-FP5 Flash memory programming control Flash Self-Programming Self-Programming enable Self-Programming library functions Self-Programming internal RAM occupancy Secure Self-Programming (boot cluster swapping) | 256 259 259 260 263 263 263 264 264 265 267 276 276 |

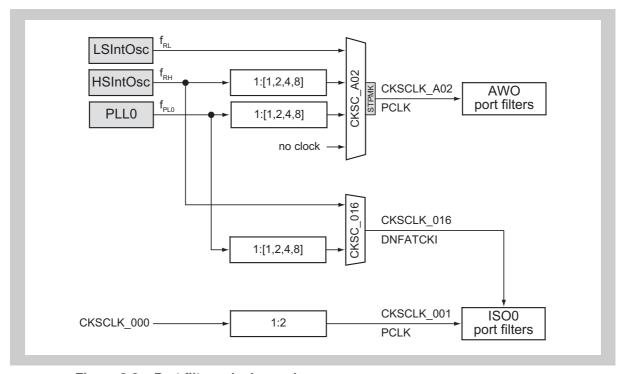

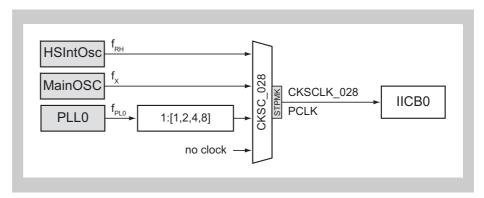

| Chapte | er 7  | Clock Controller                                                           | 284     |

|--------|-------|----------------------------------------------------------------------------|---------|

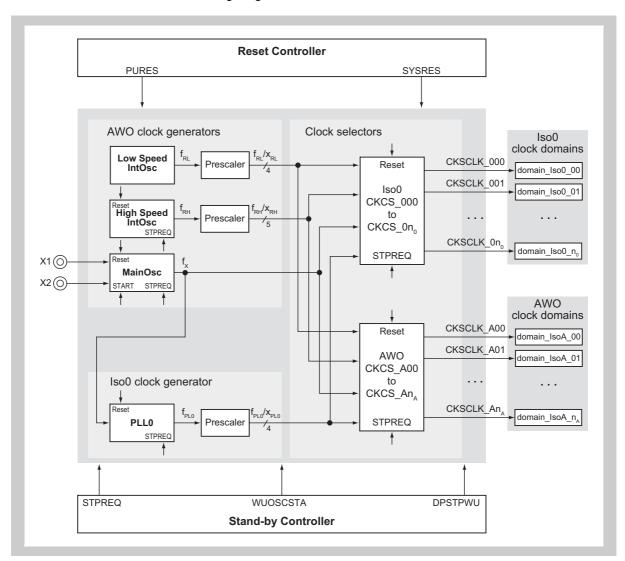

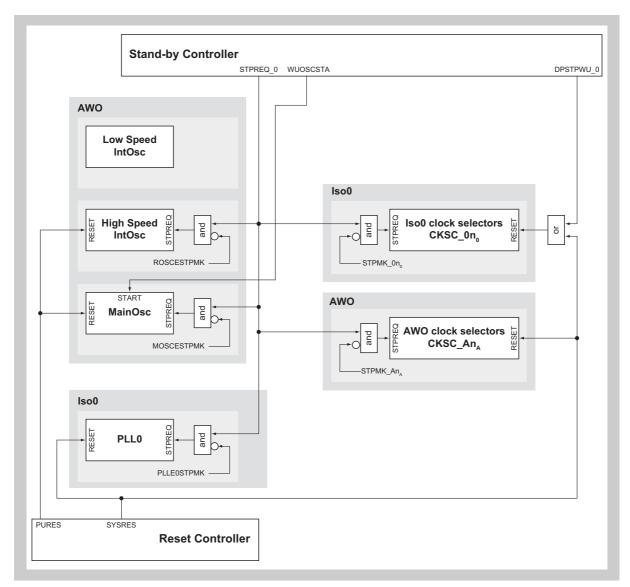

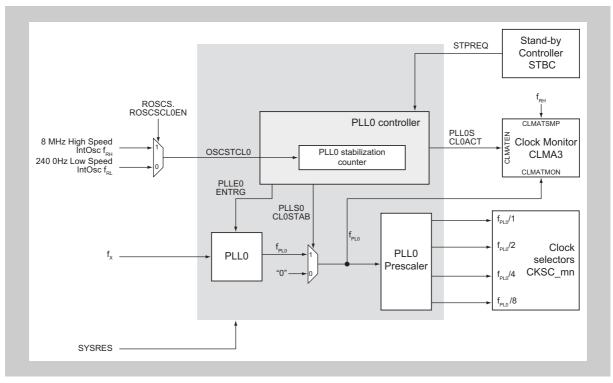

| 7.1    | Clock | Controller Overview                                                        | 284     |

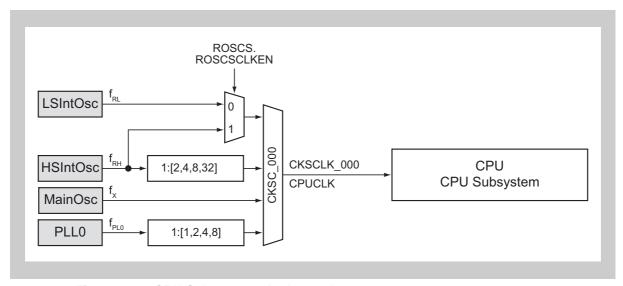

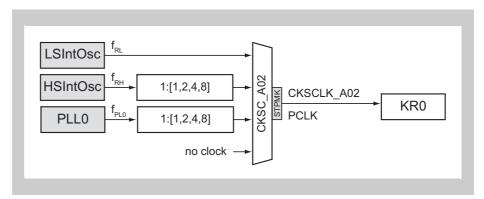

| 7.2    | Gene  | ral Description of Clock Generation and Control                            | 287     |

|        | 7.2.1 | Clock generators                                                           |         |

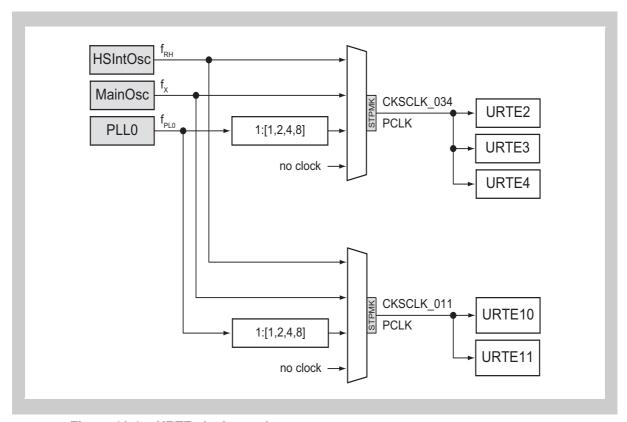

|        | 7.2.2 | Clock selectors                                                            | 291     |

| 7.3    | Clock | Generators                                                                 | 293     |

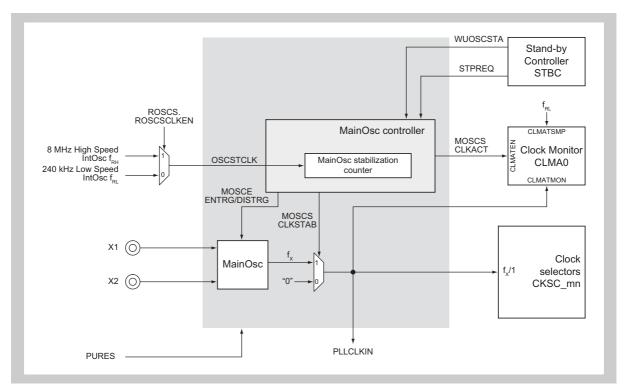

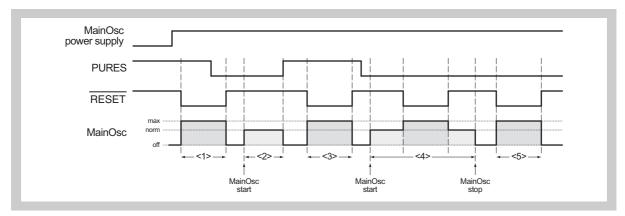

|        | 7.3.1 | Main Oscillator (MainOsc) clock generator                                  | 293     |

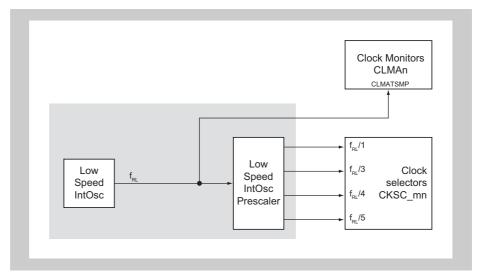

|        | 7.3.2 | Low Speed Internal Oscillator (Low Speed IntOsc) clock generator           | 296     |

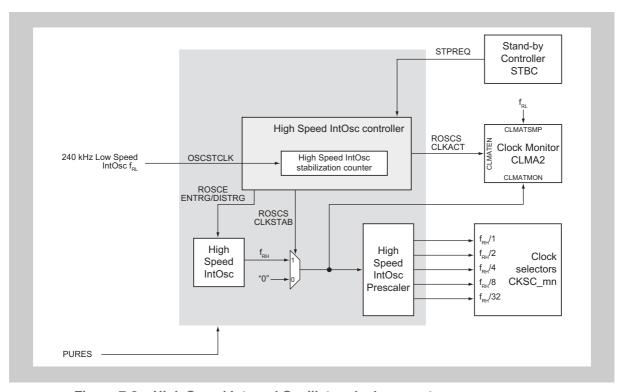

|        | 7.3.3 | High Speed Internal Oscillator (High Speed IntOsc) clock generator         | 297     |

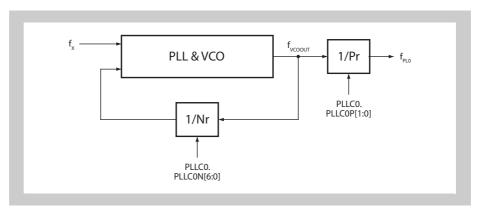

|        | 7.3.4 | Phase-Locked Loop (PLL) clock generators                                   | 300     |

| 7.4    | Clock | Selection                                                                  | 303     |

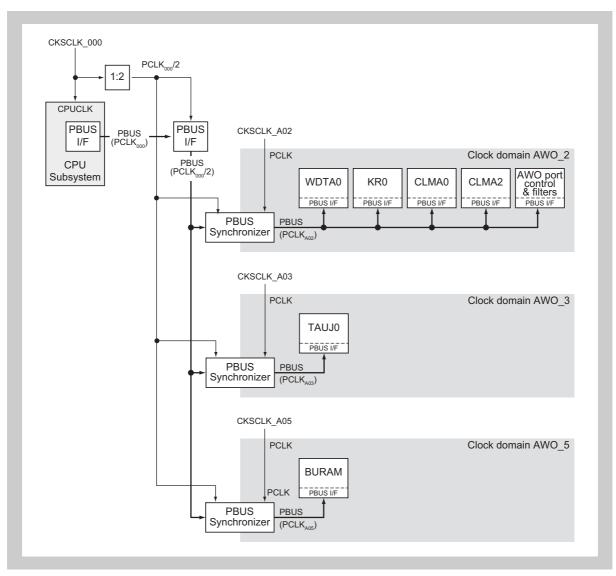

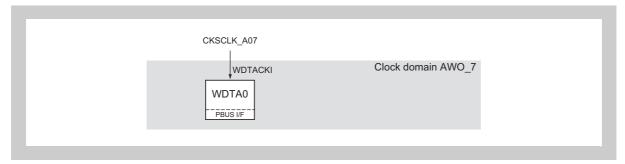

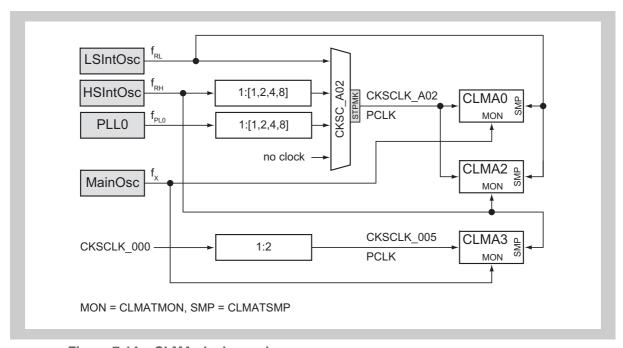

|        | 7.4.1 | Clock domains of Always-On-Area                                            | 306     |

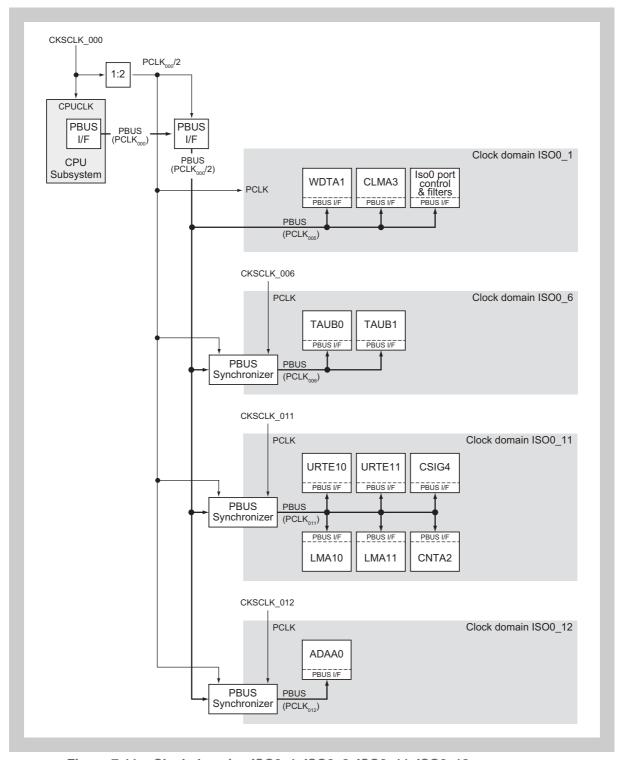

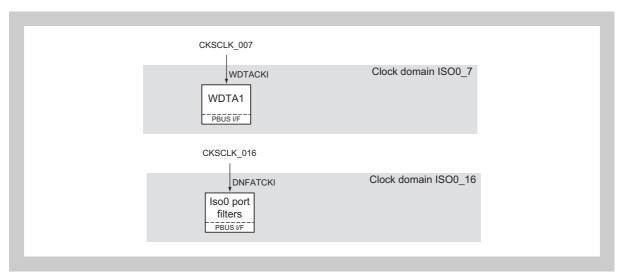

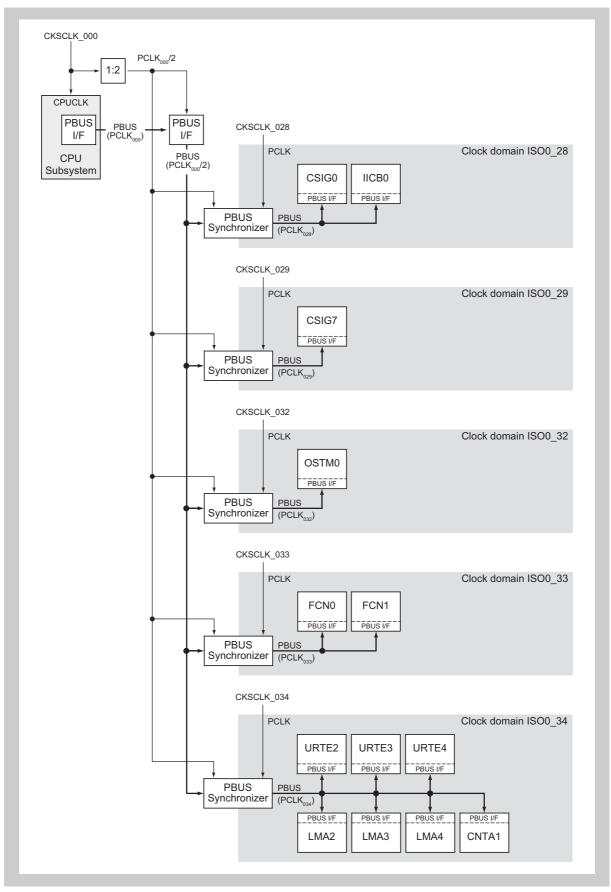

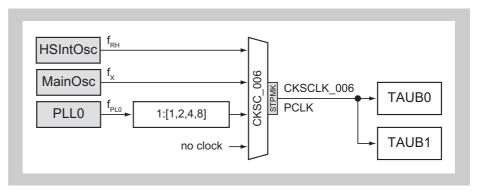

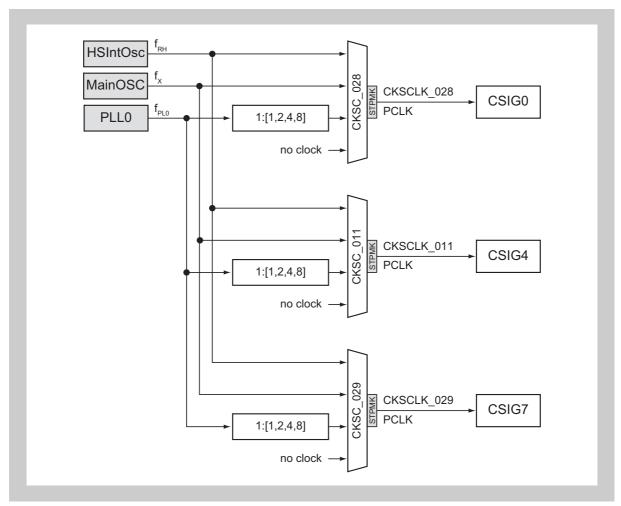

|        | 7.4.2 | Clock domains of Isolated–Area-0                                           | 308     |

| 7.5    | Clock | Domain Figures                                                             | 314     |

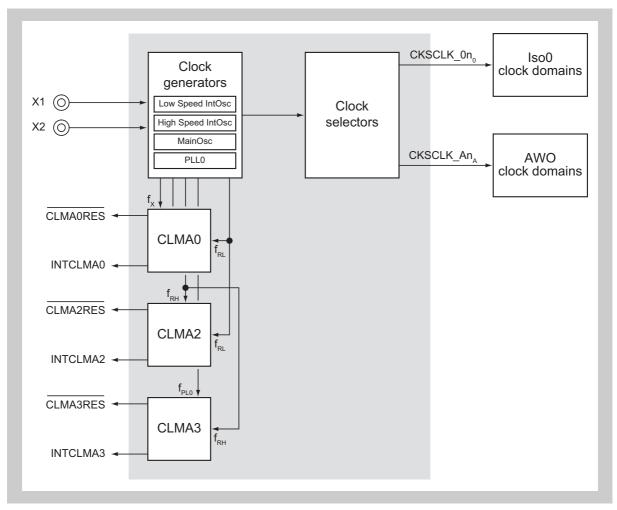

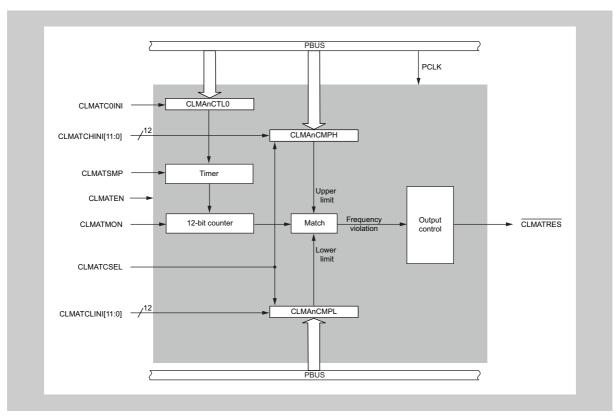

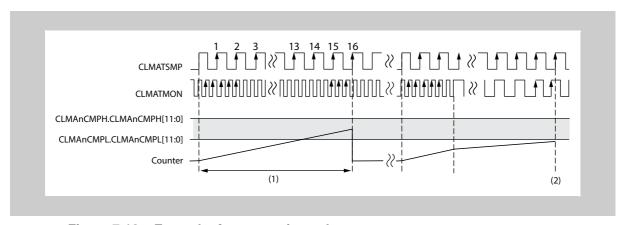

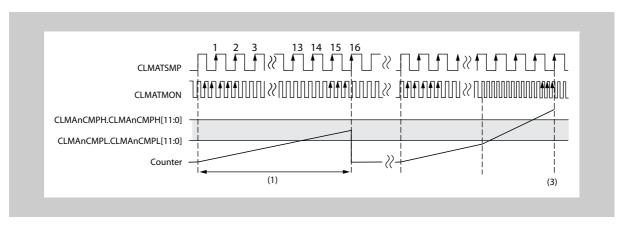

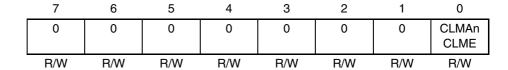

| 7.6    | Clock | Monitor A (CLMA)                                                           | 319     |

|        | 7.6.1 | V850E2/Fx4-L CLMA features                                                 |         |

|        | 7.6.2 | CLMA enable and start-up options                                           |         |

|        | 7.6.3 | Functional Overview                                                        |         |

|        | 7.6.4 | Functional Description                                                     |         |

|        | 7.6.5 | Clock Monitor registers                                                    | 328     |

| 7.7    | Clock | Controller Registers                                                       | 333     |

|        | 7.7.1 | Writing to protected registers                                             | 333     |

|        | 7.7.2 | Clock Controller registers overview                                        | 333     |

|        | 7.7.3 | Clock generators registers                                                 | 335     |

|        | 7.7.4 | Clock selector control register                                            | 347     |

| Chapte | er 8  | Stand-by Controller (STBC)                                                 | 351     |

| 8.1    |       | E2/Fx4-L Stand-by Controller Features                                      |         |

| 8.2    |       | I-by Controller functions                                                  |         |

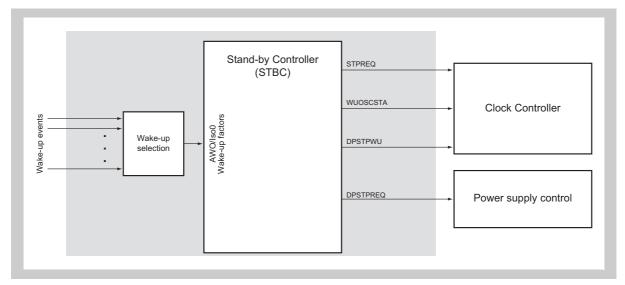

| 0.2    | 8.2.1 | Stand-by Controller signal connections                                     |         |

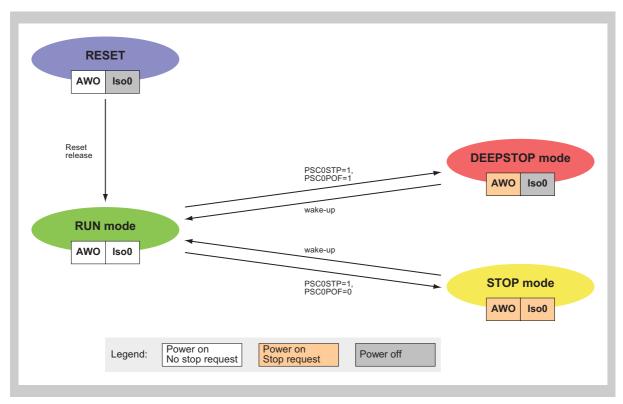

|        | 8.2.2 | Stand-by modes control                                                     |         |

|        | 8.2.3 | Stand-by modes overview                                                    |         |

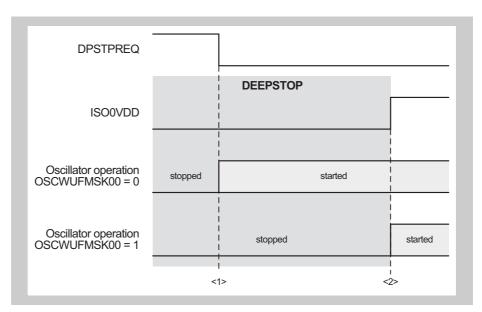

|        | 8.2.4 | Clock generators in stand-by                                               |         |

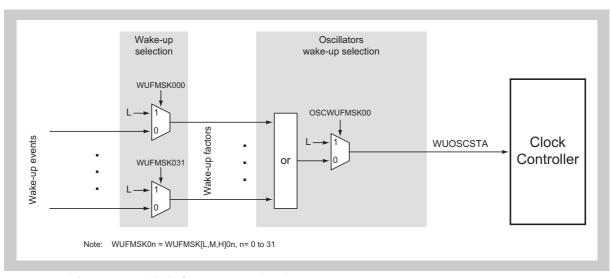

|        | 8.2.5 | Wake-up                                                                    |         |

|        | 8.2.6 | I/O buffer control                                                         |         |

|        | 8.2.7 | Mode transitions                                                           | 365     |

| 8.3    | Stand | I-by modes entry and exit example flows                                    | 366     |

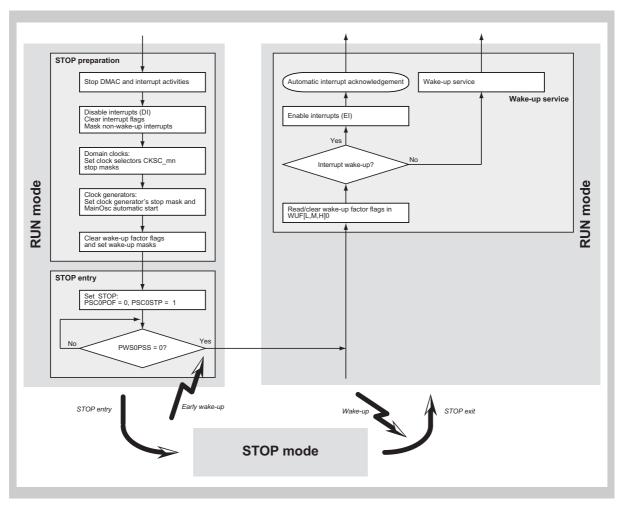

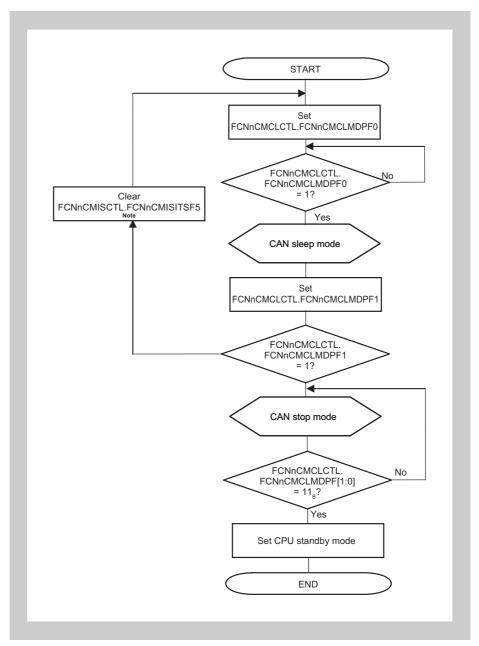

|        | 8.3.1 | STOP mode                                                                  | 367     |

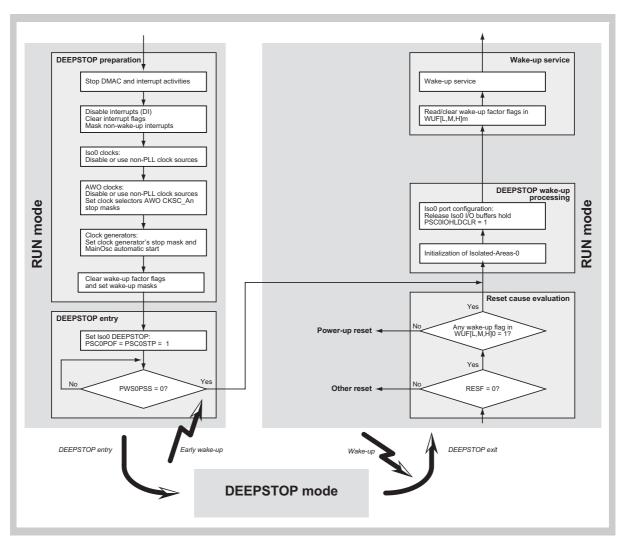

|        | 8.3.2 | DEEPSTOP mode                                                              | 370     |

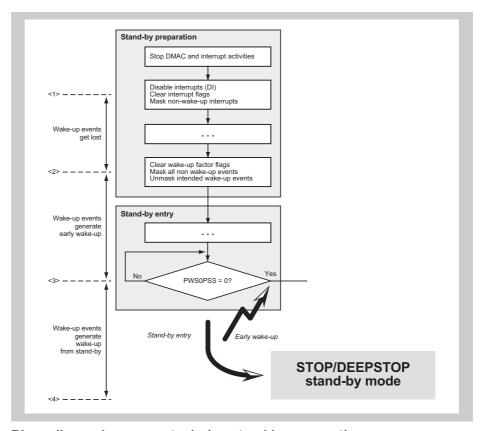

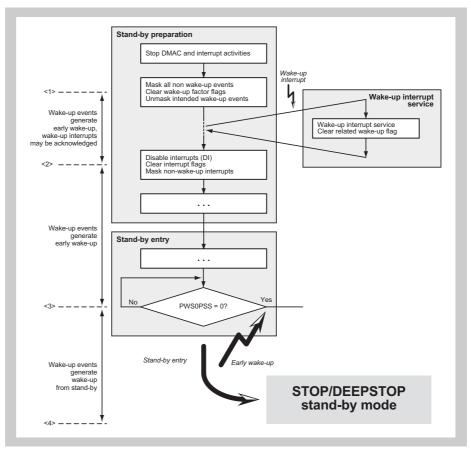

|        | 8.3.3 | Application hint: Handling of wake-up events during stand-by mode prep 373 | aration |

| 8.4    | Stanc | I-by Controller Registers                                                  | 376     |

| J      | 8.4.1 | Writing to protected registers                                             |         |

|        | 8.4.2 | Stand-by Controller registers overview                                     |         |

|        | 8.4.3 | Stand-by Controller control registers details                              |         |

|        | 8.4.4 | Wake-up factor controller registers details                                |         |

|        | 8.4.5 | Oscillator wake-up registers details                                       |         |

| Chapte | r 9              | Wake-up Sequencer (SEQ)                            | 384 |

|--------|------------------|----------------------------------------------------|-----|

| 9.1    | V850E            | E2/Fx4-L SEQ Features                              | 384 |

| 9.2    | I/O sig          | gnals port configuration                           | 387 |

| 9.3    |                  | ional Overview                                     |     |

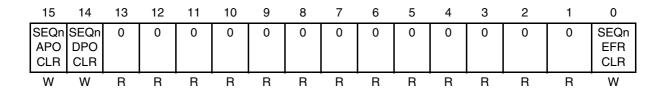

| 9.4    |                  | ional description                                  |     |

|        | 9.4.1            | Mode selection                                     |     |

|        | 9.4.2            | Starting and stopping the sequencer                |     |

|        | 9.4.3            | Digital input signals selection                    | 389 |

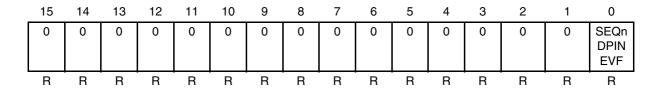

|        | 9.4.4            | Event flag                                         | 390 |

|        | 9.4.5            | CPU processing acceleration                        | 390 |

|        | 9.4.6            | Operation clocks                                   | 391 |

|        | 9.4.7            | Wake-up Sequencer setup                            | 392 |

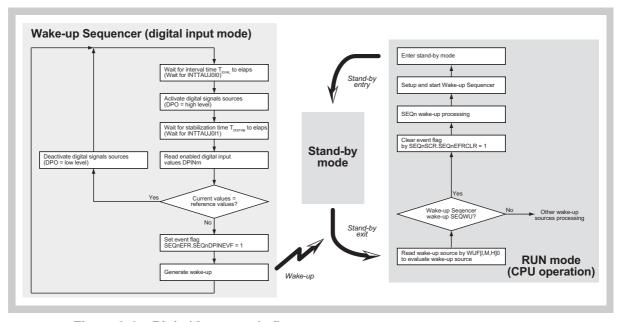

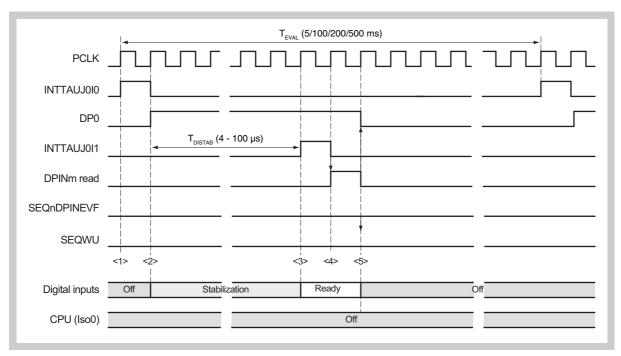

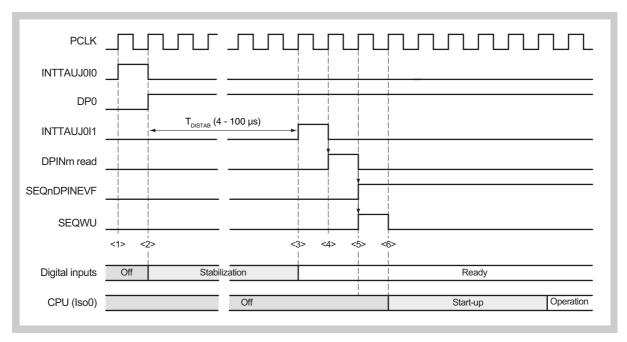

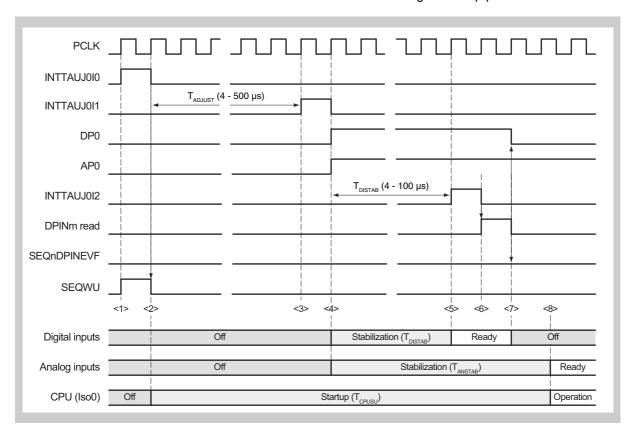

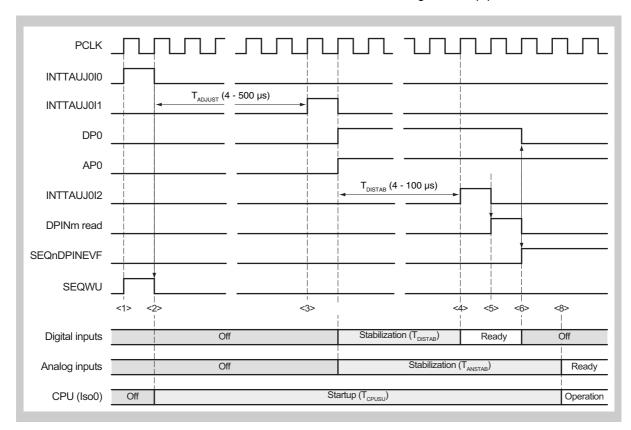

|        | 9.4.8            | Digital input mode                                 |     |

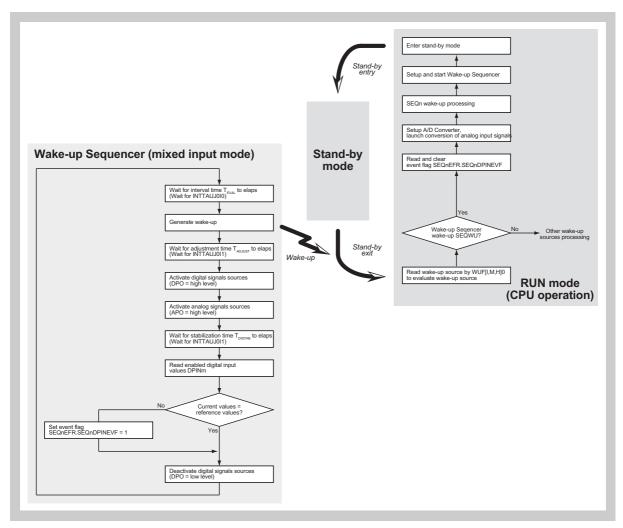

|        | 9.4.9            | Mixed input mode                                   |     |

| 9.5    |                  | -up Sequencer registers                            |     |

|        | 9.5.1            | Wake-up Sequencer registers overview               |     |

|        | 9.5.2            | Wake-up Sequencer registers details                |     |

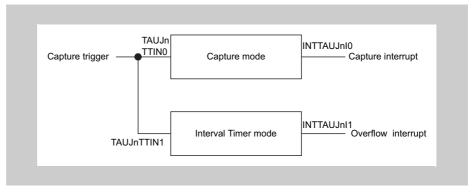

| 9.6    | Wake             | -up Sequencer specific operation of TAUJ0          | 410 |

|        | 9.6.1            | TAUJ0 operation overview                           |     |

|        | 9.6.2            | TAUJ0 register settings                            | 414 |

| Chanta | <b>410</b>       | Code Drotostian and Cogusty                        | 400 |

| Chapte |                  | Code Protection and Security                       |     |

| 10.1   |                  | riew                                               |     |

| 10.2   |                  | Programmer and Self-Programming Protection         |     |

| 10.3   | On-Cl            | hip Debug Interface Protection                     | 422 |

|        | 10.3.1           | On-Chip Debug enable flag                          |     |

|        | 10.3.2           | On-Chip Debug ID code                              |     |

|        | 10.3.3           | On-Chip Debug protection levels summary            |     |

|        | 10.3.4           | On-Chip Debug control registers                    | 424 |

| Chapte | r 11             | Reset Controller                                   | 407 |

| •      |                  |                                                    |     |

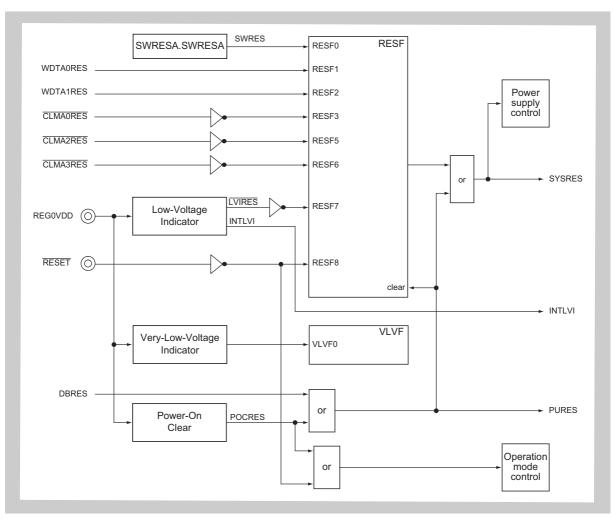

| 11.1   |                  | ional Overview                                     |     |

| 11.2   |                  | ional Description                                  |     |

|        | 11.2.1           | Reset flags                                        |     |

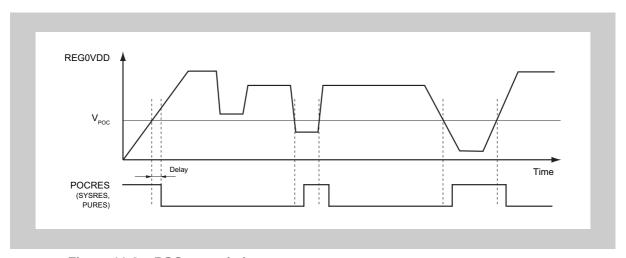

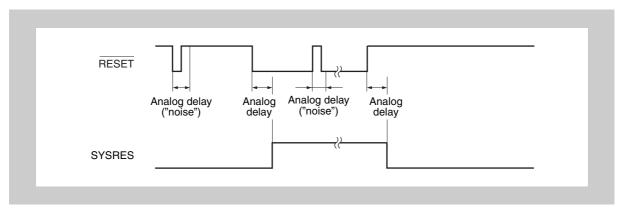

|        | 11.2.2           | Power-On Clear (POC)                               |     |

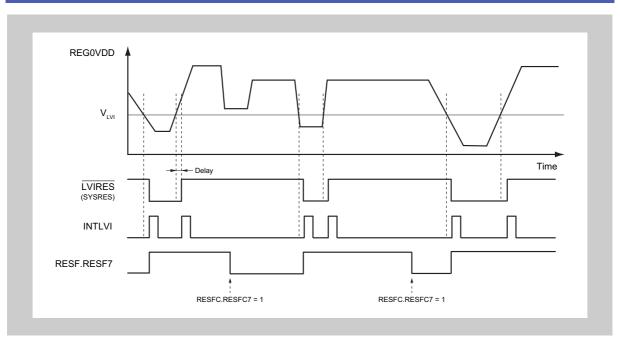

|        | 11.2.3           | Low-Voltage Indicator (LVI)                        |     |

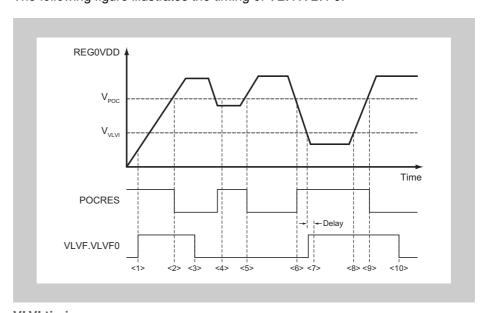

|        | 11.2.4<br>11.2.5 | Very-Low-Voltage Indicator (VLVI)                  |     |

|        | 11.2.6           | Watchdog Timers reset (WDTAnRES)                   |     |

|        | 11.2.7           | Software reset (SWRES)                             |     |

|        | 11.2.8           | Clock Monitors reset (CLMAnRES)                    |     |

|        | 11.2.9           | Debugger reset (DBRES)                             |     |

| 11.3   |                  | Controller Registers                               |     |

|        | 11.3.1           | Writing to protected registers                     |     |

|        | 11.3.2           | Reset Controller registers overview                |     |

|        | 11.3.3           | Reset Controller general control registers details |     |

|        | 11.3.4           | Software reset control registers details           |     |

|         | 11.3.5           | Low-Voltage Indicator reset control registers               | 445 |

|---------|------------------|-------------------------------------------------------------|-----|

|         | 11.3.6           | Very Low-Voltage flag control registers                     | 446 |

| Chapter | 12               | OS Timer (OSTM)                                             | 448 |

| 12.1    |                  | 2/Fx4-L OSTM Features                                       |     |

| 12.1    |                  | ional Overview                                              |     |

| 12.2    |                  | ional Description                                           |     |

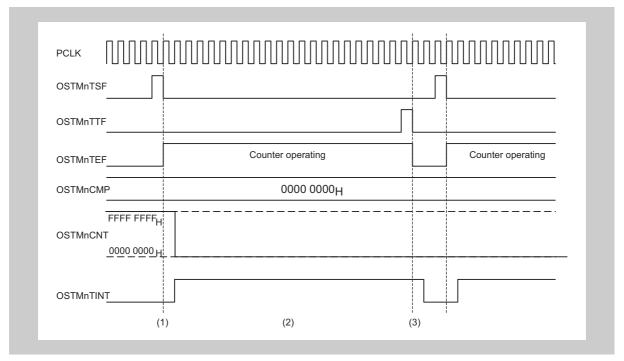

| 12.3    | 12.3.1           | Count clock                                                 |     |

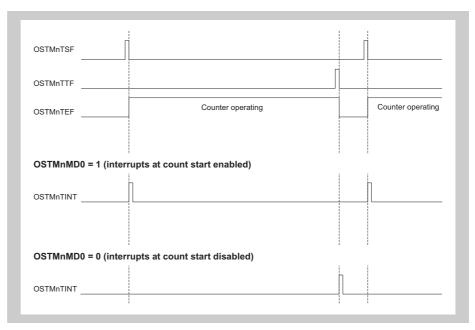

|         | 12.3.1           | Interrupt request generation                                |     |

|         | 12.3.3           | Starting and stopping the timer                             |     |

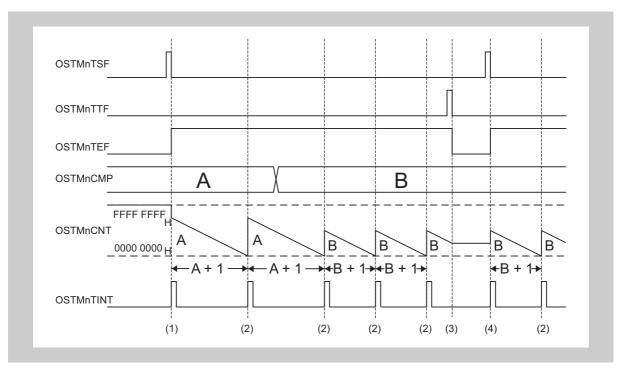

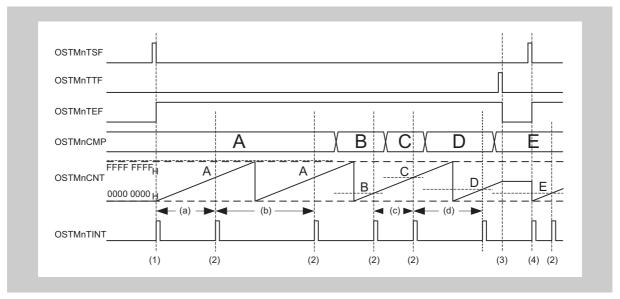

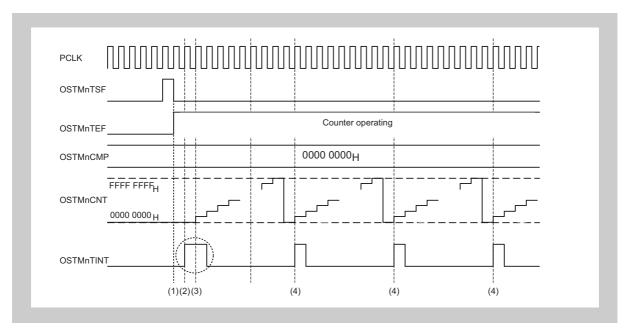

|         | 12.3.4           | Interval timer mode                                         |     |

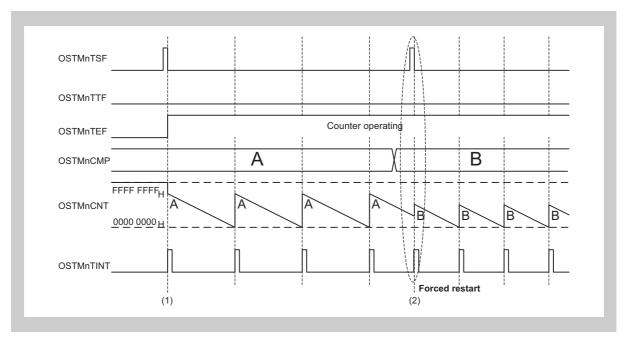

|         | 12.3.5           | Free-run compare mode                                       |     |

| 12.4    | OS Ti            | mer Registers                                               |     |

|         | 12.4.1           | OS Timer registers overview                                 |     |

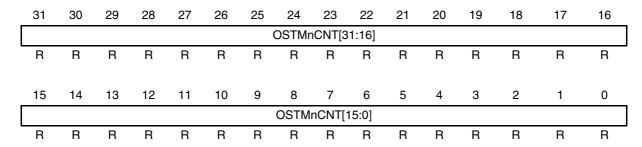

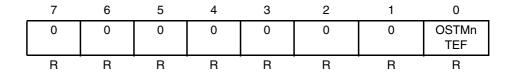

|         | 12.4.2           | OS Timer registers details                                  |     |

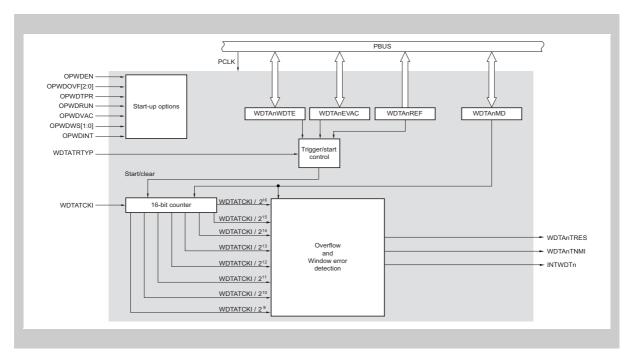

| Chapter | 13               | Window Watchdog Timer A (WDTA)                              | 464 |

| 13.1    |                  | 2/Fx4-L WDTA Features                                       |     |

|         |                  |                                                             |     |

| 13.2    |                  | Start-up Options                                            |     |

| 10.0    | 13.2.1           |                                                             |     |

| 13.3    |                  | ional Overview                                              |     |

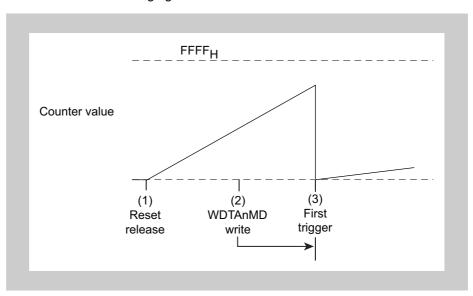

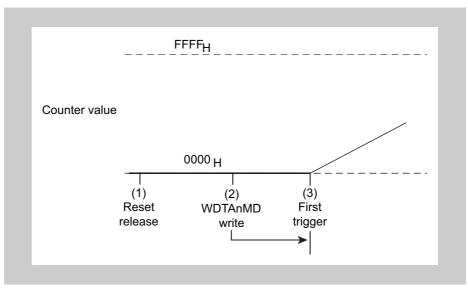

| 13.4    |                  | ional Description                                           |     |

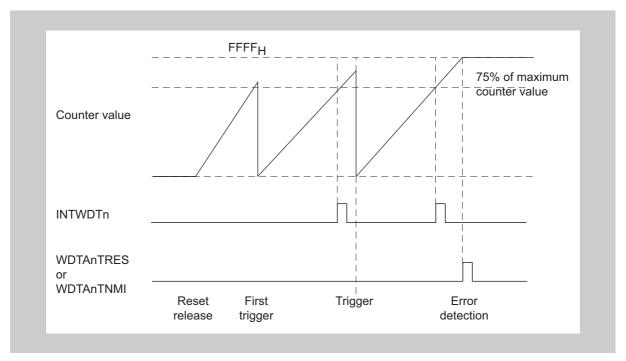

|         | 13.4.1<br>13.4.2 | WDTA after reset release                                    |     |

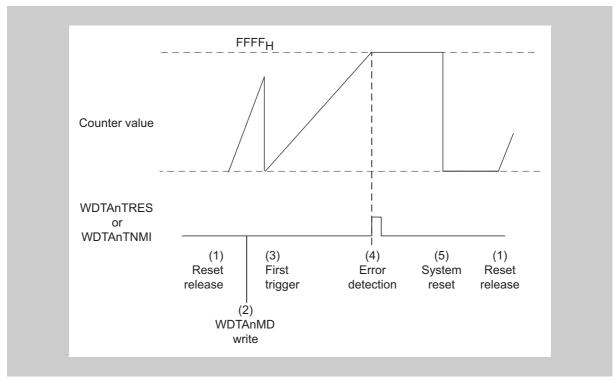

|         | 13.4.2           | Error detection.                                            |     |

|         | 13.4.4           | 75% interrupt output                                        |     |

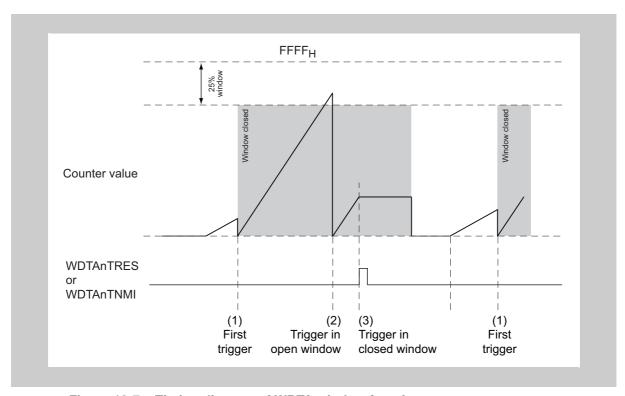

|         | 13.4.5           | Window function                                             |     |

| 13.5    |                  | cation hint: Evaluation of the Watchdog status              |     |

| 13.6    | • •              | registers                                                   |     |

| 10.0    |                  | WDTA registers overview                                     |     |

|         |                  | WDTA registers details                                      |     |

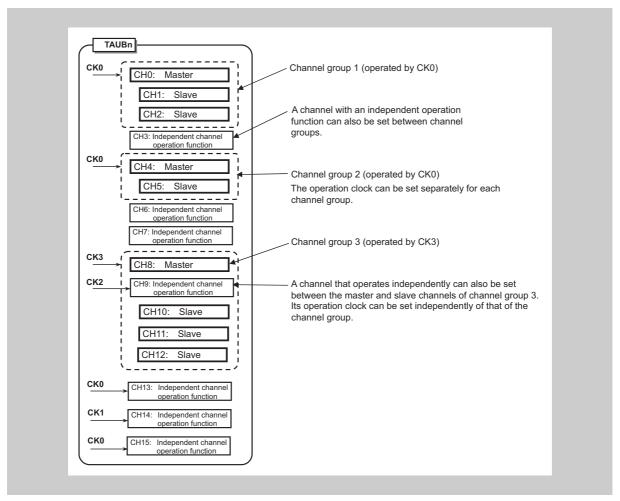

| Chapter | r 14             | Timer Array Unit B (TAUB)                                   | 487 |

| 14.1    |                  | 2/Fx4-L TAUB Features                                       |     |

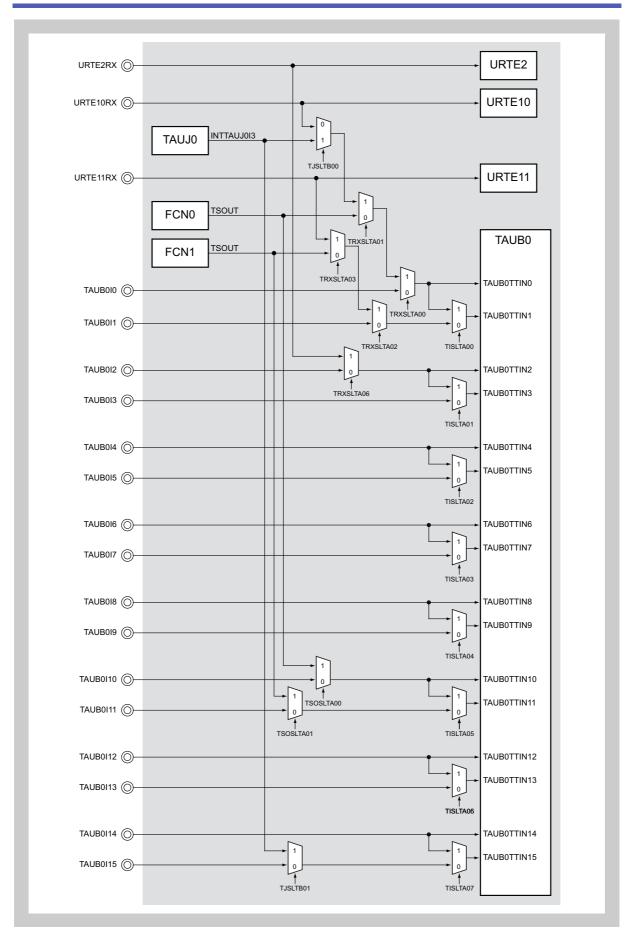

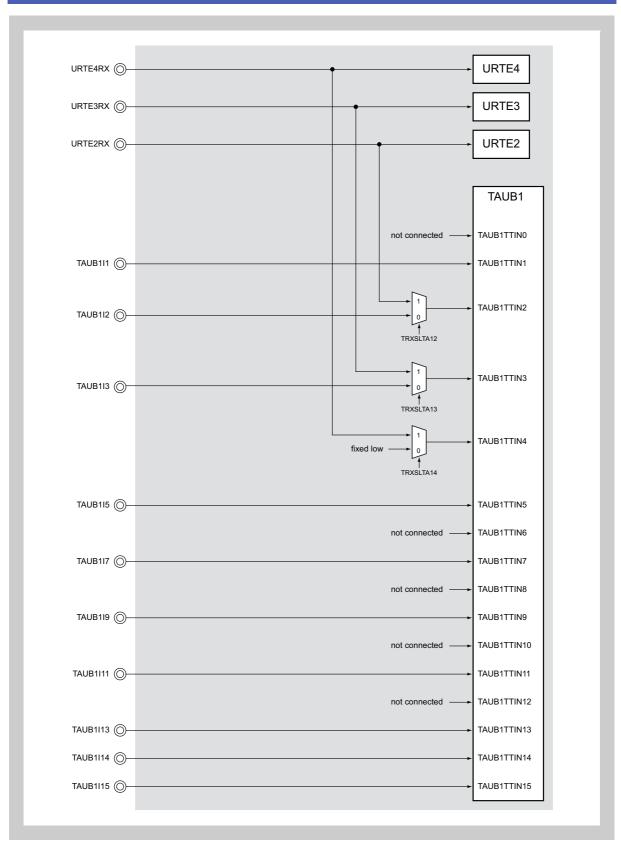

| 14.2    |                  | Input Selections.                                           |     |

|         | 14.2.1           | TAUB0 input selection                                       |     |

|         | 14.2.2           | TAUB1 input selection                                       |     |

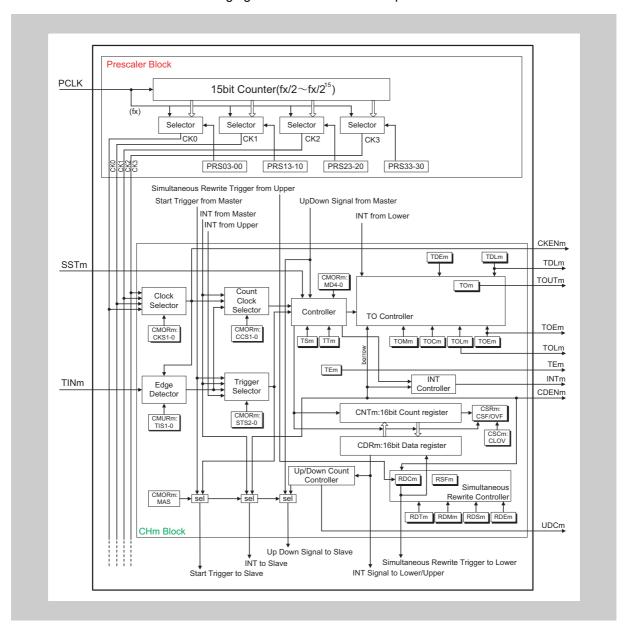

| 14.3    | Funct            | ional Overview                                              |     |

|         | 14.3.1           | Terms                                                       |     |

| 14.4    | Funct            | ional Description                                           | 506 |

| 14.5    |                  | al Operating Procedure                                      |     |

| 14.6    |                  | ition Modes                                                 |     |

| 14.7    | -                | epts of Synchronous Channel Operation                       |     |

|         | 14.7.1           | Rules                                                       |     |

|         | 14.7.2           | Simultaneous start and stop of synchronous channel counters |     |

| 14.8    | Simul            | taneous Rewrite                                             |     |

| -       | 14.8.1           | Introduction                                                |     |

|       | 14.8.2  | How to control simultaneous rewrite                                | 515 |

|-------|---------|--------------------------------------------------------------------|-----|

|       | 14.8.3  | Other general rules of simultaneous rewrite                        | 516 |

|       | 14.8.4  | Types of simultaneous rewrite                                      | 517 |

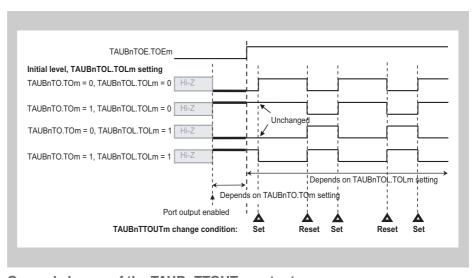

| 14.9  | Chann   | nel Output Modes                                                   | 523 |

|       | 14.9.1  | General procedure for specifying a channel output mode             |     |

|       | 14.9.2  | Channel output modes controlled independently by TAUBn signals     |     |

|       | 14.9.3  | Channel output modes controlled synchronously by TAUBn signals     |     |

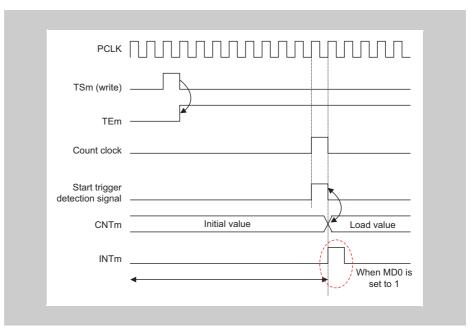

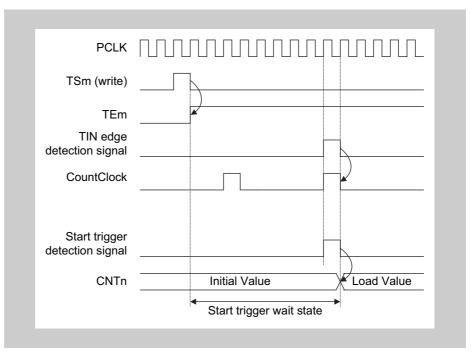

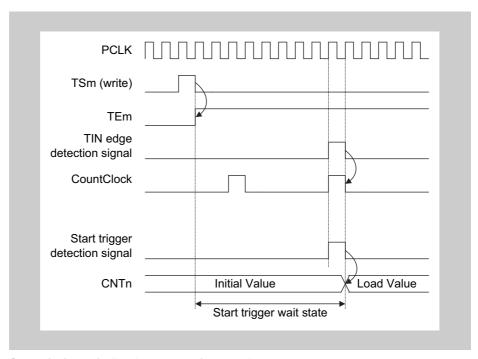

| 14.10 | Start 1 | Timing of Operating Modes                                          | 530 |

|       |         | Interval Timer Mode, Judge Mode, Capture Mode, Up Down Count Mode. |     |

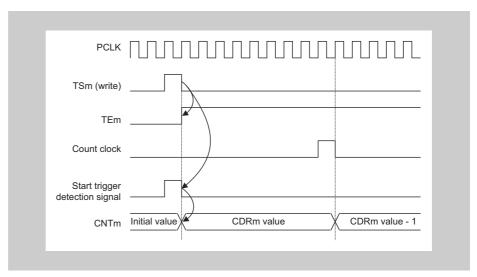

|       |         | Event Mode                                                         |     |

|       |         | All other operating modes                                          |     |

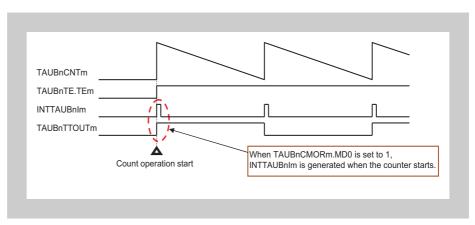

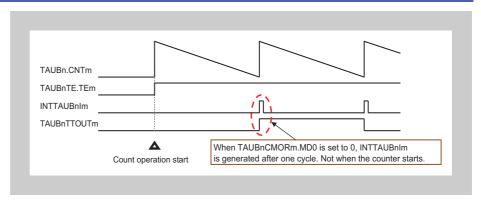

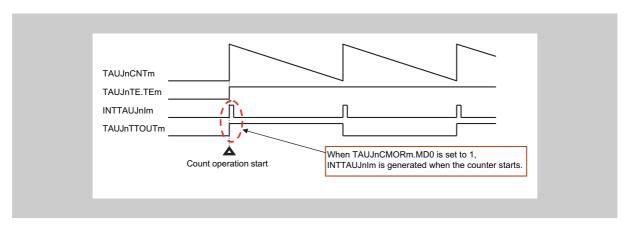

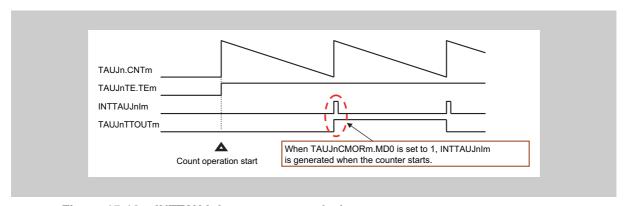

| 14.11 | TAUBr   | nTTOUTm toggle and INTTAUBnIm Generation when Count                | er  |

|       |         | s triggered (MD0-bit)                                              |     |

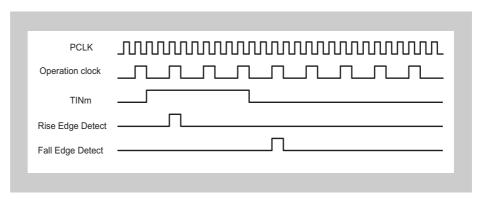

| 14.12 |         | nTTINm Edge Detection                                              |     |

| 14.13 | -       | endent Channel Operation Functions                                 |     |

| 14.14 | •       | endent Channel Interrupt Functions                                 |     |

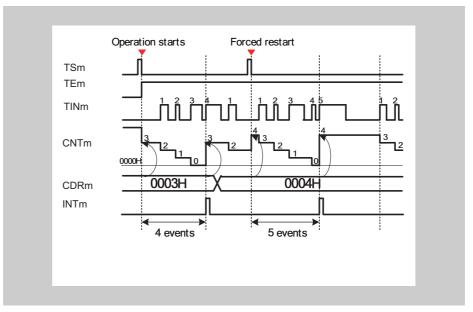

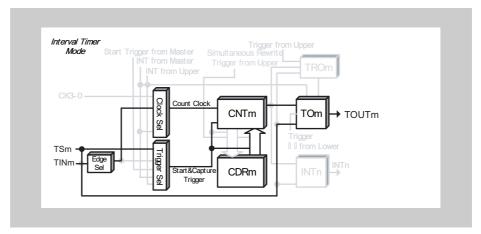

|       |         | Interval Timer Function                                            |     |

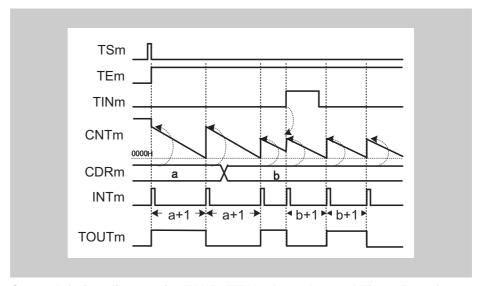

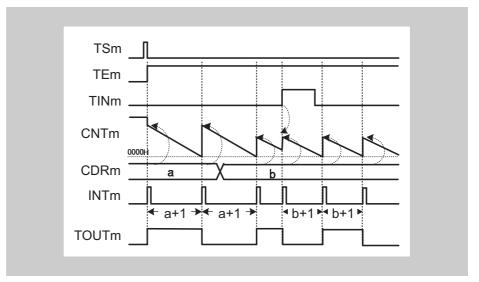

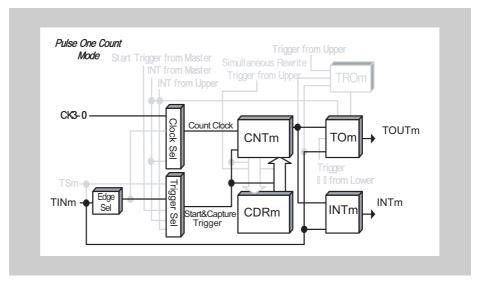

|       |         | TAUBnTTINm Input Interval Timer Function                           |     |

|       |         | One-Pulse Output Function.                                         |     |

| 14.15 | -       | endent Channel Signal Measurement Functions                        |     |

|       |         | TAUBnTTINm Input Pulse Interval Measurement Function               |     |

|       |         | TAUBnTTINm Input Signal Width Measurement Function                 | 564 |

|       | 14.15.3 | Overflow Interrupt Output Function                                 |     |

|       | 1/15/   | (During TAUBnTTINm Width Measurement)                              |     |

|       |         | Overflow Interrupt Output Function                                 | 5// |

|       | 14.15.5 | (During TAUBnTTINm Input Period Count Detection)                   | 583 |

|       | 14.15.6 | TAUBnTTINm Input Pulse Interval Judgment Function                  |     |

|       |         | TAUBnTTINm Input Signal Width Judgment Function                    |     |

| 14.16 |         | endent Channel Simultaneous Rewrite Functions                      |     |

|       | -       | Simultaneous Rewrite Trigger Generation Function Type 1            |     |

| 14.17 |         | Independent Channel Functions                                      |     |

|       |         | External Event Count Function                                      |     |

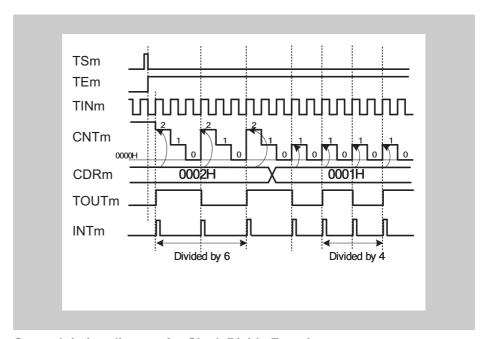

|       |         | Clock Divide Function                                              |     |

|       | 14.17.3 | TAUBnTTINm Input Position Detection Function                       | 620 |

| 14.18 | Synch   | ronous Channel Operation Functions                                 | 626 |

| 14.19 | Synch   | ronous PWM Signal Functions Triggered at Regular Interven          | als |

|       | 626     |                                                                    |     |

|       | 14.19.1 | PWM Output Function                                                | 627 |

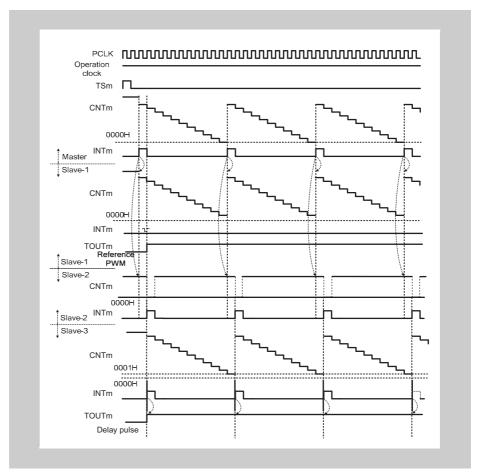

|       | 14.19.2 | Delay Pulse Output Function                                        | 638 |

|       | 14.19.3 | AD Conversion Trigger Output Function Type 1                       | 654 |

| 14.20 | Synch   | ronous PWM Signal Functions Triggered by an External Sig           | ına |

|       | 656     |                                                                    |     |

|       | 14.20.1 | One-Shot Pulse Output Function                                     | 657 |

| 14.21 | Synch   | ronous Triangle PWM Functions                                      | 669 |

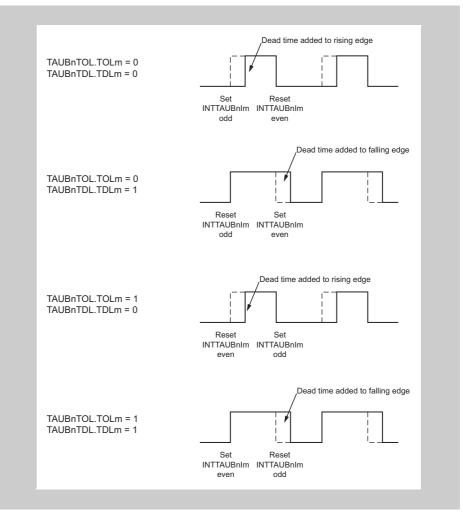

|       | -       | Triangle PWM Output Function                                       |     |

|       |         | Triangle PWM Output Function with Dead Time                        |     |

|       |         | AD Conversion Trigger Output Function Type 2                       |     |

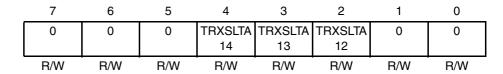

| 14.22   | Regist  | ters                                                             | 706     |

|---------|---------|------------------------------------------------------------------|---------|

|         | 14.22.1 | TAUBn registers overview                                         | 706     |

|         | 14.22.2 | TAUBn prescaler registers details                                | 707     |

|         | 14.22.3 | TAUBn control registers details                                  | 709     |

|         |         | TAUBn output registers details                                   |         |

|         |         | TAUBn channel output level registers details                     |         |

|         |         | TAUBn simultaneous rewrite register details                      |         |

|         | 14.22.7 | TAUBn emulation register                                         | 726     |

| Chapter | r 15    | Timer Array Unit J (TAUJ)                                        | 727     |

| 15.1    | V850E   | 2/Fx4-L TAUJ Features                                            | 727     |

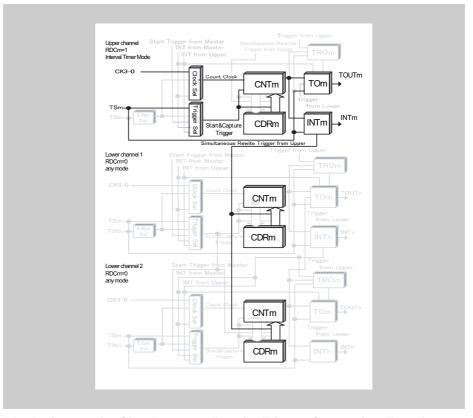

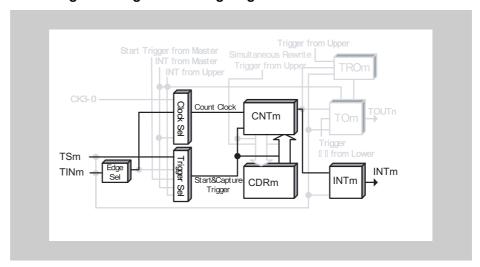

| 15.2    | Functi  | onal Overview                                                    | 730     |

|         | 15.2.1  | Terms                                                            |         |

| 15.3    | Functi  | onal Description                                                 |         |

| 15.4    |         | al Operating Procedure                                           |         |

| 15.5    |         | tion Modes                                                       |         |

| 15.6    | •       | epts of Synchronous Channel Operation                            |         |

| 13.0    | 15.6.1  | Rules                                                            |         |

|         | 15.6.2  | Simultaneous start and stop of synchronous channel counters      |         |

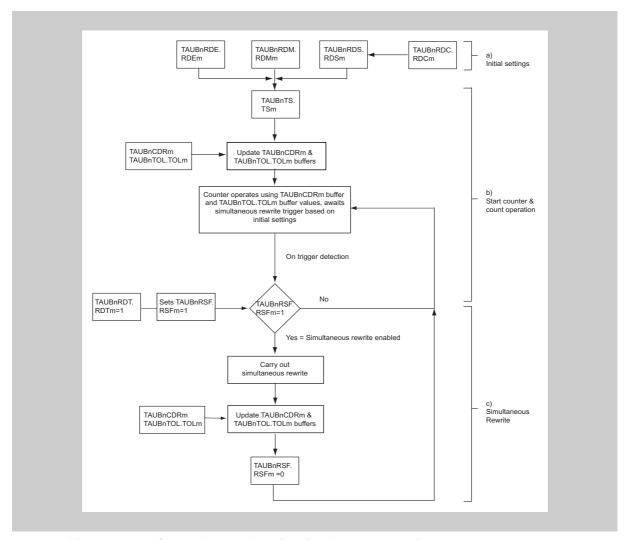

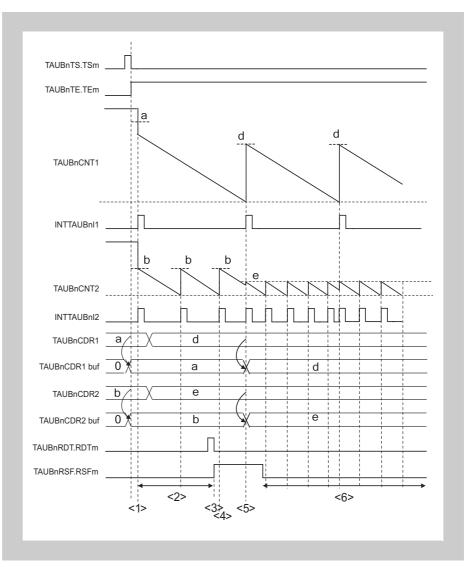

| 15.7    |         | aneous Rewrite                                                   |         |

| 10.7    | 15.7.1  | Introduction                                                     |         |

|         | 15.7.2  | How to control simultaneous rewrite                              |         |

|         | 15.7.3  | Other general rules of simultaneous rewrite                      |         |

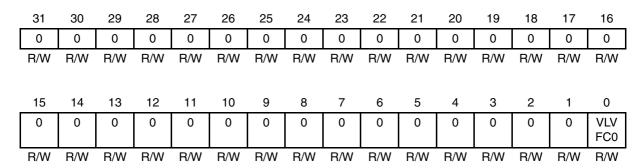

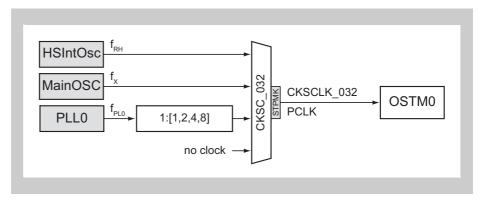

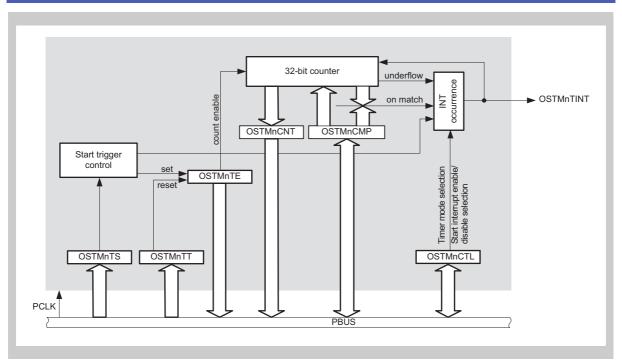

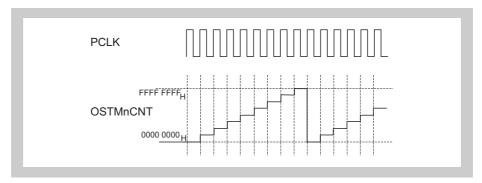

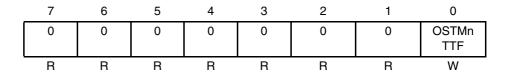

|         | 15.7.4  | Simultaneous rewrite procedure                                   |         |